基于CPCI总线的雷达数据传输接口设计*

魏巍,王勤,陈少平

(1.中南民族大学智能无线通信湖北省重点实验室,湖北武汉430074)2.中南民族大学电子信息工程学院,湖北武汉430074)

近年来,随着信息技术的不断发展,通信、网络、雷达、遥测遥感等诸多领域都面临着数据量日趋庞大的问题,这对数据传输技术也提出了更高的要求。尤其在雷达领域,雷达新体制新技术的提出与应用,如数字波束形成技术、高速A/D转换器件的应用等等,使得雷达系统所需处理的信号通道数越来越多,数据率也越来越大,庞大数据量的实时传输逐渐成为制约雷达系统性能的瓶颈之一。当前,高速数据传输技术已经成为了人们研究的热点问题。

CPCI(Compact PCI)总线是国际工业计算机制造者联合会PICMG(PCI Industrial Computer Manufacturer’s Group)提出的一种高性能工业总线接口标准[1]。与传统的工业计算机总线相比,CPCI总线具备以下几个优点:(1)传输速率高。从总线速度上看,32 bit/33 MHz的CPCI总线最大传输速度为132 MB/s;对于64 bit/66 MHz CPCI总线则峰值速度可达528 MB/s。(2)与PCI总线标准完全兼容,有利于用户将基于PCI总线开发的成熟技术与产品向工业设备上推广。(3)采用欧插机械结构标准,具备良好的耐用性、散热性、抗震性和易维护性等性能,适合工控、军事、电信等恶劣工作环境的使用。此外其还具有高扩展、支持热插拔等性能。CPCI总线的种种特性使得该技术在雷达、通信、控制等领域都得到了广泛应用[2-4]。

本文以CPCI总线接口设计作为研究对象,针对某雷达系统数据传输与控制的需求,完成了雷达接收机数据传输接口的设计与开发,为雷达系统各板卡间的正常通信提供了保障。

1 系统需求

该雷达系统的结构框图如图1所示,系统涵盖主控板卡,数据采集板卡、同步控制板卡和频率合成板卡等多种不同类型的外围板卡。其中主控板卡负责收集多块数据采集板卡的数据进行后续信号处理,以及完成对所有外围板卡的参数配置与控制。主控板与外围板卡的通信通过数据总线来完成。经过分析,得知多块数据采集板卡向主控板上传数据的最大传输速率和不超过10 MB/s,而主控板下发控制参数信息至外围板卡的传输速率则要求更低。因此CPCI总线的传输速率足以胜任系统需求。

图1 雷达系统框图

该雷达系统的主控板卡为外购产品,因此设计的重点在于外围板卡端的数据总线接口设计以及主控板卡端的驱动开发。此外对于雷达外围板卡端而言,虽然可分为多块不同类型的板卡,功能不同,但其CPCI总线接口电路的设计应基本一致,保证版本的统一性,方便调试与维护。

2 硬件设计

目前常见的CPCI总线接口实现方案有多种:(1)FPGA IPcore方案,可用各大FPGA公司提供的PCI总线接口IP核来完成。该方案结构简单,无需关心PCI总线协议,但需要购买使用许可,费用较高。(2)在FPGA内自己实现PCI协议及相应逻辑功能[5],该方案电路设计简单,费用较低,但开发难度较高,研发周期过长。(3)PCI桥芯片+FPGA架构方案[2-3,6],该方案电路结构较前两者相对复杂一些,但因使用了桥芯片,无需太多关心PCI总线协议,研发周期快,且费用较低。综合以上因素,选取了第三种方案搭建硬件接口电路,其结构框图如图2所示。

图2 硬件结构框图

其中PCI桥芯片完成CPCI总线与本地端总线的协议转换,在这里选择了PLX Technology公司32 bit宽/33 MHz低成本PCI桥芯片PCI9054。FPGA主要负责数据的缓冲与转发,并对PCI9054进行相应的控制操作。当外围板卡即本地端用户功能设备上传数据时,FPGA通过内部开设的缓冲区,将用户端的数据进行打包发送给PCI9054,由PCI芯片转换成CPCI总线协议数据上传至主控板卡端。当主控端发送控制指令时,FPGA同样在获得PCI芯片的本地总线数据后,发送至本地端用户功能设备中。此外EEPOM与FPGA配置芯片分别完成上电时对PCI芯片以及FPGA的参数配置与初始化。

PCI9054负责完成主控板与外围板端FPGA之间的通信,其主要控制步骤如下:

(1)主控板向外围板发出读写请求时,PCI9054向FPGA发出申请本地总线信号LHOLD(高有效)。

(2)FPGA检测到LHOLD有效后,若本地总线空闲,即对PCI9054回应总线应答信号LHOLDA(高有效),表示申请本地总线有效。

(3)PCI9054检测到申请总线有效后,给出地址有效信号ADS(低有效),同时给出读写的地址。

(4)FPGA检测到ADS后,根据PCI9054的读写控制信号LW/R(高为读,低为写),进行读写数据操作;并同时向PCI9054发送数据有效信号READY(低有效)。此时PCI桥芯片根据读写要求,将数据发送至FPGA或上传至主控板。

(5)当传输最后一个数据时,PCI9054将BLAST指示信号置低(低有效)。FPGA随即在下一个时钟将READY信号拉高表示传输结束。

(6)当PCI9054检测到READY为高电平时放弃本地总线,结束通信。

在主控板卡与外围板卡的数据传输过程中,FPGA开设有双口RAM作为数据缓冲区,本地端功能设备和PCI芯片均可对其进行读写操作。设计采用乒乓操作工作模式,避免两者对同一地址同时读写的冲突。此外在硬件电路设计中,针对该雷达不同类型的外围板卡所需缓冲数据块大小的需求不尽相同的情况,通过选用同系列、同封装、不同资源的FPGA芯片,统一考虑它们的电源、地以及I/O管脚的分布情况,综合设计电路版图,使得同一块PCB板上可以根据不同需求焊接合适资源的FPGA芯片。该设计既有效降低了成本,又便于以后的维护与升级。

3 驱动开发

3.1 WDM驱动简介

雷达系统的主控板卡采用Windows XP操作系统。在该操作系统平台上,应用程序直接访问硬件设备是受限制的,必须获得可工作在Windows系统内核下的驱动程序的支持。综合考虑选用WDM驱动框架模式,完成了CPCI总线数据接口的驱动开发。WDM模型驱动是微软公司为Windows系统下的设备驱动程序开发提供的一种灵活、简化的驱动模型,能有效降低所必需开发的驱动程序的数量以及复杂性[7]。

在WDM驱动下访问硬件设备时,应用程序通过调用Win32API函数产生控制命令,操作系统的I/O管理器将获取的控制命令转化为对应的IRP(I/O处理请求包)送给驱动程序的入口点。IRP是Windows内核中一种非常重要的数据结构,它包含了应用程序发出控制命令的信息,不同的IRP会根据类型被分到驱动的不同例程中进行处理[8]。随后驱动程序通过硬件抽象层(HAL)调用来访问硬件设备。当IRP结束时,驱动调用IoCompleteRequest函数通知I/O管理器,并向I/O管理器返回相关参数及数据,应用程序回读数据,完成本次操作。图3为应用程序通过调用WDM驱动程序与底层硬件进行通信的整个过程(灰色部分为论文需设计研发的工作)。

图3 软件工作示意图

3.2 WDM驱动功能实现

论文利用Driver Studio工具,调用其自带的Driver wizard设置向导生成WDM驱动框架[9],并根据雷达系统的硬件设备情况添加相应的代码。驱动实现的功能主要包括三个部分:硬件访问、中断处理与DMA传输。

3.2.1 硬件访问

硬件访问是指对硬件设备实现基本的识别与访问功能。WDM驱动可以通过GUID接口方式或符号链接名方式来获取有效的设备句柄,从而识别、打开或关闭设备。在前者方案中,每块板卡需要生成对应不同GUID标识符的驱动,打开设备比较繁琐;对于后者,所有板卡通用一个驱动程序,只根据板卡在不同的插槽位置对应不同的符号链接名打开设备。相比较而言获取设备句柄更为简单。论文采用符号链接名方式实现设备的识别。

对于硬件的访问,在X86处理器中存在两套独立的地址空间:内存地址和I/O地址。PCI桥芯片将本地端内存单元通过映射的方式定位到这两种独立的地址空间。在驱动程序中,可通过调用WDM驱动框架提供的KIoRange类(对I/O映射空间的访问)和KMemoryRange类(对内存映射空间的访问)来实现对映射的访问。

本文通过调用KIoRange类对I/O映射空间访问,实现对硬件的操作。打开设备后,应用程序可通过Win32的API函数DeviceIoControl向驱动发起相应的控制命令和参数。驱动获取命令及参数后通过KIoRange类的成员函数FORM.outd(ULONG ByteOffset,ULONG Data)对寄存器进行操作。例如配置PCI9054的中断寄存器:

m_IoPortRange0.outd(INTCSR,mm_Data);INTCSR为定义的中断寄存器,mm_Data为获得的需要修改的中断寄存器参数。

3.2.2 中断处理

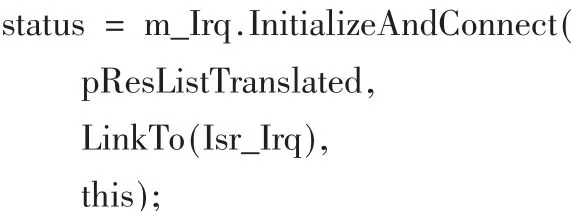

系统主要存在两类中断需要处理:(1)数据采集板卡请求数据上传时所生成的本地中断;(2)PCI9054完成了DMA传输后产生的DMA中断。WDM框架驱动将中断的处理封装成类KInterrupt。进入中断服务例程前,通过调用KInterrupt的成员函数InitializeAndConnect初始化中断变量和调用宏LinkTo链接到中断例程(Isr_Irq)中。代码如下:

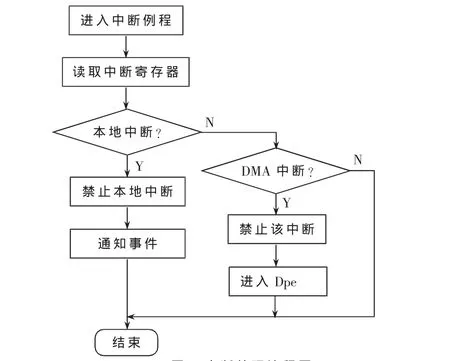

进入中断服务例程后,通过PCI9054的中断寄存器进行中断类型判断:若为本地中断,则关闭本地中断清除中断标志位,产生通知事件给应用程序,通知主控板卡需进行数据的DMA传输;如为DMA中断,则表明DMA传输完成,需禁止该中断并清除中断标志位,随后启动延迟过程调用例程(DPC)进行处理。其过程将在下节进一步说明。中断处理的流程图如图4所示。

图4 中断处理流程图

该雷达系统存在多块外围板卡同时挂在CPCI总线上的情况,它们共享一个中断向量。面对多外围板卡的中断处理时,驱动程序通过查询各个设备的中断寄存器状态,判断来自哪个设备的中断,并以事件形式通知应用程序,迅速对中断事件进行处理。

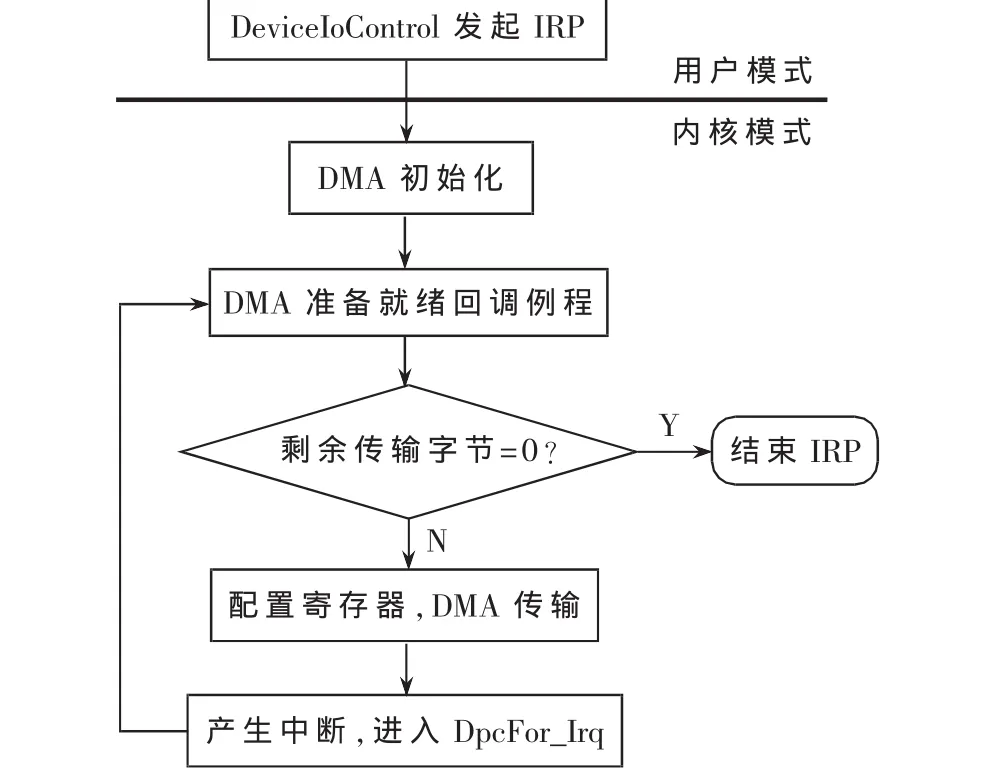

3.2.3 DMA传输

雷达系统数据采集板卡上传采集数据或主控板卡下发控制参数均可由DMA传输方式完成的,它们的工作原理基本相同。以上传为例,数据采集板卡在本地端FPGA内缓冲一定量的数据后,向主控板卡申请中断。主控板接收到该中断后发起总线操作,控制外围板卡进行DMA传输,DMA传输流程图如图5所示。

图5 DMA传输流程

进入DMA传输流程时,驱动程序通过控制DMA传输的KDmaTransfer类的成员函数Initiate()完成DMA的初始化工作。随后系统进入回调例程,若有数据需要传输,则配置PCI9054的DMA寄存器,并开始DMA传输。当传输完成后,PCI9054产生DMA中断,在驱动程序的中断服务例程中,启动DPC进入DpcFor_Irq例程,在DpcFor_Irq内通过调用KdmaTransfer类的成员函数Continue()进入DMA的回调例程,再次检测是否有待传输的数据。若所有数据传输完毕则完成DMA操作,结束IRP;否则进入下一轮DMA,一直到数据传输完毕为止。

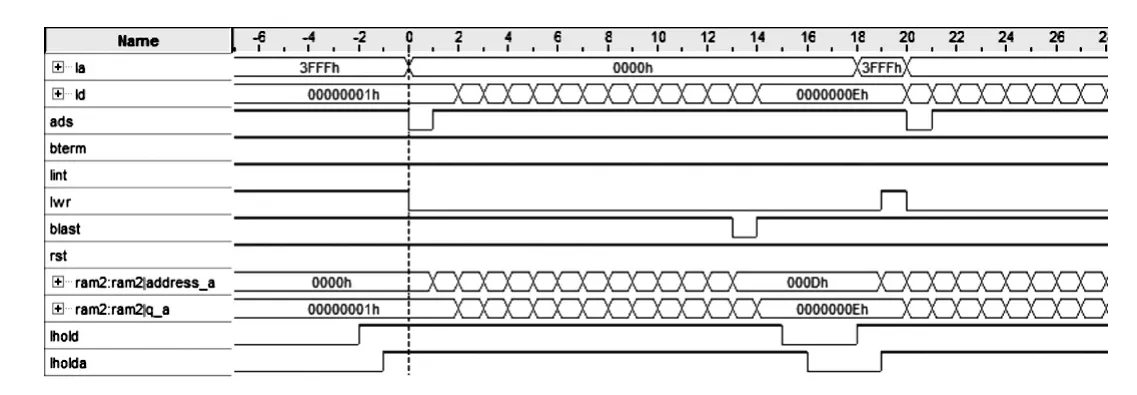

本文对安装有WDM框架驱动的板卡进行了测试。图6为外围板卡端FPGA抓取DMA传输的本地总线时序图,表明主控板卡与外围板卡的DMA传输工作正常。实验测试实际DMA传输速率约为35 MB/s,完全能够满足该雷达系统数据传输的需求。

图6 DMA操作时序图

本文针对某雷达系统数据传输与控制的要求,提出了一种基于CPCI总线的雷达接收机数据传输接口实现方案。在外围板卡端,完成了基于FPGA+PCI桥芯片架构的CPCI总线接口电路设计;在主控板卡端,进行了基于WDM框架的驱动程序开发,实现了主控板对多块外围板的硬件访问、中断处理和DMA传输等多种功能。论文的测试结果表明主控板卡能够有效完成与外围板卡间的数据传输与控制,性能指标符合系统设计要求。

[1]Wikipedia,Compact PCI[EB/OL].[2014-01-02].http://en.Wikipedia.org/wiki/CompactPCI,2013.

[2]熊杰,潘小锋,庄屹立,等.基于CPCI总线的认知无线电系统设计[J].计算机测量与控制,2012,20(3):754-757.

[3]董勇伟,周良将,唐波,等.SAR实时成像处理平台的设计与实现[J].系统工程与电子技术,2009,31(8):1882-1886.

[4]何莉,龚宗洋,张为公,等.基于CPCI总线的运动控制卡及其VxWorks下的驱动设计[J].测控技术,2008,27(8):50-52.

[5]方明.基于FPGA开发的CPCI总线多功能卡及WDM驱动程序设计与实现[D].上海:上海交通大学,2009.

[6]段玲琳,段晓超,叶明傲.CPCI外设板卡通用设计方法[C].计算机技术与应用学术会议,2009.

[7]张帆,史彩成.Windows驱动开发技术详解[M].北京:电子工业出版社,2008.

[8]武安河.Windows2000/XP WDM设备驱动程序开发(第二版)[M].北京:电子工业出版社,2005.

[9]李勇,李宇.PCI总线设备开发宝典[M].北京:北京航空航天大学出版社,2005.