基于NiosⅡ的超声相控阵数据采集系统

刘书文,骆 英

(江苏大学,机械工业结构损伤检测评估技术重点实验室,江苏镇江 212013)

0 引言

超声相控阵是指按照一定的规则和时序激发阵列换能器的各个阵元发射超声波束,通过调整激发阵元的顺序、数量、时间改变声束的形状、偏转角度及焦点位置等参数,来实现对物体的扫查[1]。该技术采用多声束扫描成像,支持动态聚焦,可在不移动探头的情况下,对复杂形状物体检测,提高了声束可达性和控制的灵活性、信噪比以及检测速度。超声相控阵成像通过对工件内部结构扫描成像,可以准确地反映缺陷的位置和大小[2];而高质量成像技术的实现必须依赖于高速的数据采集技术。

现有的超声相控阵数据采集系统,多以微处理器(单片机、ARM或DSP)为主控制器,或以微处理器与FPGA/CPLD相结合的方式;对于这种硬CPU+FPGA方案,一方面,设计者要在微处理器的选型或在微处理器与FPGA/CPLD相互匹配的过程中花费大量的时间;另一方面,当系统的设计方案改变时,需要另选器件,重新设计PCB板。Nios Ⅱ是一种基于FPGA开发的软核CPU;相对于常见的硬核CPU,Nios Ⅱ的成本更低、灵活性更高、实现更简易,性能超过150DMIPS,而且开发更快速[3]。软核CPU的出现是嵌入式系统的重大进步,在一片FPGA内可以嵌入一个或多个软核处理器,软核处理器的性能可以根据需要来定制;软核CPU和一些外设都可以在FPGA内实现,传统的CPU总线就从PCB上转移到FPGA内部;系统的调试过程几乎可以集中到FPGA内部[4]。

文中设计了一种相控阵超声检测的数据采集系统,采用内嵌Nios Ⅱ软核处理器的FPGA系统作为主处理器,通过在FPGA芯片内部构建以Nios Ⅱ为核心的片上可编程系统(SOPC),实现对数据采集的控制以及采样数据预处理。

1 系统总体设计方案

系统中以8通道的超声相控阵系统为研究对象,数据采集系统结构框图如图1所示,系统主要有OPCM阵列换能器、模拟信号调理模块、模数转换器(ADC)、数据缓存模块(SRAM)、以FPGA为核心的逻辑控制模块等及部分组成。模拟信号调理模块主要由前置放大器、滤波电路、主放大器3部分组成,完成信号调理功能。数字电路部分包括模数转换器(ADC)、数据缓存(SRAM)以及片上控制系统(以Nios Ⅱ为核心的SOPC),实现各通道回波信号的采集、存储、预处理,最后将数据上传到上位机。

图1 超声相控阵数据采集系统结构框图

图2 系统工作流程图

数据采集系统工作流程(如图2所示)可以分为数据采集和数据处理2个阶段。

在数据采集阶段:关闭三态门使各通道的SRAM与数据总线隔离;系统启动ADC开始数据转换,并将采样数据存入SRAM;数据采集过程要求控制器有较高的运行速度并且操作时序单一,适合用并行的硬件电路来控制。因此,在SOPC中增加了数据采集模块,由该模块完成数据采集的时序控制。

数据处理阶段:在数据采集结束后,逐一选通每一个相控阵接收通道的三态门,将该通道的SRAM的数据端口连接到数据总线上,并将该通道SRAM中的采样数据读入Nios Ⅱ微处理器的波形数组。而在此过程中,需要切换各个接收通道的三态门和分时操作SRAM,操作时序复杂并且对执行速度的要求不是很高,适合用Nios Ⅱ微处理器来控制,发挥了软件操作灵活的特点。Nios Ⅱ软核控制SRAM进行数据读取操作,该过程通过C语言编程实现时序控制。在Nios Ⅱ微处理器上运行的C语言,设置了8个波形数组,用于缓存8个SRAM中的采样数据,以便于作进一步的处理。当各通道SRAM的全部读入Nios Ⅱ微处理器的波形数组后,进行延时处理使个通道的回波信号同相位,再将各路回波信号加权求和后,合成波形数据。最后将合成波形送入串口控制模块的数据缓存,并由串口控制模块发送到PC机。

2 系统硬件电路的设计

在超声检测中超声波的频率越高,检测精度越高;但是频率越高,衰减也越大,超声波的穿透性能受到影响。该系统主要检测混凝土兼顾金属。综合考虑检测精度和超声衰减的问题,选用频带200 kHz~2 MHz的超声波,其中200~300 kHz的频段主要用来检测混凝土。

由阵列换能器接收的超声信号经过阻抗变换、滤波和放大处理后,送入模数转换电路。阻抗变换、滤波和放大器的设计文中从略。模数转换电路是数据采集系统的重要组成部分,将接收的模拟信号转换为数字信号,随后进行信号的进一步处理。为了较好地保持回波信号的波形,系统采用不少于10倍的采样率;ADC采用AD9235-40,12位分辨率,采样率40 MHz,满足设计要求[5]。为了抑制噪声,AD9235输入端为差分式采样保持电路;AD9235是基于CMOS开关电容型ADC,具有低成本和低功耗的优点;此类ADC的前端为非缓冲型,直接耦合至采样网络,输入阻抗会随时间(采样和保持模式切换时)变化,需要阻抗匹配电路[6-7]。因此,采用专用的差分ADC驱动芯片AD8138,将单端信号转换为差分信号,送入AD9235;同时,实现了AD9235输入阻抗匹配功能。模数转换电路如图3所示。

图3 模数转换电路

3 以Nios Ⅱ为核心的SOPC设计

系统以EP1S10 FPGA开发板为开发平台,通过在FPGA芯片内部构建Nios Ⅱ软核为核心的可编程片上系统(SOPC)来实现对数据采集的控制和数据的预处理。SOPC的设计是以IP为基础,以硬件描述语言为主要设计手段,借助计算机为平台的EDA工具(SOPC Builder),自动化、智能化地自顶向下进行的过程。基于Nios Ⅱ的SOPC的设计过程包括硬件设计和软件设计两个流程;其中SOPC的硬件包括数据采集模块、Nios Ⅱ处理器和串口模块。

3.1数据采集模块的设计

图4 数据采集模块示意图

图5 数据采集模块时序仿真图

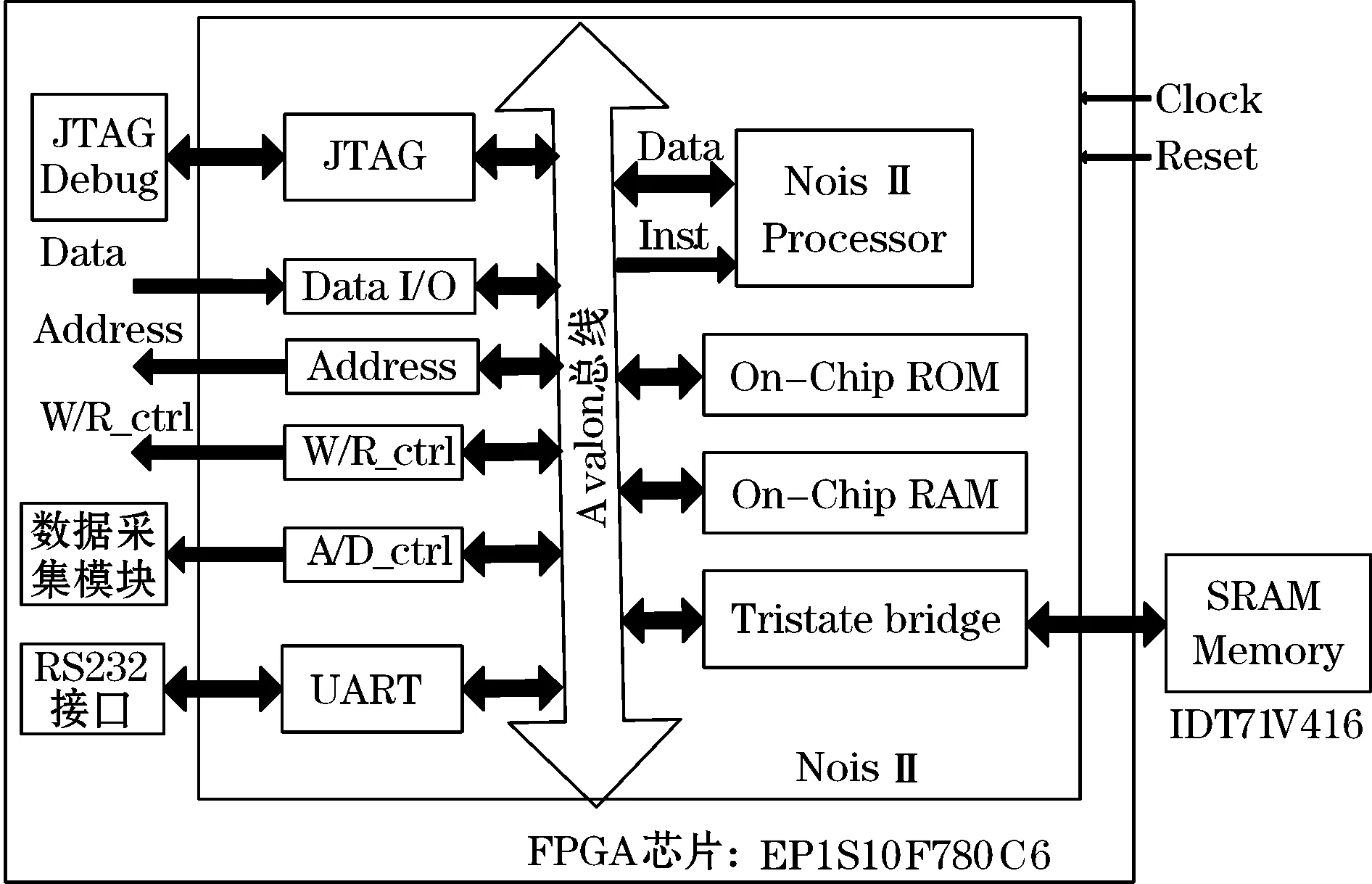

3.2NiosⅡ处理器的定制

图6 Nios Ⅱ处理器框图

Nios Ⅱ硬件设计,即定制Nios II CPU和外设,并在SOPC Builder和Quartus II中实现的过程。系统中的Nios Ⅱ处理器的组成模块如图6所示;其中,Nios ⅡProcessor为Nios Ⅱ的核心,一种通用的32位RISC软核CPU;Avalon总线是一种相对简单的总线结构,主要用于连接片内处理器与外设,以构成SOPC[8];片内存储器,包括RAM和ROM,用作CPU的高速缓存;片外存储器,用作大容量的系统内存,由2片IDT71V416组成;并行输入/输出PIO是Nios Ⅱ处理器与数据采集电路通信接口。在SOPC Builder中配置好的SOPC硬件如图7所示。

图7 SOPC的硬件配置

SOPC的硬件配置如图4所示。其中主要数据端口有:PIO端口SRWR[2:0]用于数据缓存(0#~7#SRAM)的读写控制,3位数据分别为SRAM的片选、写使能、读使能;DUPD用于ADC的使能控制,低电平有效;BA[14:0]为SRAM的15位地址线;DBI[11:0]为12为数据线,用于传输12位字长的回波信号;ESA,EA[2:0]用于控制各通道SRAM与数据总线的选通;当ESA=1时,所有的的三态门呈高阻态,各通道的SRAM与数据总线断开;当ESA=0时,EA[2:0]=0~7分别选通0#~7#三态门,即将0#~7#SRAM与数据总线连通。

3.3系统软件的设计

数据采集中SRAM的读写过程由Verilog语言编写的数据采集模块控制;SRAM中数据的读出过程、各通道数据的合成(加权求和)以及整个信号接收的过程则由Nios Ⅱ软核中运行的C语言程序实现。根据图5的系统工作流程,可以编制出系统控制软件。

4 系统测试

4.1ADC转换精度测试

图8 测试装置示意图

采用静态斜坡信号( Ramp)测试法测试ADC转换精度,通过在ADC输入端加载静态电压信号,测得ADC输出端口的数字信号,根据输入电压值与数字输出之间线性关系的好坏,来检验ADC的转换精度。测试装置如图8,将3.3 V的电压通过滑线变阻器分压,然后输入ADC的模拟输入端,调节滑线变阻器,改变输入电压,测得ADC的数字输出端。测试数据如图7所示,其中横坐标表示ADC的模拟输入电压(V),纵坐标为ADC的数字输出量。输入电压值与数字输出满足线性关系,ADC工作正常,能够正确地进行数据转换。

图9 测试数据

4.2系统总体测试

用信号发生器产生一个200 kHz正弦波信号,输入到系统的一个通道上,进行采样测试,将采样数据通过串口传到上位机。采用串口调试助手进行测试。串口的端口号设置为COMI;波特率设置为9 600;无校验位;数据位选择8;停止位选择1。如图10所示,可以在串口调试助手的接收栏中看到该组数据,测试成功。

图10 串口接收数据界面

5 结束语

文中设计了一种多通道超声相控阵数据采集系统,采用内嵌Nios Ⅱ软核处理器的SOPC系统为主控制器,不仅发挥了FPGA在高速复杂的逻辑处理方面的优势,而且充分利用了Nios Ⅱ微处理器中软件操作的灵活性的特点。该系统的嵌入式系统采用MCU、DSP、FPGA结合的方式,符合未来嵌入式系统发展的趋势,打破了传统的CPLD+ MCU的嵌入式系统方案;系统的控制模块在一块FPCA芯片上实现;各通道的数据缓存与控制器之间的数据传输采用总线复用的方式,节省了FPGA的引脚资源,降低了PCB板布线的复杂程度,提高了系统的集成度,便于系统的小型化。

参考文献:

[1]MEYER A P,ANDERSON J W.Ultrasonic testing using phased arrays.In:Proceedings of 15th World Conference on NDT[CD].Rome,Italy:2000.

[2]李爽,周世园.超声相控阵信号采集与B型成像处理.仪器仪表学报,2008(4):268-271.

[3]EDA先锋工作室,吴继华.Altera FPGA/CPLD设计(基础篇).北京:人民邮电出版社,2005.

[4]冯寿廷.FPGA开发快速入门教程.21嵌入式控制科技.2005:31-33.

[5]AD9235:12-Bit,20/40/65 MSPS 3 V A/D Converter Data Sheet[EB/OL].[2013-05-03]http://www.analog.com

[6]Eric Newman,Rob Reeder.A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs [EB/OL][2013-05-03]http://www.analog.com.

[7]APPLICATION NOTE:Fundamentals of Sampled Data Systems[EB/OL].[2013-05-03].http://www.analog.com/zh/data-converters/products/index.html.

[8]王晓迪,张景秀.SOPC系统设计与实践.北京:北京航空航天大学出版社,2008.