基于Mini-LVDS技术的TFT-LCD时序控制器的设计

刘 杰,程松华,张永栋,李曙新

(天马微电子股份有限公司 研发中心,广东 深圳518118)

1 引 言

近年来,随着显示器的分辨率提高,传输给显示器的数据的频率也随之提高。用传统的并行、满摆幅、单端传输信号的方法引起的信号串扰、系统功耗、噪声干扰等问题越来越严重。为了解决此问题,人们开发了各种差分技术。用于液晶显示器的时序控制器与驱动电路之间传输数据的差分技术有RSDS(低摆幅差分信号)和Mini-LVDS(微、低压、差分信号)两种。

Mini-LVDS技术现已广泛应用于平板显示器中,它是在LVDS技术的基础上发展的,进一步优化了用低电压差分信号、采用时钟的双边沿传输信号的特点;降低了信号的电磁干扰;可以根据显示屏的分辨率的大小合理分配数据通道数,以减低数据的传输频率;这些优点极大地提高了液晶显示器的集成度,为液晶显示器具有更大的尺寸、更窄的边界奠定了基础。

液晶显示器常采用专用的时序控制芯片,大多数专用时序控制芯片只能应用于消费领域、高规格芯片资源少、其时序要求是固定的;因特殊分辨率的液晶显示屏常有特殊的时序,此是专用时序控制芯片则无能为力。采用FPGA(Field Programmable Gate Array,现场可编程门阵列)设计的时序控制器可以满足此要求[1]。在基于FPGA的视频处理系统,利用FPGA 除设计时序控制器外,还可以对相关的数据进行处理,而且无需增加外围电路,使整个硬件系统所需的空间变小,从而节省设计成本。

利用Mini-LVDS技术的特点,灵活使用各种数据的并行、串行的转换方法并研究了变换时钟的方法,使用这些方法可以利用简单的Verilog HDL(硬件描述语言)设计Mini-LVDS 接口;不仅能在同一公司的FPGA 芯片内,而且可以在不同公司的FPGA 芯片内,利用此方法设计具有Mini-LVDS接口的TFT-LCD时序控制器,可以提高设计的灵活性。

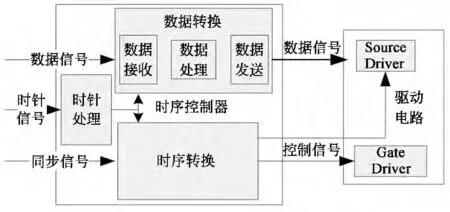

2 TFT-LCD的时序控制器简介

TFT-LCD 的时序控制器由时序转换模块、时钟处理模块和数据转换模块3部分组成,如图1所示。时序转换模块把从信号源接收的同步控制信号变换成驱动电路所需的控制信号。数据转换模块把从信号源接收到的数据信号转换为Source Driver(源驱动器)所需格式的数据信号,它包括数据接收、数据发送、数据处理3部分。时钟处理模块为时序转换模块和数据转换模块提供必需的时钟信号[2-3]。在基于Mini-LVDS技术的时序控制器中,驱动电路中的Source Driver和TCON 之 间 的 数 据 用 Mini-LVDS 技 术 进 行传输。

图1 时序控制器的原理框图Fig.1 Schematic diagram of timing controller

Mini-LVDS的数据通道的数量和像素的颜色深度没有关系,可以根据实际需要设定为3对、4对、5 对或者6 对。除根据数据通道的对数不同,对相邻点的数据进行不同的处理外;每个子像素内的并行数据必需经过并串转换、串行地通过数据线传输给Source Driver,Source Driver把接收到的数据转换为显示屏所需的数据。第0对数据通道除了传输数据外,还传输一个Source Driver的控制信号:和控制行起始信号DIO 作用相同的复位信号RST[4]。

3 时序控制器的设计

3.1 Mini-LVDS的数据转换

图2为在本设计中Source Driver的数据输入端的数据排列示意图,子像素的颜色深度是8位,输入数据通道为6对[5-6]。在4个时钟内,第0~2 对数据通道分别传输第一个像素点8 位RGB数据共24位数据;同时第3~5对数据通道分别传输第二个像素点8位RGB数据共24位数据;Mini-LVDS接口在每4个时钟内传输2个像素点的RGB数据共48位数据。为了进一步降低数据的传输频率,2颗Source Driver没有采用常用的级联的方式,而是采用了并联、同时接受数据的连接方式。

图2 Mini-LVDS接口的数据排列示意图Fig.2 Data arrangement diagram of the Mini-LVDS interface

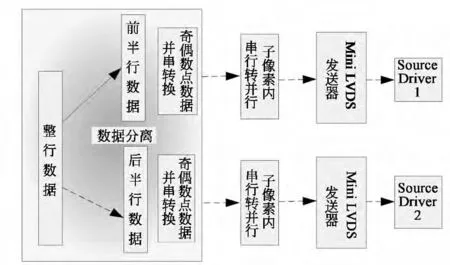

据此,设计如图3所示数据处理方法。数据处理包含数据分离和单色子像素内数据处理二大部分,其中数据分离包含一整行数据处理和奇数、偶数点的数据处理二部分。具体包括单色子像素内8位并行转8位串行数据的并串转换、奇数、偶数点的数据同时发出的并行排列、一行数据分成前半行、后半行二部分后同时发出的并行排列。

图3 Mini-LVDS接口的数据处理意图Fig.3 Data disposing diagram of the Mini-LVDS interface

3.1.1 数据分离处理

数据分离模块主要数据的前半行、后半行分离和奇数点、偶数点的分离两部分。数据的前、后半行分离采用FPGA 片内SRAM 实现,数据的分离主要采用乒乓操作的方式进行。当第一行的数据依次传输过来时将D1,D2,D3……Dm-1等前半行的数据存储在SRAM1 单元,而Dm,Dm+1,Dm+2,Dn等后半行的数据存储在SRAM2单元;而当第二行的数据传输过来时将D1,D2,D3……Dm-1等前半行的数据存储在SRAM3单元,而Dm,Dm+1,Dm+2,Dn 等后半行的数据存储在SRAM4单元。由于第一行和第二行依次传输过来,因此在接收第二行数据的同时,存储在SRAM1和SRAM2中的第一行的数据则开始同时被取出送到下一个数据处理模块。同理,当第三行数据过来时,第一行数据已经取完,第二行数据已经存完,这样第三行的数据又按照前、后半行分别存入SRAM1和SRAM2,而存储SRAM3和SRAM4中的第二行的数据则开始同时被取出送到下一个数据处理模块。如此循环,依次将数据分别传输到下一个数据处理模块,完成一次数据的前、后半行分离处理,如图4所示。

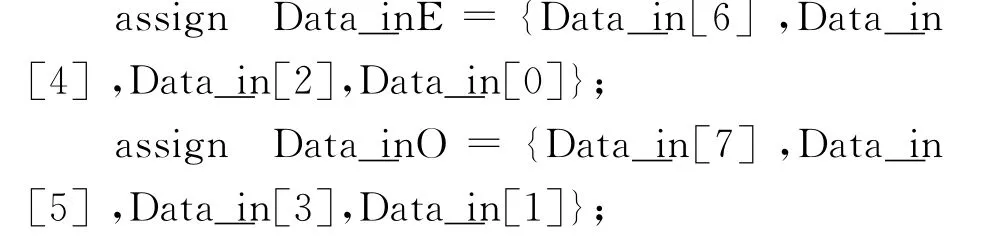

因本次处理的数据是流水线型,奇数点、偶数点的分离采用D 寄存器的方法进行串并转换。让第一点的数据暂缓延时一个时钟,与第二个数据同时发出。经过了转换的数据同时输入到下一个转换器,实现一个数据的2∶1并串转换。

图4 数据存储及分流Fig.4 Data storage and diversion

3.1.2 子像素内并串转换模块设计

通用的多位数据并串转换的实现方法有:先进先出寄存器(FIFO)和移位寄存器等两种。当采用FIFO 模式时,FIFO 的输入端的宽度和输入数据的宽度相同,输出端的宽度为1,两者在不同的时钟下工作,从而实现并串转换。当采用移位寄存器时,各位数据首先通过并行锁存器同时写入与数据位数相同个数、首尾相连构成一个移位链的D 触发器,这些D 触发器可以在移位时钟的控制下将数据串行输出。因串行并的数据排列方式的特殊性,先综合使用移位寄存器和串行加法器,设计一个4∶1 的并串转换电路。再利用DDR技术,设计了一种2∶1的并串转换电路,综合两个转换器的功能实现8∶1的并串转换电路,从而现实了子像素内数据的并串转换。这种设计方法充分利用了FPGA 的资源,降低了系统处理数据的频率,提高了系统的稳定性。

先将图5的图A 的原始数据按照不同的采集边沿重新排列,排列后的数据的排列的格式如图5的图B,方法如下:

将从图5的图B 中输出的数据经过4∶1的并串转换电路,重新排列成图C 的格式,利用串行加法器控制数据装入转换器的时刻,然后高速采样时钟作用逐次移出数据从而实现4:1的并串转换电路。方法如下:

图5 并串转换模块的输出原理示意图Fig.5 Sketch map of a parallel to serial converter’s output

DDR 输出接口,使得在通用并串转换电路的移位时钟频率相同的情况下,可以使串行数据传输的频率提高2 倍。在两个反相时钟CLK1、CLK2控制下,输入数据D1、D2同时锁存到D 触发器,然后通过一个2∶1的多路选择器以分时复用的方式输出数据,使得数据传输的频率提高2倍,因此控制时钟的频率只需要数据传输频率的一半。按照上面方法,将并行数据分别以两个差分倍频时钟按奇偶两组锁存,通过DDR 接口,就可以实现并串转换。Xilinx的FPGA 的ODDR2接口宏单元块支持这种转换,此宏单元块的使用方法如下:

3.1.3 Mini-LVDS发送模块的设计

FPGA 是CMOS 逻辑器件,它只能处理COMS逻辑电平信号,在发送时需将CMOS逻辑电平信号转换为Mini-LVDS差分信号。所有类型的FPGA 芯片都有支持这种转换IP Core,Xilinx公司的OBUFDS 单元可以支持这种信号转换方法,此宏单元块的使用方法如下。

3.3 Mini-LVDS的时钟处理

Mini-LVDS除了传输数据之外,还需要传输时钟。Mini-LVDS的时钟的频率和像素的频率之间存在着一定的倍数关系,这个倍数关系可以根据像素颜色深度和数据通道数计算出来。例如,当像素的颜色深度为24、有6对数据线(双沿采样数据,每个时钟周期采样8 个数据)的情况下,Mini-LVDS的时钟频率等于像素频率2倍。

从上面的数据处理过程可以发现,时序控制器需多个时钟信号。Xilinx 公司的FPGA 内部的数字时钟管理器(DCM)可以满足此要求,DCM 的功能包括消除时钟的延时、频率的合成、时钟相位调整。DCM 共由4部分组成,可以输出的时钟:

与输入频率相同的 CLK0、CLK180、CLK270;是 输 入 频 率 2 倍 的 CLK2X、CLK2X180;分频系数为1.5、2.5、3、4、6、8、16等频率CLKDV、任意频率的CLKFX、CLKFX180等时钟。DCM 的数字频率合成器DFS模块可以生成一个Mini-LVDS发送时钟,其他时钟可以有DCM 的其他部分生成[7]。

如果该发送时钟频率是数据时钟频率的4倍,可利用DDR 技术来获得数值为8的串行化因数。DDR 技术可以将所要求的时钟频率降低一半,不仅能使FPGA 时钟位于正常工作的频率范围内,而且能降低系统的总功耗。利用DDR 触发器(ODDR2)完成DDR 技术,需要利用二个相位相反的时钟。使用两个全局时钟缓冲器GCLK,将从DCM 的任意频率输出端CLKFX 和CLKFX180输出的两个时钟(相位相差180°)分配给DDR 触发器。这种方式仅使用了时钟的上升沿,时钟网络上的任何占空比失真都变得不重要。

3.4 复位信号的要求及相关数据处理

Source Driver除接收数据外,还需接收表示开始接收数据控制信号(DIO)和表示结束接收数据的控制信号(LD)。DIO 又可分为DIO1 与DIO2,它们不同高低电平的组合决定显示数据扫描输出的方向顺序,即数据从左到右还是从右到左输出。如选择从左到右的数据输出,则在DIO1下降沿后,在每个时钟周期内输出一个Pixel的数据,在输出到倒数第二个Pixel数据时,DIO2输出高电平,直到其为低电平,表示所有显示数据输出完毕。如TFT-LCD 应用两颗Source Driver级联,则DIO2 作为下一颗Source Driver的输入;为了进一步降低数据的频率,Source Driver没有采用级联的方式,而是采用了并联、同时接受数据的连接方式,这种方法的缺点是每个Source Driver都需接收控制信号。

图6 复位信号的要求Fig.6 Request of reset signal

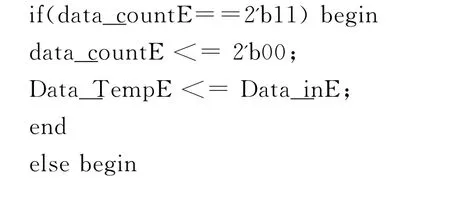

在Mini-LVDS 技术中,控制行起始信号的DIO 由复位信号RST 替代并经第0对数据向外传输;此时,还需将原有的DIO 信号置高,其时序要求如图6所示。复位信号RST 置高的复位时间起始点与LD 信号的上升沿的间隔大于20ns。将复位信号RST 置高的复位时间长度必须同时满足两个条件:时间大于50ns和大于3个时钟;通过计算,在本设计中至少需5 个时钟的时间。为了扩大时序控制器的稳定性,利用数据有效信号DE 的有效内前5个时钟将复位信号RST 置高,然后再一个时钟的置低,这样需显示的数据必须向后移位6个时钟,数据移位的方法有:先进先出的FIFO、移位寄存器和SRAM 等方法。因数据延时的长度不大,本设计使用移位寄存器的方法。

4 FPGA 实现

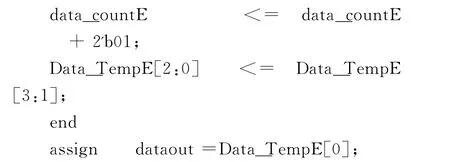

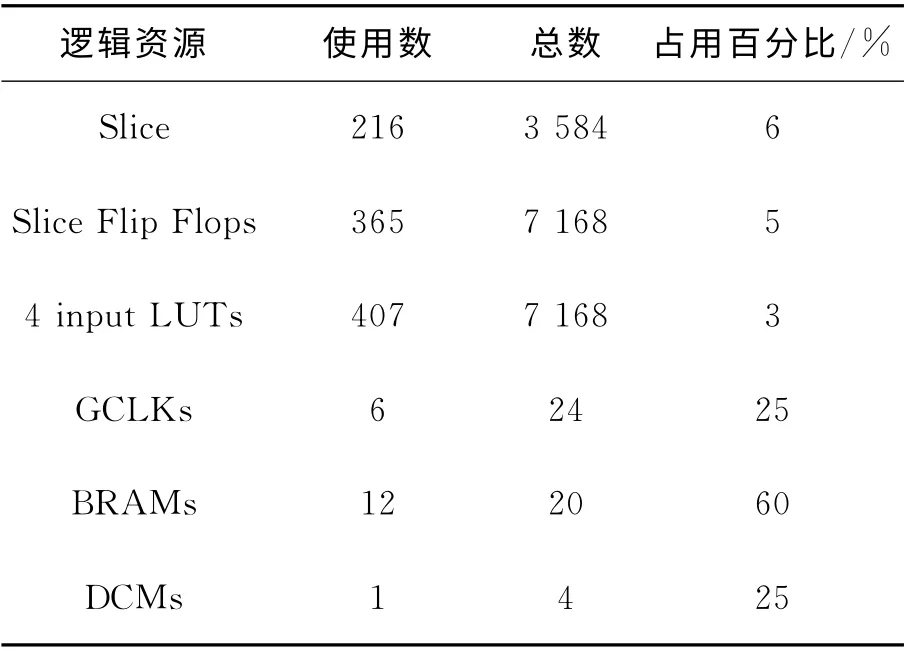

采用Verilog HDL语言来设计,设计了基于Mini-LVDS 技 术 的TFT-LCD 的 时 序 控 制 器,使 用Xilinx的型号为XC3S400AN 的FPGA 并在其开发平台ISE11.2中进行逻辑综合和器件适配,该功能所使用逻辑资源情况如表1所示。它占用的逻辑资源很少,还有很多资源可以用于其它作用。

表1 Mini-LVDS接口所占用逻辑资源Tab.1 Logical resource of Mini-LVDS interface

在基于FPGA 的视频信号处理系统中,基于Mini-LVDS技术的TFT-LCD 的时序控制器只是该系统的一个功能块,而这部分的信号的频率最高、需在多个时钟域进行变换。为了提高系统的稳定性,使该时序控制器正常工作时,不产生干扰、不影响其他功能,就必需对该部分进行必要的时序约束。FPGA 的时序约束有周期约束、特定约束、区域约束等约束。因这部分的输入信号的频率高,使用区域约束使Mini-LVDS接口在信号的输入管脚附近。

5 结 论

详细说明了基于Mini-LVDS 技术的TFTLCD 的时序控制器的方法,利用此方法设计出的具有Mini-LVDS接口的时序控制器已应用于本公司的分辨率为1 280×1 024、颜色深度为24bit的产品中,该产品的画面清晰,过渡自然,说明此基 于Mini-LVDS 技 术 的TFT-LCD 的 时 序 控 制器完全符合要求。

[1] 罗菊华,杨传仁,张继华,等.基于FPGA 的平板显示器件驱动电路的设计[J].液晶与显示,2006,21(6):680-685.Lou J H,Yang C R,Zhang J H,et al.Design of driving circuit for flat panel display based on FPGA [J].Chinese Journal of Liquid Crystals and Displays,2006,21(6):680-685.(in Chinese)

[2] 程明,肖祖胜.基于FPGA 的TFT-LCD显示驱动设计[J].液晶与显示,2009,24(2):228-231.Cheng M,Xiao Z S.Design of display driving for TFT-LCD based on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2009,24(2):228-231.(in Chinese)

[3] 潘子升,苗绘玲.时序控制器TCON 的研究与设计[J].电子设计工程,2011,19(3):67-70.Pan Z S,Miao H L.Research and design of timing controller[J].Electronic Design Engineering,2011,19(3):67-70.(in Chinese)

[4] 金强宁,洪乙又,李慧芝,等.基于Mini-LVDS技术的TFT-LCD 彩色液晶显示屏的驱动研究及应用[J].光电子技术,2009,29(3):196-200.Jin Q N,Hong Y Y,Li H Z,et al.The application and study of color TFT-LCD panel driver based on Mini-LVDS technology[J].OptoElectronic Technology,2009,29(3):196-200.(in Chinese)

[5] Online Texas Instruments.SLDA007A[EB/OL].2001-08.http://www.ti.com/

[6] Online Novatek Microelectronics Corp.NT39815[EB/OL].2011-08.http://www.novatek.com.tw/

[7] 孙航,胡灵博.Xilinx可编程逻辑器件应用与系统设计[M].北京:电子工业出版社,2008:230-240.Sun H,Hu L B.System Design and Application of Xilinx Programmable Logic Device [M].Beijing:Electronic Industry Press,2008:230-240.(in Chinese)