未来视频编码器的主流——软编码

王 贺

(上海国茂数字技术有限公司,上海201203)

责任编辑:许 盈

我国自主产权的高级视频编码协议AVS、AVS+[1]相继成熟并确定,其编码效率与H.264/AVC[2]达到了同一档次[3]。近几年,AVS实时高清编码器在各类市场中都有较大的需求,最有代表性的是广播级视频编码器。广播级视频编码器产品按照平台来分类,大致可以分为两类:一类是“硬编码”,另一类是“软编码”。

最传统的硬件编码器是没有操作系统参与的完全由数字逻辑电路完成编码操作的数字电路设备,如广为应用的74系列编码器。在视频编码器领域的硬编码,指的是所有编码工作都由ASIC芯片完成,没有操作系统和软件参与的编码方案,比如富士通的MB86H50芯片,能够实现H.264的准高清编码,但是编码质量有限制。由于商用视频编码器功能要求高,其功能模块中不仅包含视频编码模块,一般还包括了音视频采集、音频编码、码流复用、加密等功能模块,没有操作系统和软件的支持是无法实现的。只要编码器需要操作系统支持,并且有软件参与工作的都属于软件编码器,即行业内所说的软编码,软编码按照所使用的操作系统分为两大类,一类是加载嵌入式操作系统的方案,如DSP+FPGA,ARM+DSP,ARM+FPGA以及CPU+FPGA;另一类是基于多媒体服务器的方案。下一节对现有的几种常见的软编码方案进行介绍。

1 软编码方案介绍

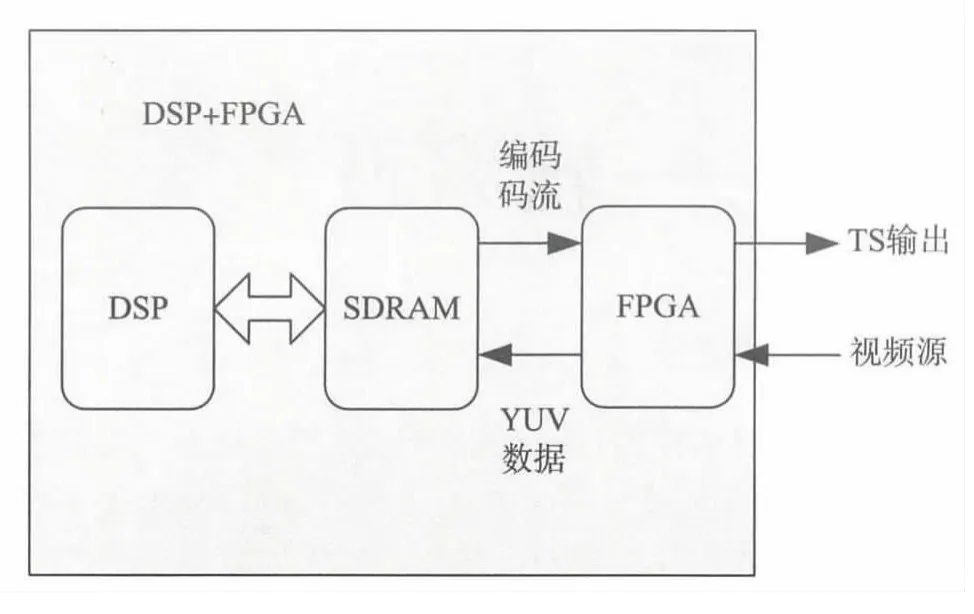

1.1 DSP+FPGA方案

该方案中FPGA只承担了视频数据采集与编码码流输出的功能,而主要的编码工作由DSP处理器承担,DSP加载了裁剪的Linux操作系统或者定制的Sysbios系统完成编码软件的调度,编码过程中DSP与FPGA之间存在数据交互[4]。因此对于DSP的处理能力要求较高,较低端的DSP处理器无法满足广播级编码的要求,因此各大厂商也推出了针对视频处理的DSP产品,比如TI公司的Keystone系列DSP芯片。该方案的逻辑图如图1所示,FPGA首先将输入信号复合YUV图像数据,送到SDRAM中间缓存中,DSP读取缓存中的YUV数据进行压缩编码,DSP的程序架构是完全的软件架构,不同的DSP处理器对多线程的处理方式有所不同。最后将压缩的码流再转交给FPGA模块,由FPGA模块负责将TS(Transport Stream)数据发送出去。

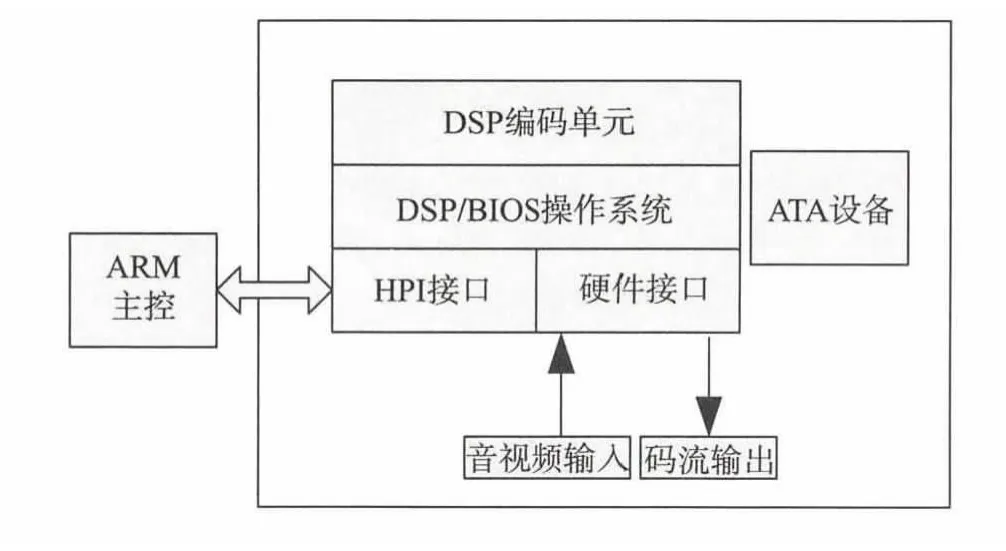

1.2 ARM+DSP方案

ARM处理器具有体积小、功耗低、成本低的特点,同时作为一种通用处理器,数据管理能力强,扩展接口丰富。如图2所示,该方案的系统主控制模块以ARM处理器为核心[5],负责系统的通用控制,也负责与DSP视频处理的通信控制。视频处理模块以DSP芯片为核心,负责视频数据的采集、视频存储等功能。系统可以包括多路的音频、视频输入。DSP视频处理模块作为子系统,接受ARM的控制,与ARM有大量的视频数据通信。ARM控制模块与DSP视频处理模块,各自是一个独立的嵌入式计算系统,除了数据交互外,二者的开发调试都是分开和独立的。自下向上,都包括硬件设备层、设备驱动层、操作系统层和应用程序层四层。

图1 DSP+FPGA方案逻辑框图

图2 ARM+DSP系统框图

在ARM主控制模块中,硬件设备包括SDRAM、Flash、时钟管理、电源管理等核心模块,构成一个最小系统,能支持整个编码系统的运行。为了软硬件开发和外部设备扩展,硬件设备包括如下几部分:JTAG调试电路,模拟/数字信号采集模块,DSP数据交换总线等。DSP视频处理模块的硬件设备包括视频采集、编码、存储等部分。该方案加载的DSP/BIOS是一个简易的实时嵌入式操作系统,主要用于完成同步、编码控制通信以及实时检测等功能。

ARM与DSP的通信方式有多种,比如串口通信、网络通信、HPI并行连接通信等方式。这些方式各有优缺点和适用场合,该方案采用的是HPI连接方式。当采集数据队列准备好之后,ARM通过HPI收到采集完成信号,然后ARM发送编码启动的信号给DSP,调用DSP的一个核来启动一个线程,通过这种方式完成编码。对外围设备的调度、码流的输入输出以及网络功能的实现等也由ARM处理器加载的嵌入式操作系统完成。

1.3 ARM+FPGA和CPU+FPGA方案

这两种方案中,ARM和CPU加载嵌入式操作系统,完成编码流程调度和数据输入输出功能。FPGA承担大部分的编码工作量,比如运动估计、变换量化等编工作。方案[6]如图3所示,ARM与FPGA之间通过AHB总线通信,由于计算能力的限制,编码任务量是非对称地分布在两个处理核心之间,ARM承担了码流复用和可变长熵编码,主要的预测工作由FPGA完成。FPGA中的编码模块被分为前向、后向两个通路,在前向通路中,宏块数据的地址由地址发生器产生,根据地址送入帧内或者帧间预测单元。然后根据预测结果得到残差值,将残差值送入DCT变换和量化单元,根据不同的QP设置输出不同质量的变换量化结果。变换量化后的数据作为编码数据通过AHB总线送入ARM进行可变长编码。在FPGA的后向通路中,编码数据被解码后重建作为参考图像为后续图像作参考帧。FPGA内部所有的编码流程是由一个逻辑控制单元控制的,在一帧图像内的编码顺序是依照宏块的排列顺序。CPU+FPGA的方案与ARM+FPGA方案基本一致,不同之处在于多核CPU可以更多地分担编码工作量,提供更好的编码质量。

图3 ARM+FPGA系统框图

FPGA的功能是由硬件描述语言实现的,如果FPGA运行出错,那么错误排查非常复杂。而且由于FPGA开发要顾及时序和布线等问题,FPGA上任何一个编码工具的调整都会影响其他编码工具的实现,那么就使得对FPGA的功能升级困难,而且FPGA与主控核心之间的数据通信依然是系统开发的难点。

1.4 高性能服务器平台

在多核技术广泛应用之前,单核CPU的处理频率存在瓶颈,使得单个CPU无法负担高清实时编码巨大的计算量,不得不借助于专用ASIC处理芯片;多核技术的成熟,使得CPU的计算能力出现了飞跃,随着CPU的并行处理核心数增加,其处理能力得到了数倍甚至数十倍的提高,选择ASIC芯片辅助编码的必要性已经失去。知名的编码器厂商都有自己的广播级软件视频编码器产品。由于编码工作都是由多核CPU运行软件完成的,能够完善地继承参考模型中各个编码工具的功能。在该类编码器的研发中无需考虑其他几种方案遇到的工程问题,比如不同处理核心之间的通信问题,主要工作内容就集中在提高编码效率、完善软件架构。

方案[7]的并行架构如图4所示,原始图像Fn通过前向路径:预测(帧内或帧间)、整数变换、量化和熵编码获得编码码流,而通过重构路径,即反量化、反变换、运动补偿来获得重建图像F'n,用作预测编码的参考帧。为经过并行预处理后的原始图像,MV’为经过整像素运动估计后的运动矢量,MV为经过亚像素运动估计后的最终运动矢量。该框架主要可分为3大部分,分别为预处理模块、运动估计模块以及编码模块。虽然3个模块是串行连接的,但各模块之间有一定的帧数量延迟时间,因此各个模块就可以独立并行工作:当第1个模块进行了M帧数据的处理后,第2个模块便开始运行;当第2个模块对数据进行了N帧处理后,第3个模块就开始进行编码处理。由于在实际的视频编码系统中,除去视频数据的输入输出、存储设备的初始时间以及硬件平台的启动时间,单纯在编码模块中运动估计部分往往占据最多的编码时间。而在运动估计中,整像素运动估计在多参考帧模式下占据最大的计算量和计算时间,因此,整像素运动估计的并行化是解决问题的关键。该方案的编码框架利用了编码延迟能够缓冲帧的特点,同时充分利用预处理模块获得的帧类型参数,使运动估计模块对每帧数据独立地并行化运动估计,经过运动估计后视频帧才进入编码模块。这种并行运动估计极大地提高了整个编码框架的并行性,也极大地提高了多核计算资源的利用率。在并行运动估计完成后进行运动补偿,然后对残差图像进行DCT变换、量化以及熵编码来得到最终码流。由于在这些模块没有整像素运动估计那么高的计算复杂度,因此计算速度提高很多,也提高了帧间预测的效率,从而能够减小并行帧数。经实验验证,该方案的率失真性能相比理论最优的率失真性能仅仅低约0.2 dB,保证了编码图像的高质量。

高性能服务器的硬件平台是经过了市场的多年验证的,稳定性很高,而且专业级的操作系统的功能较为强大,可以灵活选用功能最优的输入输出设备,在更换外围设备时对视频编码核心没有任何影响。同时,可以针对不同用户需求定制复用、加密等功能,而且可以通过对软件的修改完成对各种复杂网络功能的支持。当编码器厂商在对编码核心进行调整优化后,可以及时地对用户的编码器进行在线升级,换言之,在软件编码器的使用过程中,其性能可以随着时间不断提升,这就使得广电运行商的带宽压力不断减小,编码功能的选择也不断增加,客观上延长了产品的生命期。

图4 多核服务器并行编码软件架构

2 各类编码器的比较

由于不需要加载操作系统,硬编码在启动速度上快于软编码。也是因为没有操作系统,所以硬编码的功能有很大局限性,故大量的编码芯片是应用在如视频监控、移动设备数据压缩等领域,广播级的编码设备没有纯粹的ASIC芯片编码器。硬编码的另一个缺陷是编码质量稍逊,而且市场上尚无能支持1 080p全高清编码的广播级编码芯片。

采用了ARM,DSP,FPGA等元件的编码器,整体体积可以做得相对小,但各个器件之间存在设备间数据通信问题,在特殊条件下可能引起数据的不稳定。FPGA对串行性较强的数据处理能力较差,必须依赖其他处理单元协同处理。而且FPGA的功能更新困难,升级不便,如果运行出现错误,排除错误的周期也较长。由于该方案的硬件平台不是通用平台,都需要特殊定制,对平台的稳定性需要长期观察。

服务器平台方案对视频编码工具的功能裁剪最少,故编码图像质量最好。该方案使用的编码软件是在成熟的环境中开发的,相关资源丰富、可靠,有利于功能的更新升级,而且对网络功能的应用更友好。硬件平台方面,国际厂商所提供的服务器平台在设计、选材的能力方面强于普通厂商,其硬件平台可靠性有保证,而且对于外围设备兼容性更好,对潜在的功能扩展有好处。

表1是几个主要性能评价标准的对比表格,可以看出在整体性能上,高性能服务器平台具有巨大优势。

表1 各类平台性能对比

3 小结

本文首先介绍了硬编码和软编码的定义,并且对常见的软编码方案进行了介绍,指出各个方案的特点,随后进行了对比,指出软编码的优势。在互联网时代,广播电视设备不可避免地在向网络化、IP化过渡,因此对视频编码器是否能支持更复杂的网络功能要求,比如视频的网络组播、视频编码器的远程网络管理,是评价一个编码器是否合格的重要标准,而且未来的编码器将集成各种各样的媒体处理功能,那么对编码器的整体性能的要求也非常高。当今视频编码技术和网络技术更新的速度在加快,软编码必将是未来视频编码器的主流。

[1]GB/T 20090.2—2006,信息技术先进音视频编码第2部分:视频[S].2006.

[2]ISO/IEC11496-10:2005(E),Advanced video coding for generic audiovisual services[S].2005.

[3]张伟民.AVS+标准的主观图像质量对比分析[J].电视技术,2013,37(21):9-11.

[4]牛建伟,胡建平,毛士艺.基于DSP和FPGA的视频编码器协同设计与算法优化实现[J].航空学报,2005,26(1):90-92.

[5]王应莉.基于ARM+DSP架构的视频处理系统[D].成都:电子科技大学,2007.

[6]LICCIARDO G,COSTAGLIOLA M.An H.264 encoder for real time video processing designed forSPEAr customizable system-on-chip family[C]//Proc.IEEE International Conference on Signal Processing and Communications(ICSPC).Dubai:IEEE Press,2007:824-827.

[7]蒋骁辰,李国平,王国中,等.基于AVS+实时编码的多核并行视频编码算法[J].电子与信息学报,2014,36(4):810-816.

- 电视技术的其它文章

- CCC认证中的谐波电流检测的必要性分析