一款低抖动宽调节范围锁相环频率合成器的设计

薛 颜,杨霄垒,周启才,陈珍海,吴 俊

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

0 引 言

随着集成电路技术的发展,芯片的工作频率不断提升,对时钟精度的要求也越来越高。传统的晶体振荡器虽然具有低噪声、低抖动的性能,但是它所能提供的频率很低。为了能够获得一个高的、稳定的输出频率,可以利用锁相环频率合成器(PLL,phase locked loop)。锁相环频率合成器能够根据分频器的分频比来确定输入参考频率和输出频率之间的关系,并根据分频器的分频比将输入时钟倍频,进而获得较高频率的时钟输出。锁相环频率合成器的应用非常广泛,随着通讯技术从低速并行结构向高速串行结构转移,锁相环频率合成器起着越来越重要的作用[1]。

对于严格的周期性时钟信号,包含的过零点在时间轴上间隔相等。而对于近似周期性的时钟信号,其周期有微小的变化,使得过零点偏离了其理想位置,这种微小的变化称之为抖动。抖动的产生机理有很多种。PLL本身的性能及噪声都会让PLL的输出产生抖动。文献[2]中提到鉴频鉴相器的鉴相死区使压控振荡器(VCO)相对输入必须将随机相位差积累到Ø0时环路才得到正确的反馈。在这过程中VCO输出的过零点就会有相当大的抖动。文中采用0.18 μm工艺设计了一款低抖动、宽调节范围、高频、低功耗的电荷泵锁相环频率合成器。锁相环频率合成器在不同的频率选择不同的鉴频鉴相器复位时长,改变脉冲宽度,从而有效消除PFD鉴相死区的影响,降低锁相环频率合成器的抖动。

1 锁相环频率合成器结构

所设计的锁相环频率合成器基本结构,如图1所示,由预分频器、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器等模块组成。

图1 锁相环频率合成器结构框图

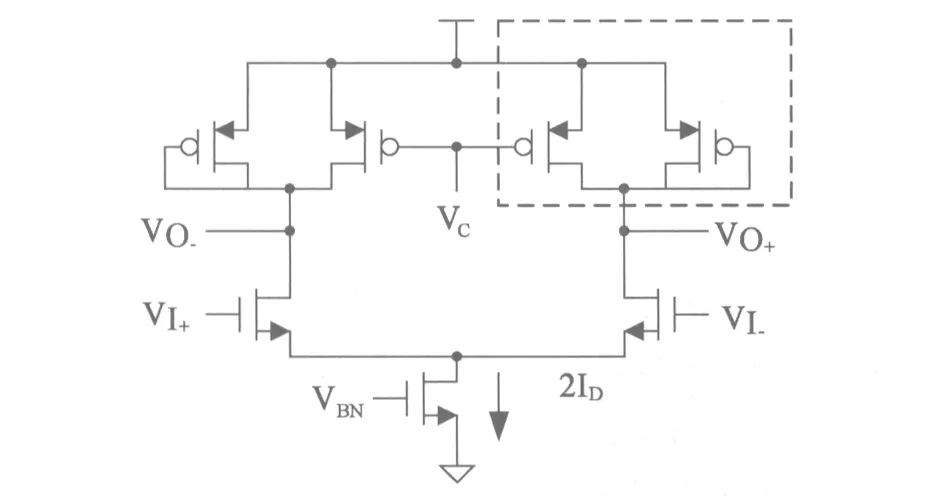

压控振荡器由基于图2的缓冲级构成。该缓冲级包括一个差分对和被称为对称负载(图中虚线框内)的电阻负载元件。对称负载由一个二极管连接的PMOS与一个相同尺寸的偏置PMOS并联而得。如果有电流,那么右边的二极管连接的管子始终处于饱和状态,而左边的PMOS管则有可能在饱和区,也有可能在线性区。文献[3,4]中给出结论,VC决定了输出VO的下限。由于负载元件的有效电阻随VC改变,所以缓冲级延迟也随着VC改变。可以看出,这些负载元件可以精确控制延迟并具有高动态电源噪声抑制能力。随着VC的变化,对称负载的电阻也发生变化,缓冲级的延时也发生变化。

图2 带对称负载的差分缓冲级

压控振荡器由4个缓冲级组成,在VC从0 V~1.8 V的变化范围内,压控振荡器的输出频率范围为0.8 GHz~3.8 GHz,输出波形,如图3所示。对于宽调节范围的PLL,需要在其不同的频段选择合适的方法用以降低PLL的抖动。这里提出了一种新的PFD结构。

图3 压控振荡器频率输出线性曲线

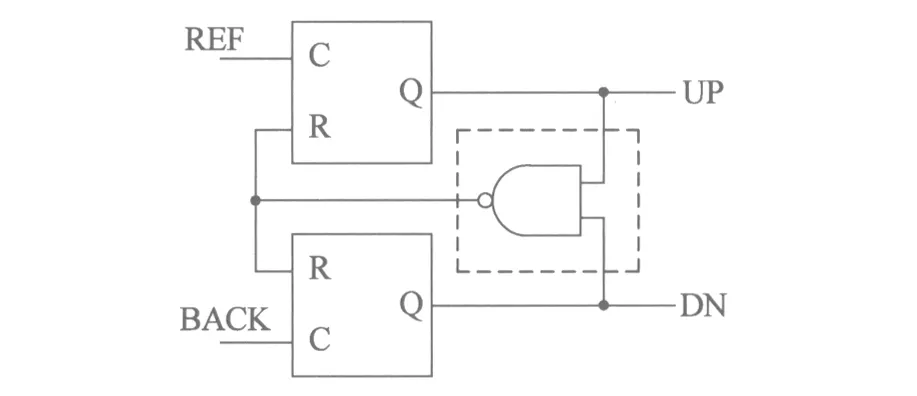

传统PLL的鉴频鉴相器由两个带复位端的上升沿D触发器和一个反相器组成[4],触发器D端接高电平,如图4所示。输入参考信号流入REF,压控振荡器反馈回来的频率信号通过分频器分频后流入BACK端,两个D触发器交叉耦合,分别响应REF、BACK及RESET信号的上升沿,形成UP、DN信号驱动电荷泵的充放电开关,用以调节VC值。但由于在这些结点存在电容,因此会有一定的上升时间和下降时间,使得这个脉冲可能没有足够的时间到达高电平,从而无法打开电荷泵的充放电开关,这便是鉴频鉴相器的鉴相死区。死区是不希望出现的,因为它使得压控振荡器相对输入必须将随机相位差积累到一定值时环路才得到正确的反馈[6]。

图4 传统鉴频鉴相器电路

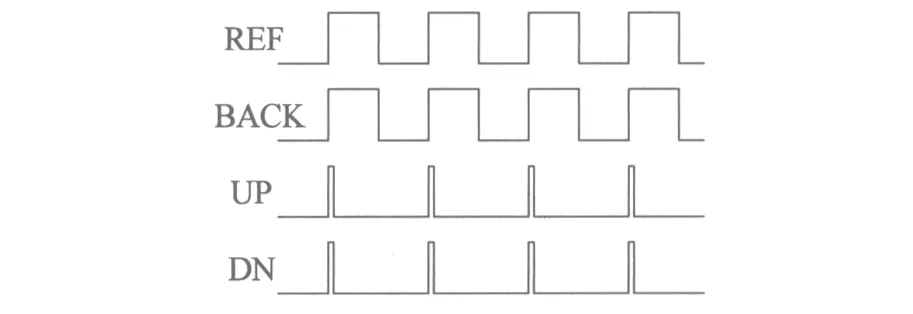

当REF信号和BACK信号的相位差为零时,即锁相环锁定时,UP和DN两端产生窄的、重合的脉冲,如图5所示。

图5 在零相位差情况下鉴频鉴相器输出的重合脉冲

如果REF和BACK同时上升,UP和DN也会同时上升,并激发寄存器复位,产生窄脉冲,它们会在有限的时间内同时打开电荷泵[6]。使得电荷泵能够对鉴频鉴相器输入的微小相位差作出反应。从而有效消除鉴相死区。

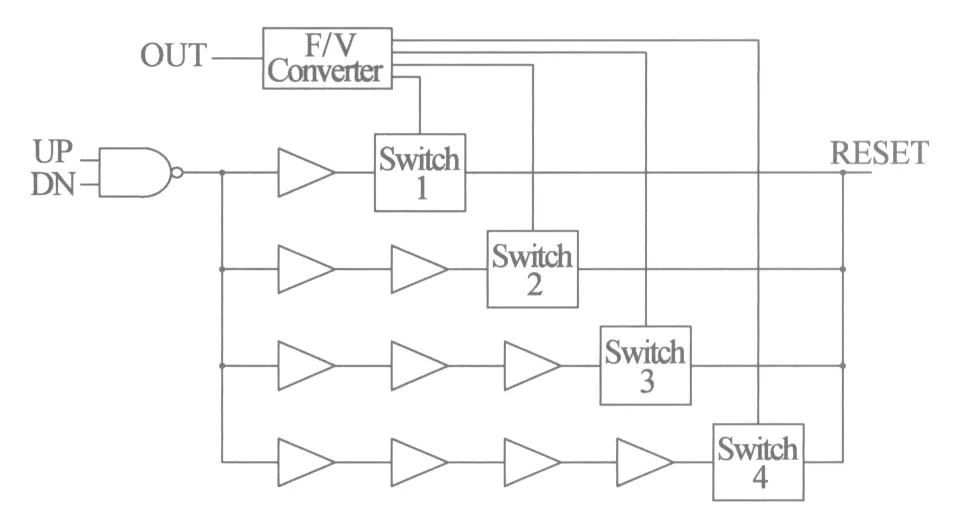

只要UP、DN上的脉冲足够宽,则这些脉冲总会开启电荷泵。当相位差增加一个极小的量时,电荷泵产生的净电流也成比例增加。如果脉冲足够宽,UP和DN都可以达到有效的逻辑高电平,使电荷泵开关导通。而这个脉冲宽度的大小取决于复位信号的门延时。在频率调节范围很大的情况下,这个脉冲宽度就需要一个合适的范围。如果脉冲过窄则不能有效的消除死区,但是脉冲过宽,又将导致锁相环不能正常锁定。所设计的锁相环,在频率为低频分段时,相对较宽的脉冲可以有效的消除死区;但是在高频分段,如果继续使用较宽的脉冲,那么脉冲宽度将可能大于反馈回来的频率周期导致鉴频鉴相器无法跟踪频率,而使锁相环无法锁定。因此本文提出了一种新型可以自调节脉冲宽度的鉴频鉴相器,根据压控振荡器的输出频率范围在不同的频段控制打开不同的通路,做到选择不同的脉冲宽度。这里将压控振荡器的输出频率范围分为0.8 GHz~1.6 GHz、1.55 GHz~2.35 GHz、2.3 GHz~3.1 GHz、3.05 GHz~3.8 GHz四个不同的分段。当压控振荡器处于这四个不同的分段时,压控振荡器的输出OUT信号通过文献[7]中提到的频率-电压转换器来控制四个不同通路的开关,选择不同的脉冲宽度,从而有效的降低了锁相环的抖动。

图4中的虚线框部分经过改进实现上述功能。UP、DN信号经过与非门后,分别通过四路不同的缓冲器,有了不同的门延时,这样脉冲的宽度就有不同,如图6所示。这四路不同的门延时分由四个开关电路控制。压控振荡器反馈回来的频率信号OUT经过频率-电压转换器转换为电压,然后与四个参考频率作比较,控制四个开关电路的开断,选择相应的通路,由不同的门延时产生相应的脉冲宽度。当频率小于1.55 GHz时,Switch4打开,其余关断,这时鉴频鉴相器拥有最大的脉冲宽度,这样的脉冲宽度可以在低频段有效的开启电荷泵,消除鉴频鉴相器的鉴相死区,从而降低锁相环的抖动;在频率大于3.05 GHz时,Switch1打开,其余关断,这时鉴频鉴相器有最小的脉冲宽度。由于在高频段继续采用较宽的脉冲会导致鉴频鉴相器无法辨识相位差,导致锁相环无法正常工作,因此,需要在高频分段相应降低门延时的大小,缩小脉冲宽度,在保证锁相环正常工作的前提下,增大脉冲宽度,让电荷泵尽可能在相位增加时有效开启,消除鉴频鉴相器的鉴相死区。

图6 鉴频鉴相器脉宽自调节电路

2 仿真结果

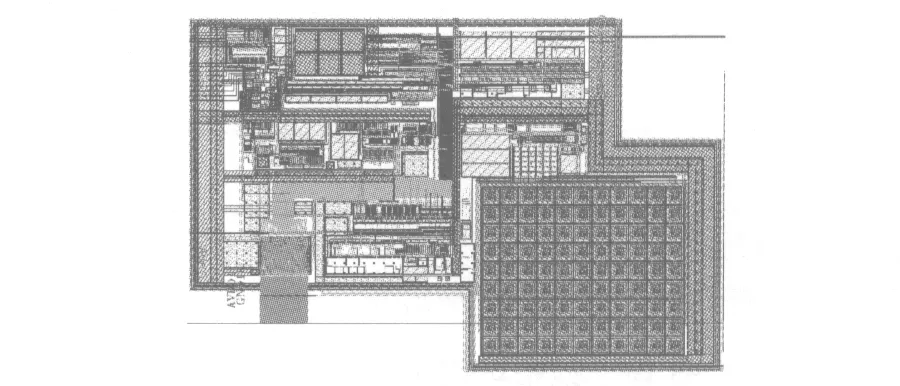

采用此种新型鉴频鉴相器,配合自有的电荷泵、低通滤波器,以及分频器等电路,设计了一款低抖动的锁相环。该芯片采用SMIC公司提供的一层多晶硅、五层金属0.18 μm CMOS工艺实现,面积为700 μm×400 μm。锁相环整体版图,如图7所示,提取寄生参数进行版图后仿真。

图7 锁相环整体版图

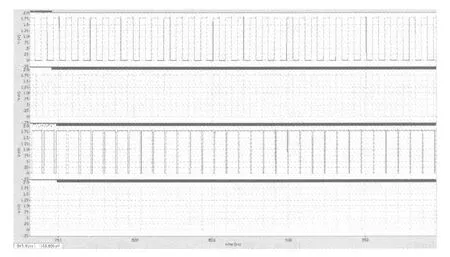

鉴频鉴相器的输入及输出UP、DN信号的仿真结果局部放大图,如图8所示。图中显示在750 ns~950 ns这个区间内,反馈时钟(B)由相位滞后参考时钟(A)到与参考时钟对齐的情况。由于VCO的频率逐渐增大,在850 ns的时间点上可以看出DN信号的窄脉冲有微弱的变窄。

图8 鉴频鉴相器仿真结果

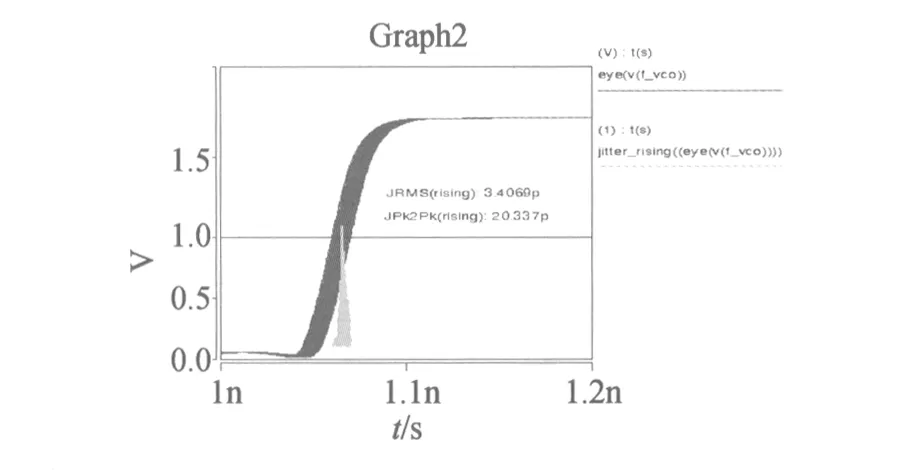

PLL输出抖动眼图曲线,如图9所示。图中横轴为时间轴,纵坐标为PLL输出摆幅。利用看图COSMOS工具将HSPICE仿真得到的PLL输出频率的上升沿进行叠加4 000个周期,计算得到均方根抖动为3.406 9 ps,峰-峰值抖动为20.337 ps。

图9 输出抖动眼图曲线

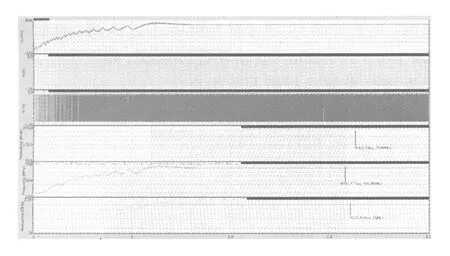

模拟结果,如图10所示。输入频率为250 MHz,分频比为8倍频,输出频率为2 GHz。仿真结果显示,锁相环在0.8 μs锁定。

图10 锁相环锁定过程仿真图

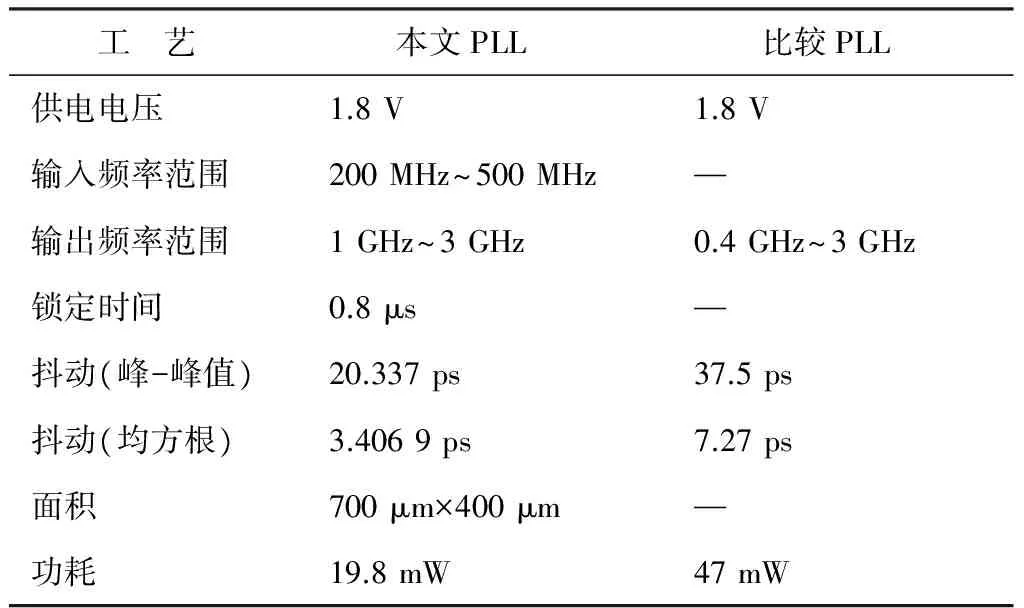

锁相环整体电路的性能概括,及与复旦大学的孙曼同学的论文《2-GHz CMOS锁相环时钟发生器研究与设计》进行比较,见表1。结果显示,所研制的PLL拥有较好的抖动性能。

表1 典型工作频率(2 GHz)的参数对比

4 结 语

在参考传统鉴频鉴相器电路结构的基础上,提出了一种改进型鉴频鉴相器结构,应用到锁相环频率合成器中,实现了低抖动的效果。采用SMIC公司 0.18 μm CMOS工艺完成芯片。版图后仿真结果显示,新电路功能正确、能够有效降低压控振荡器输出抖动,峰-峰值抖动为20.337 ps,输出频率范围为1 GHz~3 GHz。

[1] 黄召军,林武平,李亮,等.一种电荷泵锁相环频率合成器的设计[J].微电子学与计算机,2009,26(5):183-186.

[2] BEHZAD RAZAVi.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2002.

[3] 吕郁.自适应带宽时钟发生器的抖动一致性研究[D].长沙:国防科技大学,2009.

[4] JOHN G MANEATIS.Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques[J].IEEE Solid-State Circuits.1996,31(11):1 723-1 732.

[5] XINTIAN SHI,KILIAN IMFELD,STEVE TANNER,et al.A Low-Jitter and Low-Power CMOS PLL for Clock Multiplication[C]//IEEE Solid-State Circuits Conference.Montreux,2006.

[6] BEHZAD RAZAVI,Challenges in the Design of High-Speed Clock and Data Recovery Circuits[J].IEEE Communication Magazine,2002(8):94-101.

[7] WANLOP SURAKAMPONTORN,CHONBODEECHALERMROONG Y,SUREE BUNJONGJIT.An Analog Sinusoidal Frequency-to-Voltage Converter[J].IEEE Trans.Instrum.Meas.,1991,40(6):925-929.