基于UMV的重构图像扩展算法及VLSI实现

朱胜利,姚素英,徐江涛

ZHU Shengli,YAO Suying,XU Jiangtao

天津大学电子信息工程学院,天津300072

School of Electronic and Information Engineering,Tianjin University,Tianjin 300072,China

1 引言

随着CMOS图像传感器在智能终端中被广泛应用,CMOS图像传感器的视频后处理涵盖的处理技术越来越多,当前很多高集成度的应用处理芯片系统已经将视频编解码也作为CMOS图像传感器系统的视频后处理的重要部分被应用。对于视频编解码技术领域而言,无论新一代视频编解码标准(如H.264、AVS等),还是上一代视频编解码标准(如MPEG-1、MPEG-2等),其中的运动估计和运动补偿都是压缩图像时间冗余的主要方法,也是达到高压缩比所采用的重要技术之一[1-2]。有效运动补偿的基础是获取参考图像宏块的运动向量,一般运动向量范围都限制在已编码的参考帧内,这种限制使对当前帧图像边界宏块进行运动估计时,由于参考宏块可能已在参考帧之外而无法得到最优效果。在运动图像专家组标准MPEG-2以前压缩标准以及国际电信联盟视频编解码标准H.261中都存在因为参考宏块处于参考帧之外而无法进行有效的运动补偿。在H.263、MPEG-4以及中国音视频编解码国家标准AVS1.0中取消了这种限制[3],允许运动向量指向图像以外区域。当视频图像中存在跨边界运动时,这种模式能取得很大编码增益,特别是对小图像和边界运动激烈的图像而言。此外,这种模式允许使用更大运动矢量,对摄像机运动和手机拍摄特别有利。

本文基于采用流水线设计的AVS视频解码器,提出一种新型的基于像素的图像边界扩展算法,对参考帧进行高效的边界扩展。该算法考虑了从视频解码系统角度分析图像数据信息和流水线设计,以及视频解码器存储器开销的优化。确定了图像边界扩展算法在重构帧存储模块实现可以达到边界像素一次扩展、多次使用的高效性。研究了视频解码中的数据信息,通过设计乒乓存储器和FIFO确保在最优缓存设计的基础上实现流水线处理,确保了整个视频解码系统的实时性。从而在运动补偿过程中能够高效地获取无限制运动向量,优化了运动补偿,增强了图像的解码效率。针对本文算法进行了VLSI设计并用Verilog HDL描述,最后给出综合和FPGA测试结果。以往研究中,在实现UMV中没有考虑流水线设计[4]。对基于宏块或者字节进行边界扩展的方法[5],并没考虑算法实现的难度,且对巨大缓存存储器开销也没有充分考虑。本文在充分分析和考虑存储器设计最优的前提下,基于解码器系统流水线设计的思想,在重构帧存储过程中实现了分别基于亮度像素和色度像素的图像边界扩展算法,同时给出了硬件设计及测试,有助于在低成本、高效率地实现UMV方面有更加深入的研究。

2 AVS视频解码器的图像边界扩展系统

AVS视频解码系统是基于我国自主知识产权的国家标准AVS1.0的新一代视频解码系统[3],此系统包括存储控制器、图像变长解码、反量化、反变换、帧内预测、运动补偿、抗块效应滤波、重构帧存储、显示等处理单元(如图1)。基于AVS视频解码器,图像边界扩展系统主要是在重构帧存储模块中实现图像边界扩展算法,相关模块包括环形滤波模块、运动补偿模块和DRAM存储器模块。环形滤波模块提供输入数据,重构帧存储模块将数据进行图像边界扩展,为无限制运动向量的获取奠定了基础,并将数据存储到DRAM存储器模块中,运动补偿模块从DRAM存储器模块中获得实现了无限制运动向量的图像数据进行图像的运动补偿。其中,运动补偿是通过先前图像来预测和补偿当前图像,是减少帧序列冗余信息的有效方法[6-7],而重构帧存储模块将先前图像(参考帧)进行了扩展,然后存储在DRAM中,运动补偿模块从DRAM实时取出所需参考帧,进行补偿运算,然后将当前图像输出给帧内预测模块。将图像边界扩展系统设计在重构帧存储模块中,一次性将参考帧进行扩展并存储在DRAM中,使得运动补偿模块能够多次使用,同时也简化了包括运动补偿、帧内预测等模块的设计,否则每个边界模块到使用无限制运动向量的时候再去扩展并计算,会出现计算的高重复性和对DRAM的访问率的提高,降低了系统的高效性和成本结构。

图1 AVS视频解码系统

3 本文提出的图像边界扩展算法

针对UMV算法和视频解码数据结构进行分析,依据UMV算法要求的数据处理方式和基于流水线的视频解码架构对重构帧存储模块图像扩展的要求,本文提出了高效的图像边界扩展算法。算法从视频解码器系统角度出发,充分分析解码图像数据的结构信息,依据不同图像类型(帧模式、顶场模式、底场模式)和像素不同的位置(图像周边宏块的边界像素和四角顶点像素的扩展)及不同像素类型(亮度(Y)和色度(U和V))进行不同的扩展方式。这些扩展之后的数据依据UMV算法的需求存储到外部存储器中,提供给运动补偿模块所需的运动向量[8-9]。本文算法减少了中间缓存的冗余,保证了视频解码的实时性,为在基于流水线设计的重构帧存储模块实现图像边界像素的实时扩展建立了理论基础。

3.1 UMV算法

在AVS标准里,一个亮度块E和它的相邻亮度8×8块A、B、C和D之间的空间位置如图2所示。亮度块E的大小可以是16×16、16×8、8×16或者8×8。A、B、D都是与E的左上角样本紧邻的块,C是与E的右上角样本紧邻的块。而当前块的运动向量(Motion Vector,MV)计算是按照当前块的类型,从相邻块或者当前块在参考帧中对应块的MV预测出当前块的MV,该MV的预测值即MVP(Motion Vector Prediction),MVP和码流中解出MV的残差MVD(Motion Vector Decrease)相加就是所要的MV[10]。而MVD可以通过数据解析部分从码流中得到,所以在帧间解码中重点是MVP的计算。当A、B、C都是超出图像之外的参考宏块,如此计算的参考帧图像块运动向量就是UMV,同样MVD可以通过数据解析,而UMVP(Unrestricted Motion Vector Prediction)可以通过如下的计算获得[8,11]。分如下三步:

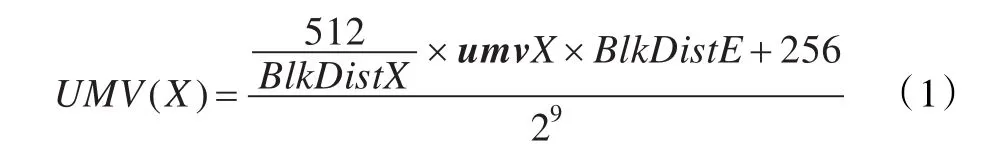

(1)第一步计算UMVA、UMVB和UMVC:

其中,X是变量,表示亮度块E相邻的亮度块A、B和C。umv表示亮度宏块的原始运动向量,对应的BlkDist表示当前块和它的运动向量所指向的参考块之间的距离。式(1)依据AVS-P2标准中对亮度块的运动向量的定义进行总结[3]。

(2)第二步计算两个块运动向量之间的空间距离[12]:

(3)第三步求UMVP:

无限制运动向量的预测值为:

图2 无限制运动矢量示意图

在AVS标准里,如果A、B、C都是超出图像之外的参考宏块,MVA、MVB和MVC都是0,这对图像的运动补偿极为不利,特别是图像边界有激烈运动的图像块。而采用UMV技术可以减少因为运动矢量超界造成的影响,同时也增大了图像块运动向量的值域,完善了运动补偿的效果。

3.2 输入解码图像数据分析

在AVS视频解码的流水线系统中,解码图像是自左向右按照光栅扫描的顺序进行解码。环形滤波模块将解码数据输出到重构帧存储模块前,采用了乒乓存储器将解码数据进行拼接且存储,以提供重构帧存储模块所需要的数据。而重构帧存储模块中的图像边界扩展的算法,主要是依据环形滤波模块提供不同的数据类型进行图像扩展重构存储的,该算法主要是从减少内部存储器的使用和提高解码效率角度考虑。乒乓存储器基于保证宏块级流水线的正常运行进行设计,主要保存的是经过环形滤波之后的数据。下面通过该存储器数据结构分析重构帧存储模块的输入数据。由于乒乓存储器是两个完全相同的存储器进行时序上的乒乓读写,选其中之一进行分析。存储器深度是26 bit,要求能够存储一个亮度和色度宏块的数据(见图3),从0到1存储宏块的上两行亮度数据,从2到9存储宏块Y0、Y1亮度数据,从10到17存储宏块Y2、Y3亮度数据,18存储宏块的上一行色度数据,从19到26存储宏块的色度数据。重构存储模块就是按照Y0、Y1、Y2、Y3、U和V顺序取数进行边界扩展。要求一个存储器读取完成前,另一个存储器宏块数据全部写入。

图3 乒乓存储器数据存储结构

3.3 图像边界扩展的布局和机制

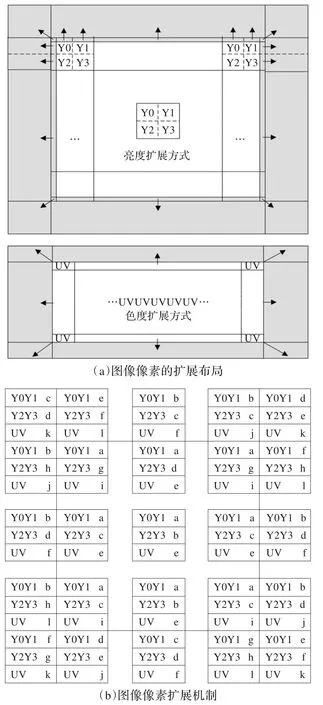

作为参考帧图像的扩展,本文算法首先规定了边界像素扩展的布局和机制。以帧类型的图像边界像素扩展布局(如图4(a))为例,说明宏块边缘像素的亮度和色度的扩展布局。其中亮度数据直接复制边界宏块的边缘像素,复制扩展16个像素单元,但是色度需要进行该宏块边缘像素的U和V交叉之后再进行水平方向复制扩展16个像素单元(8个UV单元),垂直方向复制扩展8个像素单元。图像(包括帧和场)像素扩展机制如图4(b)所示,四角部分的像素扩展顺序按照abcdefghijkl进行处理。周边部分的像素扩展顺序按照abcdef进行处理。图像内部的存储顺序按照abc进行处理。这样的顺序完全是依据环形滤波模块输出的数据特征进行确定,使得不需要内部存储器进行解码数据暂存。

3.4 图像边界扩展算法

图像边界扩展算法考虑数据类型、帧场模式、扩展位置和高效存储等因素,采用高效图像扩展机制,针对图像边界像素的亮度和色度进行图像边界扩展。具体扩展算法如下:

小时候,我常在母亲坐下休息时,给她缯满头的小辫儿。可忘了何时,母亲开始躲我,轰我,不让碰她的头发。有次放学早,回家便看到新奇又心酸的一幕:父亲戴着塑料手套,端着一盘黑糊糊,用牙刷一绺一绺翻腾着母亲的头发刷了又刷。父亲很不自然地说:“你娘头发白了,染染。”知道这个秘密后,我不再碰母亲的头发,看到被染发剂伤得黑中泛黄泛红的头发,心就难受。

图4 图像像素扩展布局及机制

对于帧模式的亮度(如图4(a)),周边处的宏块单元扩充以边缘像素为单位直接向外重复扩充16次;四角处扩充以各角处宏块的角点像素为单位向外重复扩充16×16次。对于顶场模式的亮度,周边处宏块单元扩充以边缘像素为单位直接向外重复扩充16次,但针对场模式在DRAM存储的地址需要跳变:以首行计算地址为准,隔行再进行地址计算,如1357…。四角处的扩充以各角处宏块的角点像素为单位向外重复扩充8×16次。对于底场模式的亮度,周边处的宏块单元扩充以边缘像素为单位直接向外重复扩充16次,但是针对场模式在DRAM存储的地址需要跳变:以首行计算地址为准,隔行再进行地址计算,如2468…。四角处的扩充以各角处宏块的角点像素为单位向外重复扩充8×16次。

对于帧进模式的色度(如图4(a)),在左右方向上分别把U和V的边界像素模块合成以一个U像素和一个V像素为单位整体,分别向左或向右扩展8次。上下方向上把U和V交叉后分别扩充8次;对顶角,把U的角点像素单元和V的角点像素单元合为一体,扩充16×8次。对于顶场进模式的色度,左右方向上分别把U和V的边界像素单元合成以一个U像素单元和一个V像素单元为单位的整体,分别向左或向右扩展8次;在上下方向上把U和V交叉后分别扩充4次。对于顶角,把U的拐角点像素单元和V的顶角点像素单元合为一体,扩充8×8次。对底场进模式的色度,左右方向上分别把U和V的边界像素单元合成以一个U像素单元和一个V像素单元为单位的整体,分别向左或向右扩展8次。上下方向上把U和V交叉后分别扩充4次。对顶角,把U拐角点像素单元和V顶角点像素单元合为一体,扩充8×8次。

4 图像边界扩展系统VLSI设计

基于图像边界扩展算法在AVS视频解码器的重构帧存储模块里进行VLSI设计和实现。重构帧存储模块中,图像边界扩展系统(如图5)进行图像边界扩展,为获得无限制运动向量提供有效参考帧。系统包括变长解码器、环形滤波电路、存储器控制器及动态存储模块以及运动补偿电路[13]。变长解码器通过命令总线和控制总线与重构帧存储模块、运动补偿模块相连接,为图像解码提供图像码流的参数和控制信息。环形滤波电路向重建帧存储电路提供视频解码数据。重构帧存储电路获得图像参数和控制信息以及相应的视频解码数据,实现图像扩展算法的图像扩展,并将相应的视频解码数据存储到DRAM之中。运动补偿模块进行当前帧补偿的时候会从DRAM中取出对应的参考帧,并进行运动矢量的计算,实现完善的运动补偿,最后将实现运动补偿的当前帧数据传输到下一个解码环节。

图5 重构帧存储系统

4.1 基于流水线的存储器设计

基于流水线设计的AVS视频解码系统,要求模块的输入必须采用FIFO同步存储解码数据和图像控制信息,而且要求深度保证两个宏块以上,确保流水处理实时性。本文设计了解码数据存储器和图像控制信息存储器用于重构帧存储模块的输入数据存储。其中图像解码数据存储器和上一级的乒乓存储器按照流水线的级别进行合理对接。

图像解码数据存储器(解码数据FIFO)设计为两个位宽64 bit、深度48的随机存储器(FIFO),主要存储来自环形滤波电路乒乓存储器输出的图像数据,图像数据存储器以宏块为单位将亮度和色度进行存储,并且依据控制信息把64 bit的输入数据转换为128 bit数据。图像控制信息存储器(控制信息FIFO)设计为位宽32 bit、深度8的寄存器数组,主要来自变长解码器输出的存储图像控制信息,输出信息包括:反馈到变长解码器的存储器命令和数据溢出信息、存储图像边界像素扩展模块电路的读数据命令、以及主存储器模块请求、地址及其大小、行、定位和写数据命令。变长解码器发送给重构帧存储电路的是图像控制信号,该控制信号包含的信息有四个命令[3](见表1)。

表1 图像控制信息命令字

图像控制数据信息说明:LEVEL0包含初始化信号,由32位中的0~15位提供DRAM width,从而确定逻辑存储的图像宽度。LEVEL1包含的是图像序列级的信息,其2~13位标志本图像序列中每帧图像的宽度(img_width),14~29位标志本图像序列中每帧图像的高度(img_height)。LEVEL2包含的是帧级信息,其6~25位标志每帧图像的基址。LEVEL3包含的是宏块级信息,其0~6位标志宏块在每帧图像中的纵向相对地址(mb_y),其7~13位标志宏块在每帧图像中的水平方向相对地址(mb_x)。命令数据的30~31位作为图像信息级别的标志位。

4.2 图像边界像素扩展实现

如图5,在图像边界扩展系统中,图像边界扩展电路是核心模块,主要由控制信息FIFO、解码数据FIFO、存储地址计算器、色度交叉排列器、解码图像边界扩展模块等模块组成。图像边界扩展模块电路实现了图像边界扩展算法,工作流程(如图6)从数据输入、图像扩展到数据存储和输出有序进行。解码图像的控制信息存储在控制信息FIFO中,为构建解码图像提供相应图像参数和控制信息,主要是定位图像的相对位置和图像的类

图6 图像边界像素扩展模块电路的工作流程

4.3 二维存储控制器

图像边界扩展系统采用高效的二维存储控制算法,存储方式是每次提供一个行数信号,只计算行数×16 pixel块的首地址,然后存储器的控制器根据首地址和行数,仅在一次对存储器控制器的请求信号的情况下,就可以依次向动态存储器写入行数据,实现二维存储。采用表2的机制进行扩展存储,使得整个硬件设计系统具有较高的数据处理效率并且节省存储空间。一方面,整个图像边界像素扩展处理过程也是向动态存储器存储数据的过程,本文的二维存储是在存储的过程中实现图像扩展,而不是将像素扩展需要的数据存储后再进行扩展,这样就大大节省存储空间。另一方面,只取所用数据进行处理,而不把整个宏块数据取出进行边界像素扩展,减少数据冗余,提高处理数据效率。

4.4 重构帧存储模块电路端口及时序设计

重构帧存储模块电路和变长解码器、环形滤波器及DRAM控制器之间通过控制信号和数据信号进行相连,由于FIFO设计,使得各模块之间的控制信号主要是读/写信号及读/写使能信号以及读/写完成信号。接口设计分为两部分:一方面,与重构帧存储模块输入接口的模块有变长解码器和环形滤波,前者是传送解码图像控制型。解码图像的数据存储在数据FIFO中,为图像扩展提供解码图像数据。依据图像控制信息和图像数据重构了相应图像并进行边界像素扩展。在输入的解码图像数据中,对于亮度Y,直接采用本文3.4节的图像边界扩展算法实现扩展。对于色度U和V,色度交叉排列器将色度U和V进行交叉排列,然后针对边界的像素进行以UV为单位的边界像素模块向外复制扩展,同样也采用本文3.4节的图像边界扩展算法实现扩展。存储地址计算器实时计算出当前图像数据映射到DRAM的地址,同时,解码图像边界扩展模块输出图像数据。DRAM控制器接收到地址和相应的图像数据,将扩展中的图像数据依序存储到DRAM中。运动补偿模块可以从DRAM中取出经过图像边界扩展的参考帧,计算无限制运动向量并进行运动补偿。信息的,而后者是传送解码图像数据码流给重构帧存储模块。另一方面,与重构帧存储模块输出接口的是模块DRAM控制器,主要是把经过图像边界扩展了的解码图像存储到DRAM进行图像重构,以供运动补偿模块计算参考帧运动向量之用。图像边界像素扩展模块的接口如图7所示。

表2 图像边界像素扩展存储算法

图7 图像边界像素扩展模块的接口

采用的时钟是AVS视频解码系统的系统时钟,时钟控制下的时序设计(主要指端口的时序设计)如图8所示。

图8 输入(a)、输出(b)接口信号时序图

输入端口的时序设计(如图8(a)):重构帧存储模块电路先向变长解码器和环形滤波器发出读请求信号,然后等待变长解码器和环形滤波器发出读使能信号,经过若干周期后,当变长解码器和环形滤波器准备好数据可以被读取时,变长解码器和环形滤波器会发出读使能信号,接收到读使能信号后,重构帧存储模块电路开始读取数据。读完数据后,重构帧存储模块电路会发出读完成信号给变长解码器和环形滤波器以示完成读操作。

输出端口的时序设计(如图8(b)):重构帧存储模块电路准备好数据后,先向DRAM控制器发送写请求信号,同时送出写入首地址,然后等待DRAM控制器允许被写时,并DRAM控制器发出写使能信号之后,当前模块开始将数据经DRAM控制器写入DRAM,完成写操作时,DRAM控制器会发送写完成信号给重构帧存储模块电路以示写操作完成,重构帧存储模块电路会停止写操作。

5 实验结论

基于AVS视频解码器的图像边界扩展系统通过仿真后,利用Synopsys公司的DC-FPGA工具进行了FPGA的综合,综合的门级网表经过Xilinx公司的VirtexII XC2V6000系统进行了FPGA验证。本文设计的图像边界扩展系统在AVS解码器中实现了图像边界的有序而高效的扩展,使得运动补偿能够获取无限制运动向量,提高了视频解码效率。

为了比较有UMV和无UMV对视频解码系统的影响,本文引用效率E[14-15]作为衡量依据,E为硬件结构的吞吐率R和实现面积A的比值。

其中,R采用重构帧存储模块输出的平均数率,A是重构帧存储模块的面积。

综合面积结果:采用Synopsys公司的DC_FPGA工具综合,系统时钟为6.7 ns的条件下,打开UMV综合模块面积83 848.562 500门,关闭UMV综合模块面积82 626.432 300门,面积仅增加1.5%。测试的解码效率:实验选用具有代表性的测试序列(如表3),码流1到码流5为同一分辨率下的不同边界运动剧烈程度的码流,码流6到码流10属于同一图像剧烈程度的不同分辨率大小的码流。采用同一AVS编码器对相应的码流序列进行编码。

表4是针对测试选定的10个码流测试的结果,主要是针对打开UMV和关闭UMV的情况,依据公式(4)计算出解码效率,从实验结果看,打开UMV解码器解码效率得到了普遍提高。而对于不同边界运动剧烈程度的图像解码效率和不同分辨率大小的图像解码效率的变化趋势从图9可以看出。很明显,图像边界运动越剧烈,采用UMV后解码效率提高得越多。而对于边界运动一样,图像越小,采用UMV后解码效率提高得越多。

表3 图像扩展系统测试流说明

表4 图像边界扩展系统测试

6 结束语

本文通过分析AVS视频解码系统设计中需要无限制运动向量改善运动补偿,提出了一种高性能的图像边界像素扩展算法,该算法通过硬件实现,在芯片面积增加不大的情况下,有效实现了UMV的获取,从而改善了运动补偿的结果,提高了视频解码系统的解码效率。通过仿真与在FPGA中的验证,证明了本文算法的低成本、高效性以及可实现性,为AVS视频解码系统提高解码效率,特别是小尺寸且图像边界运动剧烈的图像解码,本文选择的码流解码效率提高都在4%以上。同时,值得指出的是本文采用了高效的二维存储机制进行存储图像数据,从而提高了整个系统的存储效率。

图9 图像边界扩展系统提升图像解码效率

[1] Huang A M,Nguyen T.Correlation-based motion vector processing with adaptive interpolation scheme for motioncompensated frame interpolation[J].IEEE Transactions on Image Processing,2009,18(11):740-752.

[2] Li Ming,Chang Yilin,Yang Fuzheng,et al.Rate-distortion criterion based picture padding for arbitrary resolution video coding using H.264/MPEG-4 AVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2010,20(9):1233-1241.

[3] 国家质量监督检验检疫总局.信息技术先进音视频编码第二部分:视频(AVS视频(报批稿))[S].2005.

[4] 张凤.H_263_中高级选项UMV和ADV的研究和实现[J].有线电视技术,2004,160(16):43-46.

[5]张大勇,庄弈琪,汤华莲.MPEG-4中的无限制运动补偿的实现[J].微计算机信息,2008,24(5/3):224-295.

[6] Yang Heechul,Yang Jungyoup,Won Kwanghyun,et al.Motion vector coding with decoder selectable PMV[C]//2010 2nd International Conference on Signal Processing Systems,2010:447-450.

[7] Yokoyama T,Iwasaki T,Watanabe T.Motion vector based moving object detection and tracking in the MPEG compressed domain[C]//2009 Seventh International Workshop on Content-Based Multimedia Indexing,2009.

[8] Zheng Junhao,Deng Lei,Zhang Peng,et al.An efficient VLSI architecture for motion compensation of AVS HDTV decoder[J].J Comput Sci&Technol,2006,21(3):370-377.

[9] 赵建全,张卫宁,袁鲲,等.AVS视频硬件解码器运动补偿单元的设计[J].电气电子教学学报,2008,30(6):21-24.

[10] 龚声蓉,郭丽,韩军,等.基于全局运动补偿编码的AVS编码器设计[J].通信学报,2007,28(10):102-108.

[11] Laroche G,Jung J,Pesquent-Popescu B.RD optimized codingformotionvectorpredictorselection[J].IEEE Trans on Circuit and Syst for Video Tech,2008,18(12):1247-1257.

[12] Rye S N,Sang L G.Error concealment in H.264 considering direction and distance of motion vectors[J].Korea Inf Comm Soc,2009,34(1):34-47.

[13] 刘龙,韩崇昭,王占辉.MPEG-4运动补偿的VLSI结构设计[J].通信学报,2005,26(11).

[14] 邓磊,高文,胡铭曾,等.基于AVC/AVS标准高效运动估计硬件结构设计[J].计算机研究与发展,2006,43(11):1972-1979.

[15] Pirsch P,Gehrke1 W.VLSI architectures for video compression[C]//Proc of the 1995 IEEE Int,1995:220-246.