本安型四路数字视频光端机的设计

汪 涵

(常州信息职业技术学院 江苏常州 213164)

0 引言

本文介绍的视频光端机具有本质安全型特性,主要应用在有防爆要求的场合,如煤矿、石油、化工等。现有的数字视频光端机技术和产品大多数都是定位在普通环境中使用,不能在宜爆场合直接使用。目前多数厂家把普通的视频光端机装入防爆箱内,作为隔爆型光端机,但这样的方案成本非常昂贵。本文设计的光端机由于采用本安电路技术,不需要再装入笨重的防爆箱内,体积和重量都比隔爆型光端机优越,大大降低了运输、安装、调试和后期维护成本,具有较好的市场应用前景。

1 光端机总体设计方案

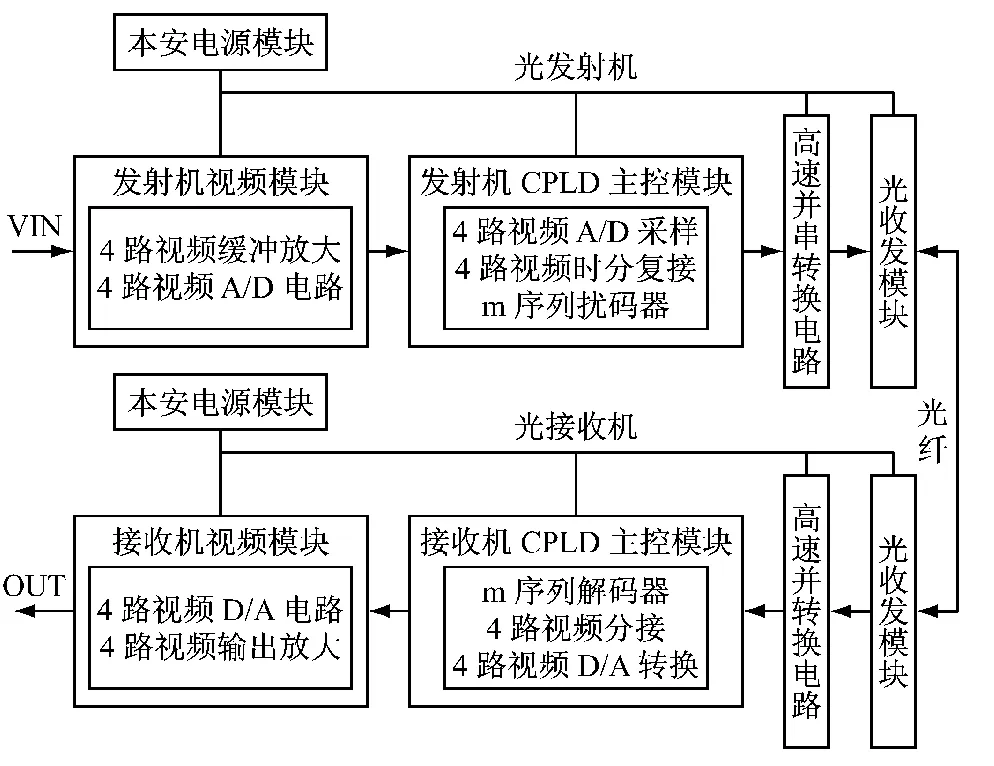

本设计的视频光端机硬件电路符合本安电路的设计要求。光端机主要包括光发射机和光接收机两部分。图1为光端机总体设计框图。

光发射机首先将4路模拟视频基带信号进行模数转换变为数字信号,并将4路视频数字信号进行复用,形成高速数字信号,然后对高速的并行数据进行m序列扰码器处理,使其更适合光纤传输,再利用并串模块把编码后的并行数据转换为更高速的串行数据,最后通过光发射模块把高速的电信号转换成光信号并进行发射;光接收机中的光接收模块首先将光信号转换成电信号,再利用串并转换模块将高速的串行数据转换为并行数据,然后对高速的并行数据进行m序列解码器处理,并对数字信号进行分解,恢复出各路低速的数字视频信号,最后通过数字/模拟转换电路恢复成模拟视频信号。本设计光端机硬件按照本质安全电路的要求设计,可以直接应用在有防爆要求的场合。

图1 光端机总体设计框图

2 本安电源模块设计

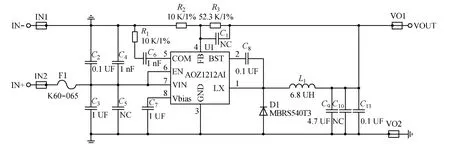

本安型视频光端机电路上要满足本安要求最关键的设计是电源部分要实现本安特性,而且光端机的输入供电电源也必须是本质安全型电源。本设计选择的输入电源为DC12V本安电源,DC12V输出的本安电源主要参数为:①最大输出电压Uo:12.5 V;②最大输出电流Io:1.3 A;③最大外部电感Lo:0.1 mH;④最大外部电容Co:22 μF。从上述主要参数可以看出DC12V输出的本安电源的带容性器件的能力比较弱。本设计系统内部电路中需要5 V和3.3 V两种电压等级,所以采用了开关降压型本质安全型电源设计技术。系统电源部分主要采用DC-DC电源控制芯片AOZ1212AI和线性电源芯片AMS1117-3.3。芯片AOZ1212AI为整个电路提供5 V电源,满足系统5 V的供电要求。图2为DC12V转DC5V的本质安全型电源电路。

图2 DC12V转DC5V的本质安全型电源电路

电源控制芯片AOZ1212AI是非隔离降压型开关电源控制芯片,具有较宽的电压输入范围(DC4.5 V-DC27 V),370 kHz的开关频率。根据DC12V本安电源的负载特性要求,本设计AOZ1212AI的输入和输出电容的和不能超过22 uF,最大电感不能超过0.1 mH,故本设计采用C3(1 uF)作为 AOZ1212AI的输入电容,C9(4.7 uF)作为AOZ1212AI的 输 出 电 容,L1(6.8 uH)作 为AOZ1212AI的滤波电感。本设计的整机功耗小于3 w满足本安产品的要求。

3 光端机CPLD主控模块设计

光端机CPLD主控模块主要功能包括光端机发送端实现4路视频信号的AD采集、4路视频信号时分复接、m序列扰码器;光端机接收端实现m序列解码器、4路视频信号的分接、DA转换。

3.1 4路视频信号的A/D、D/A转换

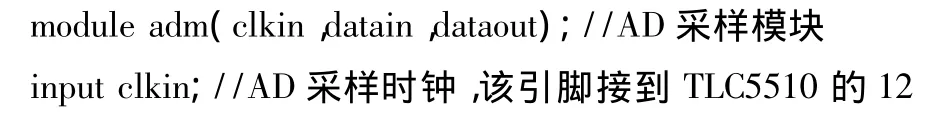

光端机发送端A/D转换芯片采用的是TLC5510,TLC5510是8位半闪速结构模数转换器,一个TLC5510完成一路模拟视频信号的A/D转换[1]。光端机接收端得到数字视频信号后需要D/A模块转换为模拟视频信号,设计中采用跟A/D芯片TLC5510配对的TLC5602作为D/A芯片。根据TLC5510的时序,本设计编写如下单路视频A/D采样Verilog程序:

本设计要同时采集4路的视频信号,所以采用了4片独立的TLC5510芯片,每个芯片各自完成一路视频的A/D转换。CPLD主控模块同时采集4路视频数字信号,并按照时间的先后顺序送入4路视频复接模块。

3.2 光端机4路视频信号的复分接

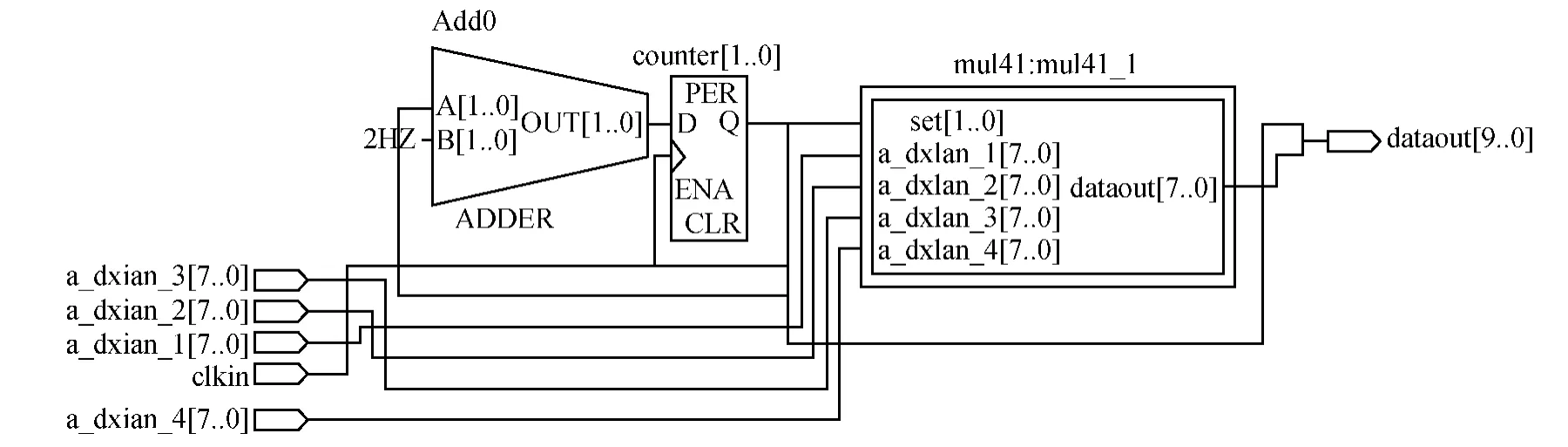

本设计用到的复分接技术是时分复用TDM(Time Division Multiplexing)[2],时分多路复用以时间作为信号分割的参量,故必须使各路信号在时间轴上互不重叠。本设计中共有4路视频信号,每路信号的传输率为12.5 M字节。本设计将整个物理信道分为4个时隙,每个时隙由10位构成,其中8位为视频数字信号,2位循环计数用来进行时隙区分,4路视频信号将一直占用各自的时隙,不存在空闲的时隙。信号复接功能主要是由光端机发送端主控模块CPLD中生成的一个4选1的数据选择器mul41_1(counter[1:0],dataout[7:0],a_dxian_1,a_dxian_2,a_dxian_3,a_dxian_4)来完成,其中 counter[1:0]为2位循环计数器作为选择器的选择控制信号,dataout[7:0]为选择器的输出端作为信号复接后的输出,a_dxian_1,a_dxian_2,a_dxian_3,a_dxian_4为选择器的输入端作为需要复接的四路视频信号。4路视频信号的复接模块经QuartusⅡ综合后生成的RTL图如图3所示。

图3 4路视频信号的复接模块RTL图

3.3 光端机m序列扰/解码器

由于模拟视频信号具有一定的规律,所以数字化采样后的原码并不适合直接进行光纤传输。例如:当数据信息出现较长的连“0”码或者连“1”码时将会影响接收端位定时信息的恢复质量,造成抽样判决时刻发生变化,对系统的误码率产生影响,甚至有可能接收全错的信息。采用有冗余的传输编码可以消除数据源一部分信息模式对系统性能的影响,但是要以减少有效数据传输速率为代价,而且复杂的线路编码会增加系统的硬件成本。在本设计中使用m序列串行扰码器将数据源变成近似于白噪声的数据序列,以增加定时的同步信息,消除信息模式对系统误码的影响。本设计的光发射机在数字信号进入并串芯片lv1023之前,在CPLD中设计一个扰码器[3],将二进制视频原码序列加以变换,使其接近于随机序列。相应的,在光端机接收端CPLD中设计一个解扰码器,以恢复原始序列。1位m序列扰码器经QuartusⅡ综合后生成的RTL图如图4。

图4 1位m序列扰码器RTL图

4 基本功能测量

多次实验结果表明:本设计光端机工作稳定,图像清晰,实时传输效果好,多路视频同时传输时无互扰现象发生,表1是检测结果的关键参数。

表1 关键参数

5 结束语

本论文主要完成了本安型4路视频数字光端机的设计,实现了4路模拟视频信号在单芯光纤中的数字化传输。在实验室中测试,图像信息传输非常稳定,通过电视观测到的彩色信号发生器发出的视频信号经过本光端机传输后图象依旧非常清晰,本设计主要完成了以下工作:①本设计光端机硬件按照本质安全电路的要求设计,可以直接应用在有防爆要求的场合;②详细分析了数字复分接技术的基本原理和实现方法,利用Verilog语言完成了4路视频数字信号的复分接程序设计;③在主控CPLD芯片中用简单的串型扰码器代替复杂的线路编解码电路,降低了光端机的成本。

[1]温智宁,管自新.基于TLC5510的数据采集系统设计[J].国外电子元器件,2008(5):22.

[2]徐旭.基于LVDS技术的数字光端机设计[D].长春:吉林大学,2009:6.

[3]基晓华.基于FPGA的数字视频监控系统的研究与设计[D].武汉:武汉理工大学,2009:16.

- 常州信息职业技术学院学报的其它文章

- 可编程控制器在数控车床自动上料机械手中的应用