高分辨率全帧CCD高速驱动设计

唐亚军 , 郭喜庆 , 余 锦 , 朱 涵 , 杨敬娴

(1.中国科学院 光电研究院,北京 100094;2.中国科学院大学 北京 100090)

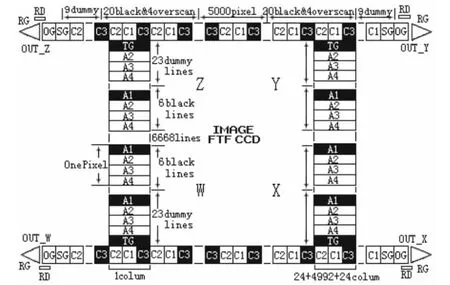

随着航空遥感相机应用水平的不断提高,其对有效载荷和数据处理速度提出了越来越高的要求。全帧CCD作为高灵敏度图像传感器,分辨率高、感光面积大,广泛应用于航空遥感。但因其像素高、帧频低,无法满足高速航拍的需求[1]。加之传统的专用集成驱动设计的可配置灵活性低,应用范围受到限制。因此,关于高分辨率、高灵活性的高速CCD驱动的设计具有实质性意义。本文以FPGA作为CCD驱动时序产生的核心单元,以FTF5066M为例,完成了全帧CCD的高速驱动的设计。结构图[2]如图1所示。光敏区四角嵌入了MOS单元,构成4个输出放大器。MOS单元上包括实现像素拼接的加法门SG,输出门OG控制光生电荷有序输出。光生电荷在四相垂直行驱动脉冲A和传输门TG的控制下,将电荷转移到水平移位输出寄存器中。三相水平驱动脉冲C驱动输出寄存器中的光生电荷有序地输入到输出放大器中。

1 FTF5066M结构

FTF5066M是一款具有33 M像素的高分辨率全帧CCD图像传感器。由光敏区和上下水平移位输出寄存器组成。光敏区包括X、Y、Z、W象限,每行5 040像素,包含有效像素4 992个、过渡像素8个、黑像素40个;每列包括6 726个像素行,有效像素6 668行、黑像素12行、哑像素46行。其内部

图1 FTF5066M内部结构图Fig.1 FTF5066M internal structure

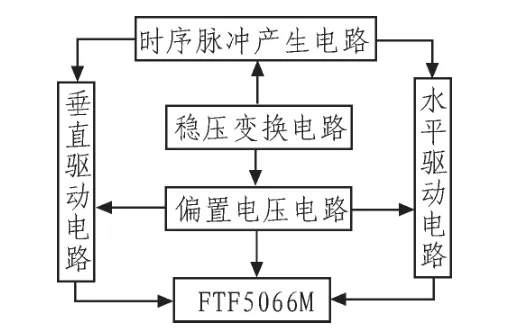

2 硬件电路设计

FTF5066M驱动电路包括稳压变换电路、偏置电压电路、驱动脉冲产生电路、垂直水平驱动电路[3]。本文以逻辑门阵列FPGA为驱动时序脉冲产生电路的核心,采用分离元件,结合FTF5066M四输出通道结构特点进行了高速驱动电路设计。驱动电路组成结构如图2所示。

图2 FTF5066M驱动电路框图Fig.2 FTF5066M driven circuit diagram

2.1 稳压变换电路

LM317是一款具有过载保护功能的正三端可调稳压器,输出电压范围1.2 V到37 V。线性调整率高达0.01%,能充分满足CCD时序脉冲电路和偏置电路的电压稳定性要求[4],如图3所示。

图3 稳压变换电路Fig.3 Voltage conversion circuit

旁路电容C2和电解电容C1抑制纹波对输出电压的干扰。去耦电容C3提高了变换电路的瞬态响应,取值1 μF到1 000 μF。D1可抑制断电时 C3对 LM317的冲击。LM317在输出端Vout和调整端ADJ间保持1.25 V稳定电压,调整R2输出可控电压:

当 1 A≥Iout≥10 mA,IADJ≤5 μA。 因此当输出电流大于10 mA时,可忽略IADJ对Vout的影响。在满足LM317的最小稳定工作电流1.5 mA条件下,图3中的参数实现了1.2 V到27 V输出电压要求。

2.2 偏置电压电路

正确的偏置电压是FTF5066M正常工作的必要条件,各偏置电压需要满足以下要求[5-6]。

VNS:N型衬底电压,20 V到28 V。VNS越大CCD抗晕能力越强;反之动态范围越广。根据航拍相机对高动态范围要求[7],暂取 20 V。

VPS:P型衬底电压,典型值6 V。

VSFD:源级跟随器漏极电压,该电压是跟随器工作电压,典型值20 V。

VRD:漏极复位电压,典型值20 V。

RG:栅极复位电压,其值为CCD输出信号复位电压水平,取20 V。

SG:加法门电压,典型值4 V。

VOG:输出门栅极电压,取6.5 V。

VSFD和VNS取自稳压变换电路的输出,其它偏置电压利用分压电阻由VSFD分压得到。

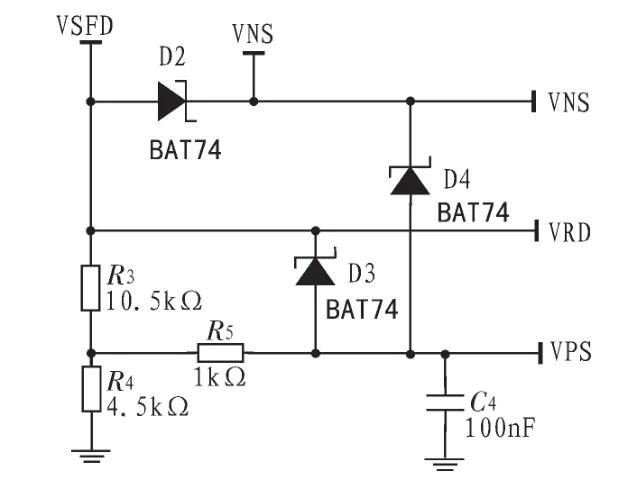

FTF5066M的输出寄存器极其脆弱,其4个偏置电压需满足安全的上电顺序 (下电顺序相反):VNS、VSFD、VRD、VPS,且 VPS不能先于 VSFD、VRD到达芯片管脚。利用BAT74反向截止特性,偏置电压保护电路如图4所示。满足了VSFD和VRD电压差不超过5 V,VSFD不大于VNS的要求。FTF5066M易受到静电放电损坏,须确保VPS小于VSFD和VRD,保证VRD不高于VSFD电压。

图4 偏置电压保护电路Fig.4 Bias voltage protection circuit

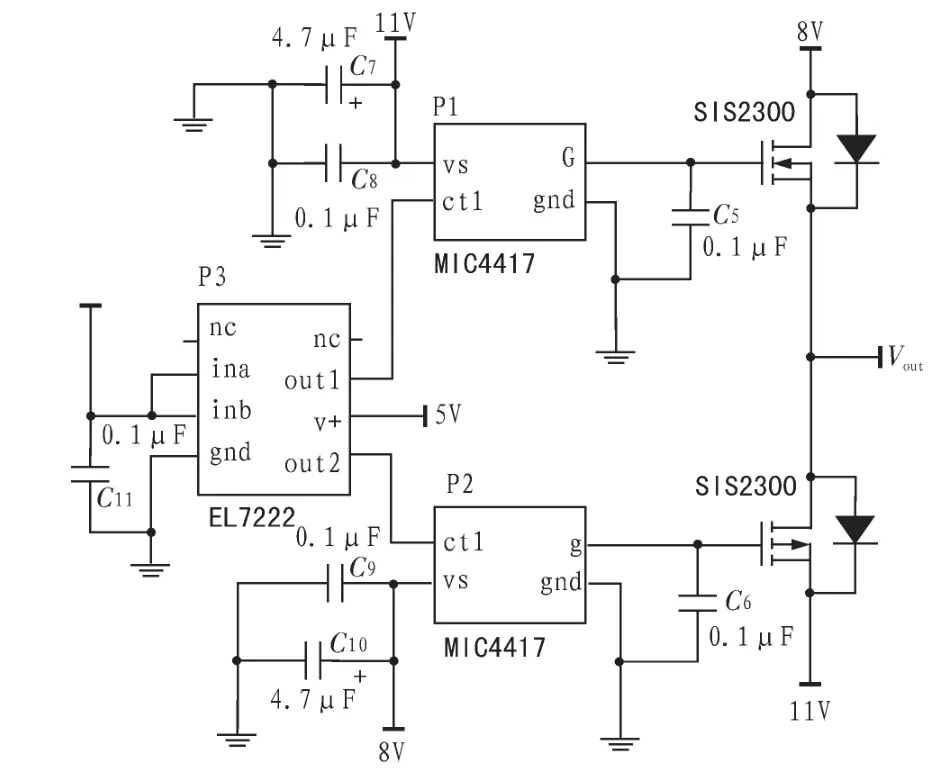

2.3 驱动电路

四相垂直行转移脉冲A转移状态时高电平11 V;光积分状态时高电平8 V。因此,转移脉冲的高电平需根据CCD工作状态进行选择。本文将N沟道和P沟道MOSFET的漏极串接作为输出端,设计了高电平选择电路,如图5所示。图中MIC4417起到开关作用,MIC4417的VS端分别接入电压11 V和8 V,实现了SIS2300的栅源电压VGS>0,SIS2301的VGS<0开通条件。EL7222将FPGA信号输出电平转换成TTL电平,完成与MIC4417的连接。out1端电压与ina同相,out2端电压与inb反向。因此,ina与inb的短接实现了两MIC4417交替开通。从而使得两MOSFET在Vin控制下交替导通完成脉冲A的高电平在11 V和8 V之间的转换。

时序脉冲产生电路核心器件FPGA的IO扇出系数小、驱动能力小,产生的驱动脉冲信号无法直接驱动CCD完成光生电荷转移。驱动电路需将FPGA产生的驱动时钟信号进行功率放大,以满足CCD对驱动电压和电流以及时序的要求[3]。

EL7202是一款具有2 A峰值驱动电流高速时钟驱动器,最大输出电压16.5 V。负载电容1 000 pF时,上升时间tR和tF下降时间均不超过20 ns,足够满足四项垂直驱动脉冲A和传输门时钟TG的功率放大要求。

图5 垂直行驱动脉冲高电平选择电路Fig.5 High level selection circuit of vertical pulse

FTF5066M的三相水平像素驱动脉冲C、加法时钟信号SG和复位时钟信号RG共同实现光生电荷的水平转移。读出频率高达25 MHz,驱动器应具有更短的上升时间和下降时间,以满足水平驱动脉冲瞬态响应的要求。74AC04是一款六驱动先进高速CMOS驱动器,最大输出电压为6 V,典型瞬态传播延迟时间tPD为4 ns,满足CCD对水平驱动脉冲信号的电压和时间特性要求。

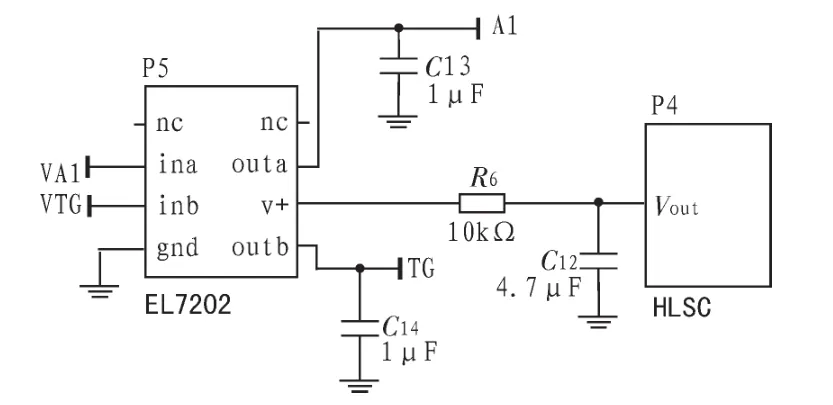

结合FTF5066M的时序脉冲驱动信号的特点,图6以A1、TG为例设计了垂直驱动电路,电荷复位信号CR的驱动电路应在V+端接入+5 V电压,这样才能达到CR的变化幅值为5 V。其他信号直接接入高电平选择电路HLSC(图5)的Vout端,R6和C12用于防止过冲,去耦电容应尽量靠近管脚。图7设计了水平驱动电路,图中电阻和稳压二极管并联后与电容串联构成了正电压钳位电路。注意在满足稳压二极管钳位值条件下,需保证钳位电路的时间常数τ大于5Tc,其中τ=RC,Tc表示水平驱动时钟周期。否则驱动信号将产生严重失真,出现尖锐脉冲。

图6 垂直驱动电路Fig.6 Vertical driven circuit

2.4 时序脉冲产生电路

时序脉冲产生器件FPGA集成度高、速度快、可配置型好,非常适合CCD驱动的设计。目前关于FPGA外围电路的设计已有很多资料,可参考文献[8]。实验阶段,本文采用Altera公司EP1C12型FPGA作为驱动脉冲产生电路核心器件。速度等级-8时,锁相环最低行列时钟输出频率275 MHz(晶振频率15.625 MHz),能充分满足FTF5066M全帧CCD驱动电路对时序频率的要求[9]。因此,可将FPGA的IO端口与前面所设计的驱动电路的相应接口连接,产生12路行列时序脉冲,其中包括垂直驱动时钟高电平选择电路的控制时钟Vin。

图7 水平驱动电路Fig.7 Horizontal driven circuit

3 时序设计与仿真

3.1 FTF5066M驱动时序分析

CCD完成积分后,垂直行转移脉冲将帧图像逐行转移到水平移位输出寄存器中。FTF5066M的帧转移时序见文献2的图5。

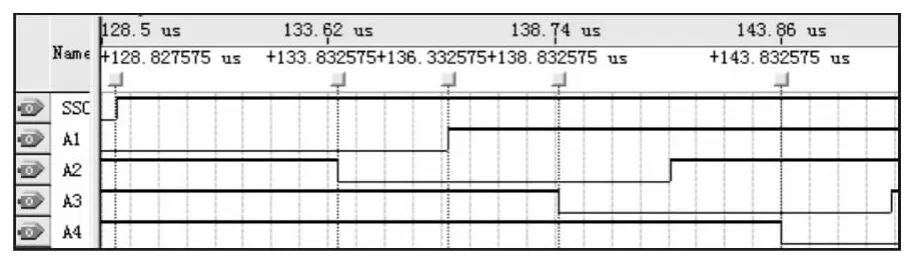

帧转移时序分为三阶段。FTF5066M首先进入光积分阶段,光积分结束后进入帧转移阶段,最后进入空闲阶段。SSC是系统基准时钟,CR为CCD电荷复位信号,与VNC耦合共同实现光生电荷的复位。外部触发信号Trig上升沿后的第一个SSC脉冲上升沿触发CR信号,CCD进入积分阶段;Trig下降沿触发帧转移的开始,下降沿后的SSC第一个上升沿触发VA高电平,用于控制四相A时钟高电平的转换。空闲阶段A时钟均保持低电平,积分阶段A2、A3、A4变为高电平,A1的低电平实现像素的阻隔。帧转移阶段,SSC高电平阶段进行垂直行转移,低电平阶段完成水平光生电荷的转移,三相水平驱动脉冲C驱动将光生电荷逐个转移到输出寄存器中,SSC的上升沿由C2的上升沿触发。

3.2 FTF5066M驱动时序设计

目前基于全帧CCD的相机大多采用单通道输出方式,帧频不超过1 fps,难以满足高帧频应用要求。特别是大面阵CCD,帧频就更低。本文结合FTF5066M光敏区四通道可输出的结构特点,设计了四通道并行输出时序驱动。为使光生电荷分别向4个通道移动,需将X、Y、Z、W 4个象限的水平和垂直驱动信号按照一定顺序组合为统一的驱动信号。图8中实线表示光生电荷流动方向,黑框外的信号表示与FPGA的统一接口。该方法设计的驱动时序,仅需3363次垂直转移和2529次水平转移,而单端输出需分别6 703次和5 049次转移。

3.3 实验结果及分析

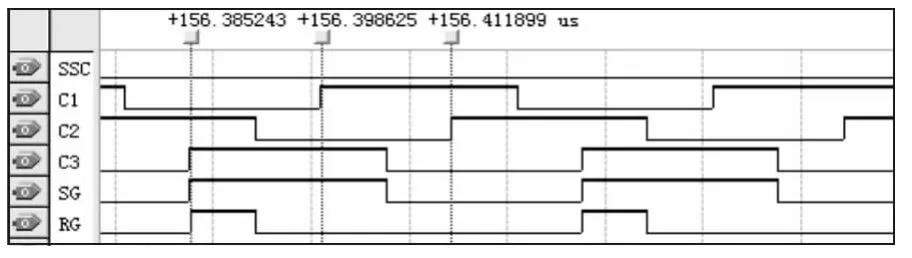

本文采用Quartus II进行FTF5066M驱动时序设计。实验仿真中,EP1C12采用50M的外部晶振。FTF5066M的复位门时钟RG的高电平保持时间是所有驱动信号中最小时间单位 (倍频时钟C_ss的时钟周期),帧转移时序仿真如图9所示。图中C_ss信号是外部晶振Cin通过锁相环PLL三倍频获得的150M最小基本时钟。Trig信号触发计数器产生系统基准时钟SSC,同时通过该计数器产生垂直四相转移时钟。采用分割法将水平驱动信号6等分,在SSC下降沿的触发下,利用状态机产生三相水平转移时钟、RG及SG信号的输出。关于垂直转移时钟和水平转移时钟的相位关系如图10、图11所示。

图8 FTF5066驱动信号分配图Fig.8 Drive signal distribution diagram of FTF5066M

图9 帧转移时序图Fig.9 Frame transfer sequence diagram

图10 垂直转移时钟相位图Fig.10 Vertical transfer phase diagram

图11 水平转移时钟相位图Fig.11 Horizontal transfer phase diagram

以系统基准时钟SSC为参考标准,图10所测时间值的垂直转移时钟绝对相位误差不大于5 ns;以加法门时钟SG为参考标准,图11中水平转移时钟的绝对相位误差不超过0.05 ns,充分满足FTF5066M的工作时序要求[2]。在25 MHz的水平时钟频率四通道输出模式下,水平转移时间为:th=2 529 ×40 ns=101.16 μs, 而行转移时间采用了典型值[2]27.5 μs。在30 ms的积分时间条件下,实现了2.161 3 fps的快速帧频,与单通道输出速率0.7 fps相比[2],大幅度提高了航空遥感相机拍摄速度。

实验中,驱动电路在30 s时间内获得了64帧采集图像,接近2.161 3 fps×30 s=64.8帧的理论计算值。30 s定时试验中由于帧结束信号未收到,最后0.8帧图像未被写入帧存储区。图12是FTF5066M利用上述驱动电路所获的四路并行输出合成图。由于FTF5066M的4个输出放大器增益误差和随机噪声的存在,X、Y、Z、W四象限的边界出现了细微灰度差,可在后续图像处理中通过滤波和灰度变换[10]得到正确的采集图像。

图12 TFT5066M四路并行输出图Fig.12 FTF5066M four parallel output diagram

4 结 论

采用FPGA作为时序发生器,利用分离器件设计的高分辨率全帧CCD驱动电路在实验中能产生正确的驱动信号和偏置电压,并得到了成功应用。利用FTF5066M的结构优势设计的配置灵活的四通道并行输出高速驱动,提高了全帧CCD的帧频,为高速航空遥感相机的设计打下了良好的基础。但在是四通道并行输出方式应用中,图像象限边界出现了细微的灰度差,这对后期PCB电路的结构优化设计和图像处理提出了新的挑战。

[1]米本和也.CCD/CMOS图像传感器基础与应用[M].北京:科学出版社,2011.

[2]DALSA.FTF5066M 33M Full-Frame CCD Image Sensor[M].Canada:DALSA Corporation,2008:2-16.

[3]侯新梅,李自田,胡炳樑.基于FPGA的面阵CCD驱动电路的设计[J].电子应用技术,2010,7(318):195-197.HOU Xin-mei, Li Zi-tian, Hu Bing-liang.Design of area CCD drivercircuitbased on FPGA[J].Application of Electronic Technique, 2010, 7(318):195-197.

[4]National Semiconductor.LM317 3-Terminal Adjustable Regulator[M].America:National Semiconductor Corporation,1996:1-12.

[5]DALSA.Application Note AN14[M].Canada:DALSA Corporation,2009:24-35.

[6]ZHANG Ming-yu,REN Jian-yue.Design of Driving Circuit for Binocular CCD Image System [C]//International Symposium on Advanced Optical Manufacturer and Testing Technology, Dalia:Chinese Optical Society,2010:215-222.

[7]李智勇,杨校军.关于遥感卫星TDI CCD相机动态范围设计的思考[J].航天返回与遥感,2011,32(1):24-25.LI Zhi-yong,YANG Xiao-jun.Insights on design of dynamic range of remote sensing satellite TDI CCD camera[J].Spacecrafr Recovery&Remote Sensing, 2011,32(1):24-25.

[8]姚远,李辰.FPGA应用开发入门典型实例[M].北京:人民邮电出版社,2010:10-29.

[9]Altera.Cyclone FPGA Family Datasheet[M].America:Altera Corporation,2005:17-30.

[10]冈萨雷斯,阮秋琦,阮宇智等.数字图像处理[M].3版.北京:电子工业出版社,2011.