数字音频D类功放电源误差校正方法研究

袁永金,樊养余,于泽琦,吕国云,史龙飞

(西北工业大学 陕西 西安 710127)

随着电子设备日益向小型化、便携化方向发展,功耗成为设计需要考虑的重要问题,为此,对电子设备效率提出了更高的要求。传统的A类,B类和AB类线性音频功放最多只能达到50%的电源效率,而音频D类功放只让功率晶体管工作在开关状态,其电源效率理论上可达100%。在实际应用中,虽然功率放大级还会存在一定的电能消耗,但其效率依然可达到80%~90%[1],因而具有广泛的应用前景。音频D类功放功率级利用功率晶体管的开关特性放大信号,这使得其电源效率远远高于传统线性功放,但是在功率晶体管放大信号的同时,功率级供电电源所包含的噪声、纹波会使功率级输出信号发生失真,从而使功放性能大大降低。因此,校正功率级电源噪声引起的误差,提高音频D类功放的输出性能,成为众多研究者的研究目标。为了解决功率级电源噪声和谐波所产生的误差,许多研究者提出了不同的方案,J.Tol等人采用对系统加入两个高带宽ADC来对功率级的输出信号分压后进行模数转换,然后设计一个数字控制器把系统输入信号和功率级输出信号进行比较,从而校正功率级误差[2];Miguel Angel Rojas-Gonzalez等人采用双闭环反馈校正功率级电源误差[3];P. T. Krein等人在数字PWM发生器和BBM模块之间加入模拟比较器,通过比较BBM模块的输入和功率级的输出调整模拟比较器的阈值对误差进行校正[4];Pallab Midya等人则采用将功率管输出信号与数字PWM信号比较后的差值进行A/D转换,转换结果引入PWM误差校正模块完成对功率管输入信号的校正[5]。在这些校正方法中,模拟器件较多,设计复杂,大多应用于传统D类功放,同时时序的有效匹配也是制约校正性能的重要因素。

随着各领域数字化程度的不断加深,越来越多的音源采用数字音源,高效率、低损耗,可以直接放大数字音源的数字音频D类功率放大器日益受到人们的关注。因此,本文结合数字音频D类功放核心控制IP提出一种基于FPGA的数字音频D类功放电源误差校正方法,实现对电源误差的实时在线校正,有效提高数字音频D类功放的性能。

1 电源噪声对数字音频D类功放影响分析

数字音频D类功放利用功率晶体管的开关特性放大调制的二值连续时间信号,当功率晶体管关闭时,输出为0电平,当功率晶体管开启时,输出为功率级供电电平VDD,若 为理想电源,功率晶体管输出信号为理想PWM波,然而在实际应用中,所使用的电源往往由工频交流电变压之后整流、滤波得到,其不可避免的含有工频50 Hz的噪声与谐波噪声。这些噪声使得功率晶体管的输出高电平不再是稳定的 ,从而在音频频段内引入噪声,降低了数字音频D类功放的整体性能。

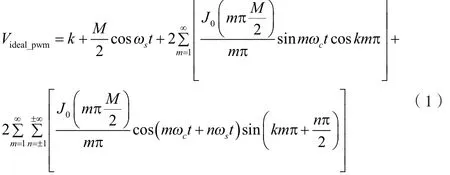

根据已有的PWM信号数学模型[6],理想PWM调制信号可以表示为:

其中 表示静态偏置,M表示调制系数, ws表示输入信号的角频率,wc表示载波的角频率, Jn()表示n阶第一类贝塞尔函数。

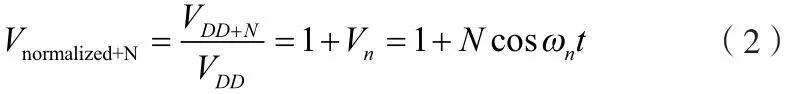

对于功率级供电电源,可以将其视为理想供电电源与电源噪声的叠加。实际的供电电源VDD+N可以归一化表示为:

其中VDD为理想的功率级供电电源, Vn为归一化的电源噪声,wn为电源噪声的频率,N为电源噪声的归一化幅度。由于Vn的影响,通过功率级的信号将会产生误差。

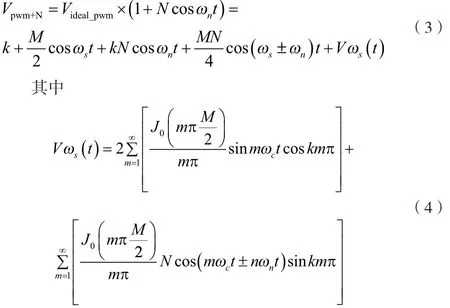

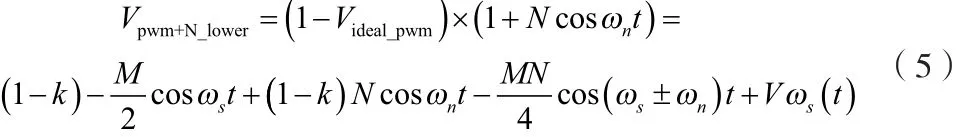

添加噪声之后的PWM信号可以表示为[7]:

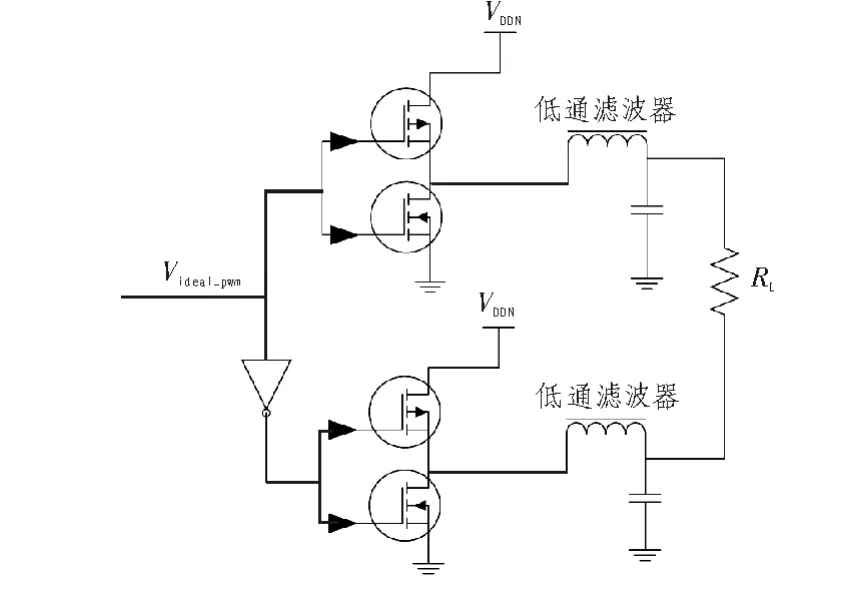

在实际应用中,音频D类功放功率级形式有半桥与全桥两种形式,相对于半桥形式功率级,全桥形式的功率级的效率更高,电源抑制比(Power Supply Rejection Ratio,PSRR)较好,因此使用较为广泛,文中数字音频D类功放系统同样采用全桥形式功率级,其结构原理图如图1所示。

由图可见,上半桥臂的输出信号 VPWM+N_upper=VPWM+N,下半桥臂的输出信号可以表示为:

图1 全桥形式功率级结构原理图Fig. 1 Full-bridge power stage structure diagram

因此,全桥功率级的输出信号可以表示为:

其中第一部分为静态偏置,第二部分为输入信号,第三部分电源噪声部分,第四部分与互调失真(Inter Modulation Distortion,IMD)有关,最后一部分与载频相关,一般为高于192 kHz的频率成分,在通过低通滤波器时会被滤除,因此分析时最后一部分不予考虑。

理想情况下 ,k=0.5静态偏置与低频电源噪声消失,输出信号只存在互调失真,当然,在实际应用中,上下半桥臂k值不会都精确为0.5,静态偏置与低频电源噪声依然存在,但是均能被抑制在较低的水平上。

2 基于FPGA的数字音频D类功放电源误差校正模块实现

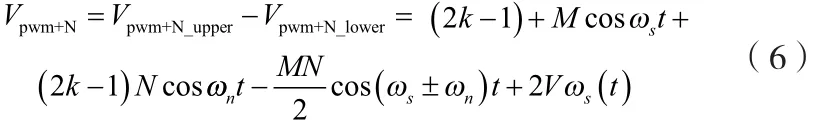

为了对电源误差进行校正,本文采用预校正的方法,在对输入信号进行调制之前,根据当前功率级供电电源噪声大小,调整输入数据,调制放大之后将互调失真部分抵消,从而达到对功率级输出信号电源误差的校正。

基于现有数字音频D类功放系统,将当前功率级供电电源噪声实时返回到数字音频D类功放的核心控制部分,处理后得到当前电源噪声所对应的输入变化值,在Sigma-Delta调制器输入端实时减去电源噪声引起的输入变化值,完成对电源误差的校正。

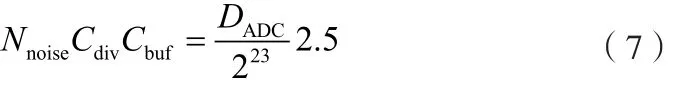

数字音频D类功放电源误差校正模块按照所实现的功能可以分为电源噪声反馈模块与电源噪声数据处理模块两部分组成。其中电源噪声反馈模块的功能为将功率级当前供电电源噪声提取放大后,由ADC电路转化为数字量反馈到数字音频D类功放核心控制模块;电源噪声数据处理模块的功能为根据电源噪声反馈数据实时校正Sigma-Delta调制器输入,对功率级电源误差进行预校正,抑制电源噪声对系统性能的影响。电源误差实时校正的数字音频D类功放系统框图如图2所示,实物图如图3所示。

2.1 电源噪声反馈模块的设计与实现

图2 电源误差实时校正的数字音频D类功放系统框图Fig. 2 Digital audio class-D amplifier system with power supply noise real-time correction block diagram

图3 数字音频D类功放板级系统Fig. 3 The board-level system of digital audio class-D amplifier

电源噪声反馈模块的基本实现原理为:使用精密可调电阻与2 kΩ电阻对功率级供电电压进行分压,分压信号缓冲后送至ADC,ADC的输出作为电源噪声反馈至FPGA核心模块。缓冲电路的作用为对分压信号使用运放进行跟随和二倍放大处理,即可得到一对与单路分压信号等效的差分信号,然后将其隔直、设定静态偏置后送入ADC差分输入端,以便ADC进行处理。由于对分压信号进行了二倍放大处理,为使分压信号始终处于运放工作电压范围之内(0~5 V),将分压值设定为1.75 V,其二倍放大值为3.5 V,可以正常反馈的电源噪声电压峰值为 ,远大于可能的电源噪声电压绝对值,同时可使运放工作于最佳工作电压范围。

2.2 电源噪声反馈数据校正

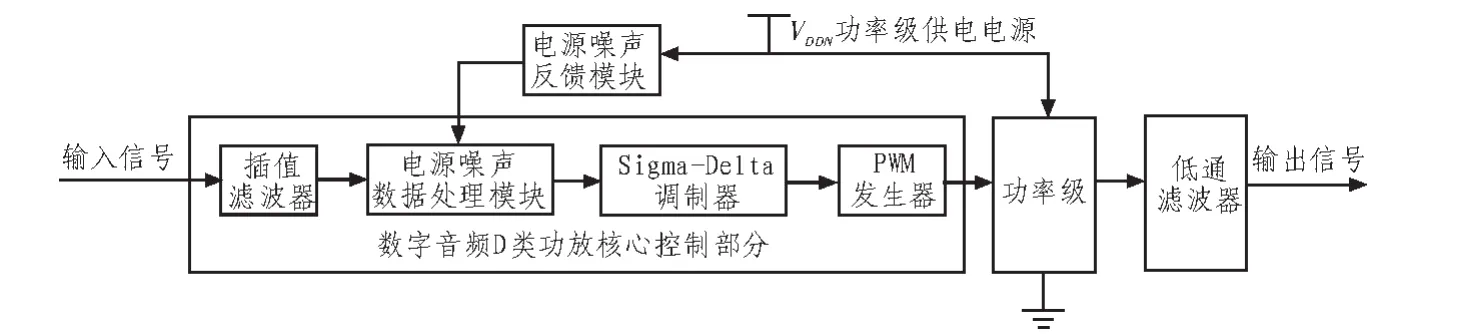

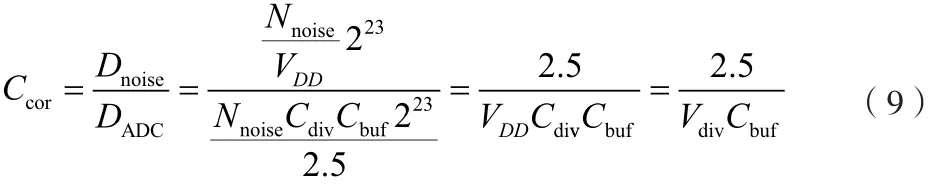

由于电源误差校正效果与电源噪声反馈数据的准确性密切相关。因此,需要将电源噪声反馈模块所反馈的数字量与实际电源噪声电压值准确对应。根据缓冲电路结构及ADC特性,电源噪声电压与ADC输出数据量(24 bits)的关系如下式:

其中Dnoise为电源噪声电压, cdiv为分压系数,cbuf为缓冲电路衰减系数,DADC为ADC输出数据量(24 bits),ADC模拟输入端的直流静态偏置电压为2.5 V。而送入FPGA内部误差校正模块的数据量与电源噪声电压的对应关系如下式:

其中Dnoise为送入FPGA内部电源误差校正模块的电源噪声反馈数据,Nnoise为电源噪声电压,VDD为功率级供电电压值。

联立式(7),(8)得到:

其中为 Ccor电源噪声反馈模块反馈数据校正系数,Vdiv为分压值,即1.75 V,cbuf为缓冲电路衰减系数。通过理论推导与实际测试,得到缓冲电路衰减系数 的值为0.8979,从而得到电源噪声反馈模块反馈数据校正系数 为1.59。在FPAG内部误差校正模块中添加校正乘法器(系数为1.59的常系数乘法器),校正电源噪声反馈模块的反馈数据,使得电源误差校正效果达到最佳。

2.3 电源噪声数据处理模块

电源噪声数据处理模块在FPGA平台上实现,与现有的基于FPGA的数字音频D类功放核心控制模块相配合,完成对电源误差的校正,提升系统性能。

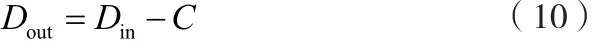

此模块采用verilog代码编写[8],状态机实现,当Sigma-Delta调制器尚未进入数据处理流程时,对其进行全桥的校正处理。电源噪声反馈模块返回的电源噪声数据Dnoise位宽为24 bits,其中低23 bits为小数位。为校正信号频率附近的互调失真,需要将电源噪声数据Dnoise乘以信号输入数据Din,得到校正数据,即 C=Dnoise*Din。由上面所得到的的两个校正数据,即可对Sigma-Delta输入数据进行预校正,其输入输出关系如下式;

其中Din电源噪声数据处理模块的信号输入值,Dout为电源噪声数据处理模块的输出值。

3 测试结果及分析

校正效果测试通过测量功放系统的电源抑制比(PSRR)来实现,采用如下方案[9]:功放系统左声道输入为0(静音),右声道输入幅度为0 dB的正弦信号,由于功放后端功率级和滤波电路直接与供电电源相连,右声道输出的信号会耦合到功率级供电电源中,使功放左声道输出含有右声道频率成分的信号,于是分别测量出左声道为半桥输出结构时其输出信号在输入信号频率成分的幅值Ripple_in'和左声道为全桥(电源误差校正使能)输出结构时其输出信号在输入信号频率成分的幅值Ripple_out ,即可得到功放系统在输入信号频率成功放开环半桥输出本身含有PSRR值[10])。

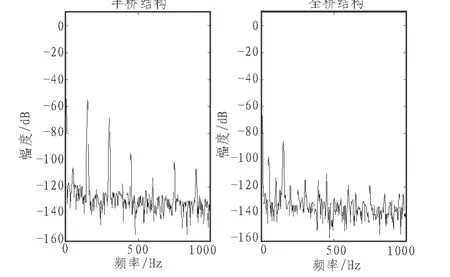

在实际中,电源噪声的主要成分为功率噪声50 Hz及其谐波成分,其中150 Hz为最具有代表性的电源噪声频率成分,因此在测试时选取150 Hz作为输入噪声信号频率,测试得到系统性能。当输入的电源噪声频率为150 Hz时,功放系统在半桥输出结构下和在全桥输出结构(电源误差校正功能使能)下的输出信号的频谱对比如图4所示。

图4 电源噪声为150 Hz时,半桥及全桥结构输出信号频谱对比图(0~1 000 Hz)Fig. 4 The comparison chart of half-bridge and full-bridge configuration output signal spectrum(0~1 000 Hz) when the frequence of power supply noise is 150 Hz

使用MATLAB对测试结果数据计算得到功放系统在电源噪声频率为150 Hz时的PSRR为36.78 dB,可以有效抑制电源噪声对系统性能的影响。

为了验证实际使用情况下,电源误差校正模块的性能,采用非稳压线性直流电源对功放功率级供电,输入为1 kHz、-5 dB的正弦波,分别测得在功放系统(全桥输出结构)的电源误差校正功能分别关闭和开启的情况下,其输出信号频谱对比如图5所示。

图5 功放系统的电源误差校正功能分别关闭和开启时,全桥输出信号频谱对比图Fig. 5 The comparison chart of full-bridge configuration output signal spectrum when the power supply correction is enable and unable

由上图可知,在采用非稳压线性直流电源的情况下,所使用电源误差校正方法可以有效抑制电源噪声与输入信号的互调失真,从而提高系统输出性能。

4 结 论

文中针对数字音频D类功放功率级供电电源引入电源噪声,降低系统性能的问题,分析了功率级电源噪声对输出信号造成的影响,提出了基于FPGA实现的功率级电源误差实时校正方法,经实际电路测试证明,电源抑制比达到36.78 dB,能够有效的抑制数字音频D类功放输出端电源噪声的影响,提高了数字音频D类功放的适应性。

[1] Huffenus A,Pillonnet G,Abouchi N.A High PSRR Class-D Audio Amplifier IC Based on A Self-Adjusting Voltage Reference[C]//ESSCIRC’2010 Proceedings,2010:118-121.

[2] Tol J,Rutten R,Reefman D,et al.A Digital Class-D Amplifier with Power Supply Correction[C]//121st AES Convention,San Francisco,2006:7-22.

[3] Rojas-Gonzalez MA,Sanchez-Sinencio E.Low-power high-efficiency class D audio power amplifiers[J]. IEEE Journal of Solid-State Circuits,2009,44(12):3272-284.

[4] Krein P T. All-Digital Audio Amplifier[D].Urbana-Champagne:University of Illinois at Urbana-Champaign,2001.

[5] Midya P, Roeckner B, Bergstedt S. Digital correction of PWM switching amplifiers[J].Power Electronics Letters,IEEE,2004,2(2):68-72.

[6] Black H S. Modulation theory[M].Van Nostrand, 1953.

[7] Shu W,Chang J S,Ge T,et al.Fourier series analysis for nonlinearities due to the power supply noise in open-loop class D amplifiers[C]//Circuits and Systems, 2006.APCCAS 2006. IEEE Asia Pacific Conference on. IEEE,2006:720-723.

[8] Samir Palnitker著,Verilog_HDL数字设计与综合[M].夏雨闻,译.北京:电子工业出版社,2004.

[9] Randy Boudreaux,Sean Davis.Measuring The Performance of Power Supply Rejection Feedback As Used in CS44800/CS44600 Digital Class-D PWM Amplifiers[EB/OL].(2005-02)http://www.cirrus.com/en/pubs/appNote/AN257REV1.pdf.

[10] Tong Ge,Joseph S Chang.Modeling and technique to improve PSRR and PS-IMD in analog PWM Class-D amplifiers[J].IEEE Transactions on Circuits and Systems II: Express Briefs,2008,55(6):512-516.