一种基于双口RAM的冗余系统通信方法

徐 军 张 磊 孙军峰

应用于轨道信号系统的车载信号设备,主要用于采集状态数据和输出控制指令,在运行过程中通信数据量大,而且通信过程必须具备极高的安全性和可靠性。

车载信号设备开发过程中,需要考虑多种提高可靠性的设计方案,目前比较通用的方法就是进行冗余容错设计。本文以某型车载信号系统预研为背景,利用双口RAM接口电路简单、数据交互量大、传输速度高等特点,设计了一种基于PowerPC和双口RAM的冗余系统,并采用新颖的角色轮换和自检技术,不仅保证了数据传输,而且也提高了系统的安全性。

1 系统总体交互方案

车载信号系统主要由主处理系统MPS、安全I/O设备GVIO(General Vital I/O)和外部设备组成。MPS主要通过GVIO进行数据收发,与外部设备进行通信,完成系统的状态采集和控制功能。

GVIO作为通信接口模块,支持多种接口与外部设备连接:通过RS-422与联锁设备连接;通过CAN接口与LKJ设备连接;通过RS-232与GPS信号连接;通过网口与无线传输模块连接,并与轨旁控制系统进行通信;通过安全IO接口进行布尔量采集和输出。

MPS和GVIO组成二取二的冗余系统架构,MPS由2个相同的处理模块MCU1(1#CPU)和 MCU2(2#CPU)组成。MCU1和MCU2具有相关硬件和软件,并且进行完全相同的逻辑运算处理,结构框图如图1。

GVIO主要从外部接收数据,并对2个MCU的数据进行一致性表决,表决通过后的数据,作为系统的最终输出结果。

在MPS中,MCU1和MCU2包含微处理器MPC8248、RAM、Nor Flash、PCI控制器、双口RAM;GVIO包含微处理器、RAM、PCI控制器和通信接口 (串口、CAN、以太网)。

MCU和GVIO分别与双口RAM的两端相连,GVIO系统通过PCI总线与双口RAM连接,MCU系统通过local bus总线与双口RAM连接,时钟模块分别与MCU系统、GVIO系统通过时钟信号线相连。

图1 系统模块框图

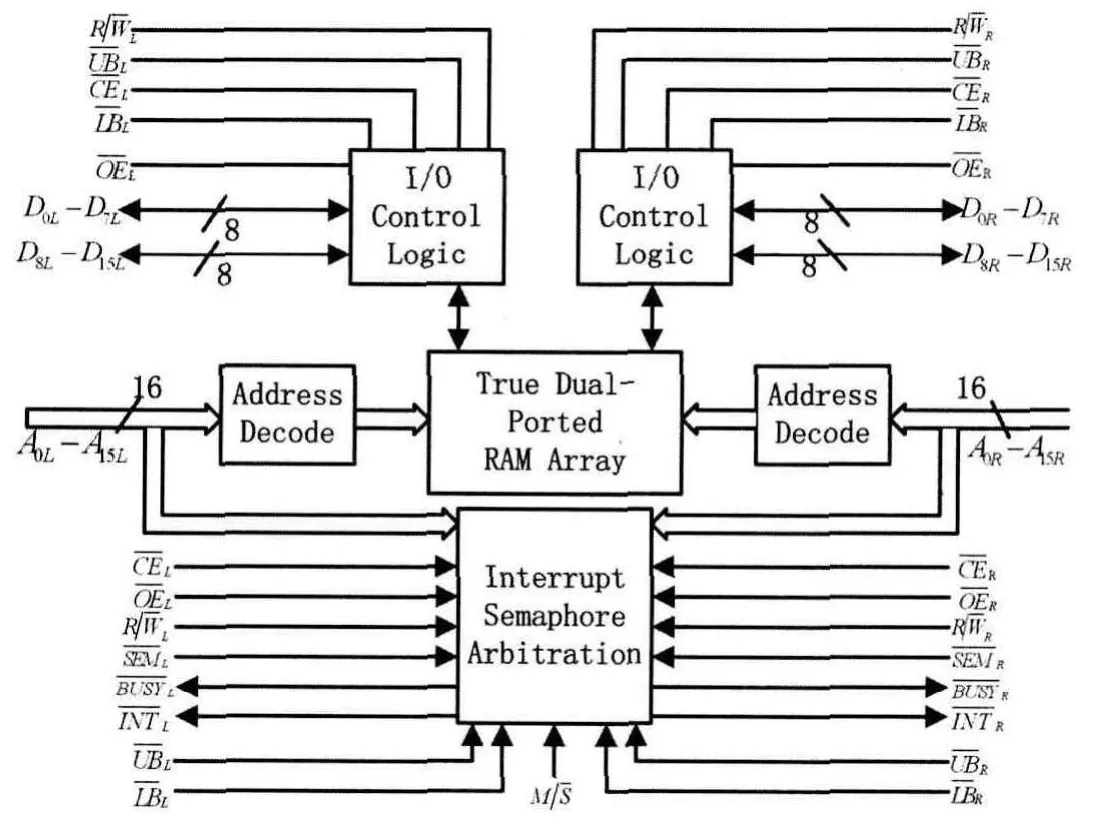

2 双口RAM硬件结构

双口RAM是双端口SRAM芯片,本设计采用CY7C028V-15AXI,最高15 ns读写速度,数据容量为64K x 16 bit,双口RAM具有2套完全独立的数据线 (D0~D15)、地址线 (A0~A15)和控制信号线 (片选、读、写、中断、忙等信号 )。CY7C028V-15AXI的逻辑模块如图2。

依据双口RAM的工作原理,其两端的CPU共享一个存储器空间,允许MCU(MCU1/MCU2)和GVIO同时访问双口RAM中相异的数据存储单元,可以快速交换数据,但是出现以下2种情况时,双端口存取可能会出现冲突问题:①MCU和GVIO同时向同一地址单元写入数据;②MCU和GVIO同时对同一个地址单元进行操作,MCU写入数据,GVIO读出数据,或者MCU读出数据,GVIO写入数据。

MPS和外部设备之间传递的通信数据,大部分都是安全相关数据,这些数据的可靠性极其重要,如果发生数据异常,可能引起难以预料的结果。

图2 双口RAM逻辑模块框图

3 数据通信方案

3.1 系统处理流程

MPS主要负责系统的逻辑处理与控制,GVIO主要负责数据的接收和发送,MPS和GVIO通过双口RAM进行数据交互,整个系统处理流程如下:

1.GVIO通过 RS-232、RS-422、CAN、以太网等接口,接收外部设备发送过来的数据,并通过I/O接口采集相应设备的布尔量数据。

2.GVIO将接收到的数据,各拷贝一份相同的数据,写入到双口RAM中,传递给MCU。

3.MCU1/MCU2从双口RAM读出数据,并进行逻辑运算处理。

4.MCU1/MCU2将处理后的输出数据放入双口RAM。

5.GVIO分别从双口RAM读出MCU1和MCU2写入的数据,通过 Safety-Coding-Arbitration进行数据一致性处理,将处理后的数据发送给对应的外部设备。

3.2 数据交换条件

MPS和GVIO进行数据交换的操作比较频繁,而且数据交互过程需要满足安全性、实时性和可靠性等要求。因此,MPS和GVIO双口RAM进行数据通信时,必须满足以下3个条件:①避免MCU和GVIO发生访问冲突;②提高MCU和GVIO数据交互速度,不影响设备的数据通信量;③保证交互数据的完整性、正确性、可靠性。

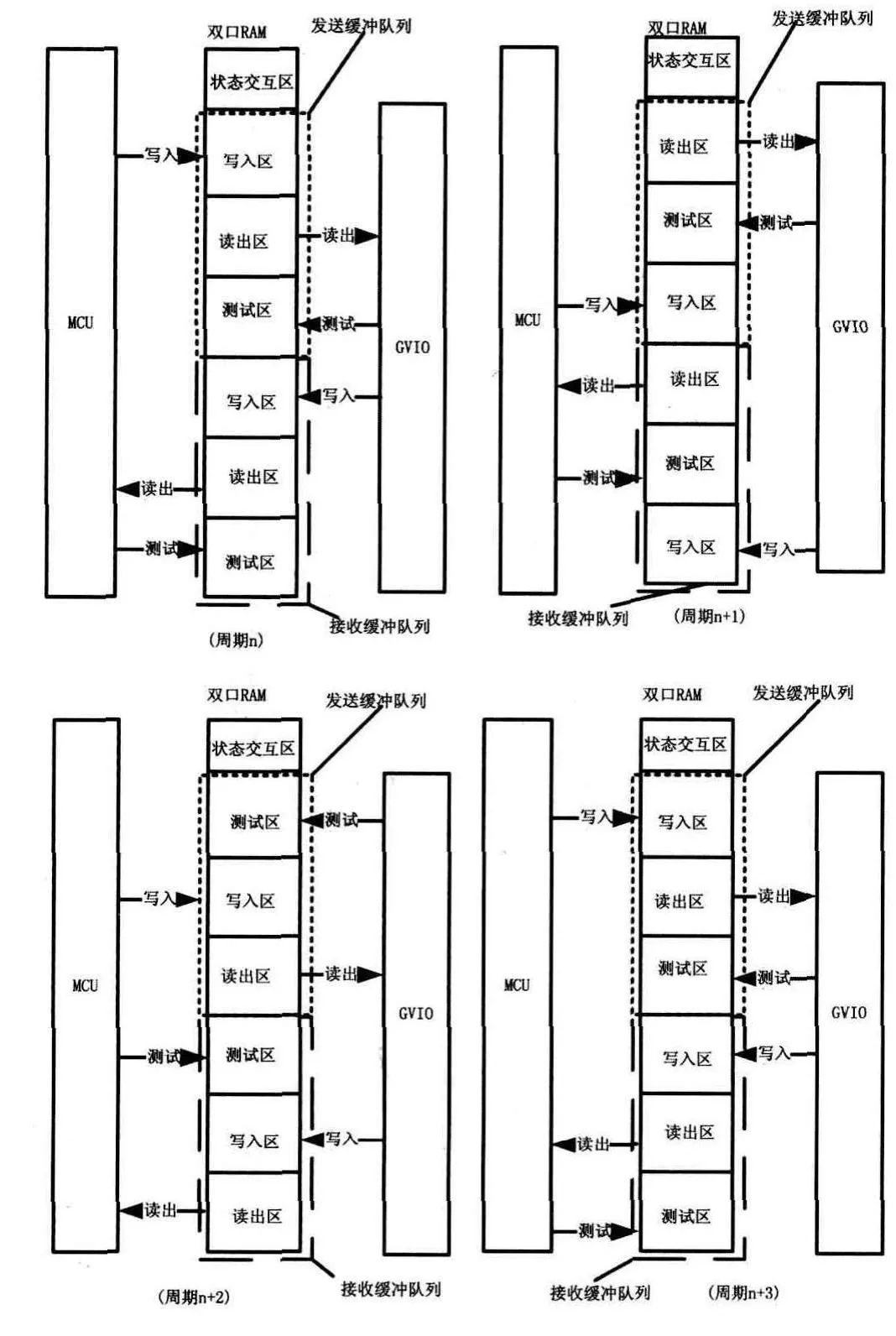

为了满足条件①,避免MCU和GVIO同时对双口RAM的同一个内存单元进行访问,本设计没有采用双口RAM的中断或者信号量等机制,而是采用了一种环形缓冲收发机制,将128KB的双口RAM划分为2个独立环形缓冲区:发送环形缓冲区 (63KB)和接收环形缓冲区 (63KB)。

发送环形缓冲区负责将MCU传递给GVIO,最终发送给外部设备;环形缓冲区从GVIO接收到数据,并传递给MCU。环形缓冲区如图3所示。

图3 环形缓冲区示意图

发送、接收环形缓冲区都再分为写入、读出和测试3个区块,每个区块的大小都为21KB。

MCU与GVIO通过相同的外部时钟中断来驱动数据处理软件模块的运行,MCU与GVIO在对双口RAM进行访问时可以做到同步、流水线作业。

在同一个处理周期内,发送或者接收环形缓冲区中任何一个区块,都有明确固定的角色,MPU板和HCU板不会同时访问操作相同区块,只有一个板卡对特定区块进行访问,避免了双口RAM的访问冲突问题。

MPS的运行周期为600 ms,MPS按照周期进行数据接收、处理和输出。其中,用于数据处理的时间为300 ms,MPS接收、发送数据超过300 ms,也会影响逻辑处理功能。在接收发送处理阶段,300 ms中的280 ms被分为20个发送接收子周期,每一个子周期的时间为14 ms。

读写双口RAM的数据速率为1 KB/ms,写入区块或者读出区块,有效交互时间280 ms内,可以交互高达280KB的数据,可以满足系统的数据通信量。因此,通过该设计可以满足条件②。

为了满足条件③,保证在双口RAM中传输数据的安全性和可靠性,采取2种安全数据处理措施:第一,通过Safety-Coding-Arbitration原理进行数据一致性处理;第二,对双口RAM进行自检,降低双口RAM的硬件失效和功能性故障的风险。

3.3 安全数据处理措施

3.3.1 数据一致性处理

Safety-Coding-Arbitration处理过程如下。

1.MCU1将要发送的数据Data1的CRCS进行掩码处理 (mData1),MCU2也对要发送的数据Data2的CRCS进行掩码处理 (mData2)。

2.GVIO从双口RAM读出经过掩码数据mData1和mData2,对mData1和mData2进行一致性比较和合并处理。

CRCd=mCRC1⊕mCRC2⊕MASK

3.如果CRCS等于CRCd,则表示从MCU1和MCU2传输过来的数据是一致的,可以进行合并后输出,否则丢弃。

3.3.2 对双口RAM自检

应用存储器检测算法对双口RAM存储功能性故障进行检测和诊断,能够及时发现和定位双口RAM的功能故障和硬件失效。检测步骤如下。

图4 数据交互流程图

其中,存储器模块M,有n个存储器阵列单元Ui;表示单元的状态处于状态值ν,其中ν∈{0,1},∈{0,1},i=1…n;表示单元的写入状态值ν;表示从单元的读出状态的状态值为ν;▽D表示单元地址按降序变化;i△Di表示单元地址按升序变化。

以上的多种措施,可以提高双口RAM数据交互的速度,也可以保证数据交互的安全性和可靠性。

3.4 软件设计

通过相应的软件设计及周期性步骤,可以实现冗余系统的安全通信方案,周期性步骤如下。

1.读出区块内容是否读完,如果读完,将该区块设置的标志变换为测试区块,下个周期对该区块进行测试。

2.写入区块内容是否写完,如果写完,将该区块设置的标志变换为读出区块,下个周期对该区块进行读出。

3.测试区块内容是否测试完,如果测试完,将该区块设置的标志变换为写入区块,下个周期可以对该区块进行写入。

4.对测试区块进行检测,是否发现硬件随机失效,若有,在状态交互区中进行记录状态和告警信息。

在同一个周期,MCU和GVIO操作不同的区块;通过周期轮转,各个区块进行角色轮换,如图4所示。

4 结束语

分析冗余系统应用双口RAM的性能和安全性要求,提出了多种措施来保证数据交互的实时性、安全性和可靠性,并在实际项目中应用,取得了良好的效果。

[1] 姜平,周荣根,肖红升,等.基于双口RAM的多机数据通信技术[J].仪表技术与传感器,2005,15:105-107.

[2] 张遵伟,曹宝香,聂胜伟.基于双口RAM的冗余架构同步技术研究[J].计算机工程,2012,38(18):221-224.

[3] 李震.一种基于双口RAM的环形数据缓存系统[J].计算机技术与发展,2010,20(1):201-204.