基于FPGA 的FBG 光纤光栅解调系统

何彦璋,隋广慧,常欢,申雅峰,张磊

(中航工业北京长城计量测试技术研究所,北京100095)

0 引言

光纤光栅的反射或透射谱的中心波长受应变、温度等因素的影响而发生变化,波长的变化量同应变和温度等因素具有确定的关系,因此波长解调是光纤光栅传感系统的核心技术之一。根据基本原理的差异,解调技术可以分为滤波器法、衍射光栅分光、干涉法及扫描光源法等,其中衍射光栅分光法利用光栅的分光特性,将不同波长的光束在空间展开后通过光电探测器进行检测,该方法可以达到1 pm 的波长分辨力,同时具有较高的环境适应性,在航空、航天、建筑等领域具有重要的应用前景[1-3]。

本文介绍了基于FPGA 的FBG 光纤光栅传感系统,运用FPGA 芯片控制InGaAs 探测器曝光、数据传输以及AD9826 模数转换芯片工作,通过网口将转换数据发送至上位机,最后依靠上位机软件实现高斯拟合算法,对采集数据进行处理获得解调结果。

1 FBG 传感解调系统工作原理

基于FPGA 的FBG 传感解调系统如图1 所示,宽带光源发出的光经过隔离器,进入环形器,环形器一端接光纤光栅,反射信号由环形器的另一端输出,经过准直透镜进入装置,由双光栅衍射分光,非球面反射镜成像在InGaAs 线阵探测器上。探测器将光信号转换为模拟电信号,模拟电信号通过AD9826 转换为便于FPGA 处理的数字信号,经过FPGA 处理后,信号通过以太网发送至上位机进行高斯拟合,最终得到解调结果。整个解调系统分为硬件系统和软件系统两大组成部分。

图1 基于FPGA 的FBG 传感解调系统原理

2 硬件系统设计

FBG 光纤光栅解调系统硬件部分:通过探测器将传感器发出的光信号转化为模拟电信号,然后通过AD9826 进行模数转换,最后FPGA 将数字信号通过以太网口进行发送至上位机。图2 为硬件系统构成示意图。FPGA 芯片为Stratix II 系列的EP2S60F1020C4。芯片为Stratix 系列的中档器件采用BGA 的封装形式,包含48352 个ALUTs、1024 个管脚、2.5 Mbit 的片上RAM 以及36 个DSP 模块。FPGA 控制整个系统工作,输出探测器控制信号CLK,RESET 信号,控制探测器按所需频率曝光;对AD9826 芯片进行初始化,然后输出AD9826 工作时钟信号,并接收转化后的数字信号并通过网口向上位机进行传输。图3 为FPGA 控制流程图。

图2 硬件系统构成

图3 FPGA 控制流程图

2.1 探测器驱动设计

根据系统设计要求,选用的探测器型号为滨松G11620 -512DA。其像元数为512,尺寸为32 mm ×15 mm×3 mm。探测器为单通道数据输出,工作最高时钟频率为1 MHz,输出模拟信号范围为1.2 ~2.4 V。CLK为时钟信号,频率为1 MHz,驱动探测器工作。

FPGA 根据探测器工作情况要求,输出相应的驱动信号,其中RESET 为探测器曝光使能信号,当在CLK下降沿时检测到RESET 为高电平时,探测器开始进行曝光积分;当在CLK 下降沿时检测到RESET 为低电平时,结束探测器曝光积分,在9 个时钟周期后将像元数据进行串行输出。FPGA 控制信号时序如图4 所示。

图4 FPGA 控制信号时序

2.2 AD9826 控制设计

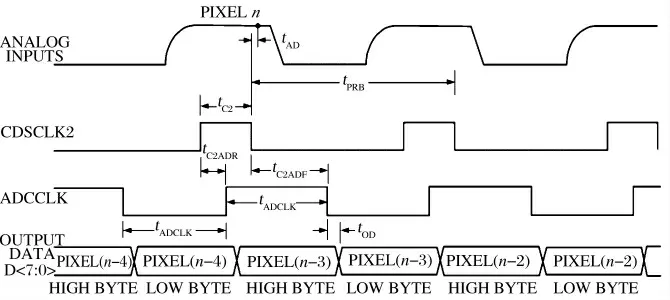

FBG 光纤光栅传感器所输出的光信号通过InGaAs探测器转换为模拟电信号,模拟信号需要通过模数转换芯片AD9826 进行模数转化,将转换后的数据通过FPGA 进行接收处理。选取的AD9826 模数转化芯片,是一款三通道、双工作方式的A/D 芯片,其转换速率达到15MSPS,采用分时输出高8 位和低8 位的方法来实现16 位数据的输出。根据InGaAs 探测器模拟信号的输出形式,选用一通道SHA 模式进行模数转换。图5 为AD9826 芯片一通道SHA 模式工作时序。

图5 AD9826 一通道SHA 模式工作时序图

运用FPGA 对AD9826 进行控制,在系统启动前对芯片SCLK,SLOAD,SDATA 寄存器进行初始化,选定芯片工作方式。然后输出CDSCLK2,ADCCLK 时钟信号,其频率均为1 MHz,相位相差90°。数字信号从AD9826 发出后,FPGA 采用串并转化将分时到达的高8 位和低8 位数据进行组合,当数据累积到512 个时,即一次测量数据接收完毕,FPGA 将数据打包准备通过网口进行发送。

2.3 以太网口控制设计

解调系统的解调频率可以达到1.9 kHz,每次测量的数据共计8192 bit,所以选择百兆网口即可。在FPGA 中运用软核NIOS,直接通过软件搭建网口控制平台。即运用NIOS 为FPGA 和网口协议芯片建立接口,数据从FPGA 进入网口协议芯片后,协议芯片根据TCP/IP 协议对数据进行打包后发送。

3 软件系统设计

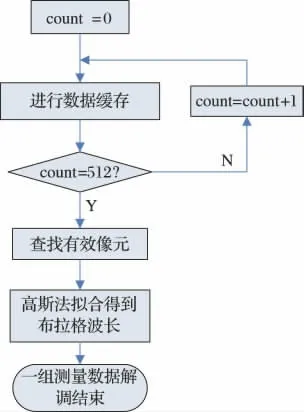

当FPGA 采集的数据通过网口发送至上位机后,软件系统对数据进行处理,图6 为上位机程序流程图,首先对数据进行缓存,当数据个数达到512 即一次测量的数据量时,开始查找有效像元数据,最后依据高斯拟合算法对有效数据进行处理,得到解调结果。

图6 上位机主程序流程图

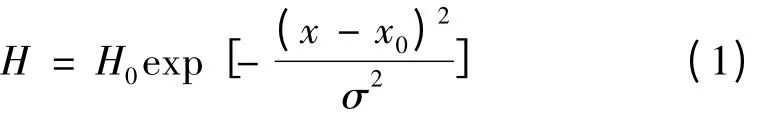

软件系统设计的核心是采取合适的波长拟合算法,计算出反射光的中心波长。寻峰算法基于高斯曲线拟合,对于光纤Bragg 光栅的反射功率谱密度曲线,理论上其强度最大值位于中心波长处,并以中心波长为轴左右对称,曲线可以用高斯函数近似表达为

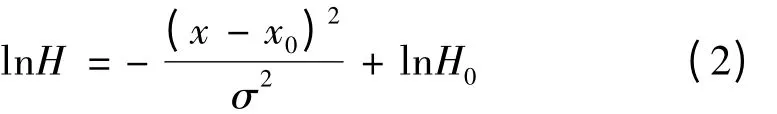

式中:H0,x0,σ2为实数常数,H0>0。对式(1)两边取对数得

式(2)可化为

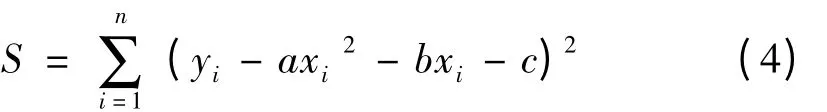

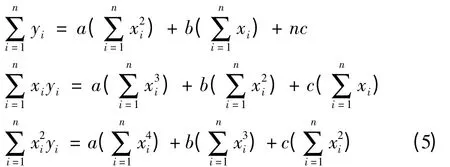

采用最小二乘法计算系数a,b,c。式(3)的离差平方和

为了使S 取得最小值,对式(4)中的系数a,b,c 求偏导,得方程组

式中:yi为探测器像元能量的对数值;xi为对应的像元坐标值。

解方程组(5)求得系数a,b,c。最后由a,b 可求得波长值x0为

采用回归分析获得的反射谱高斯拟合曲线,由于采用最小二乘法,保证了离差平方和取得最小,因此外界干扰对拟合高斯曲线的参数影响较小,各参数值主要取决于整体采样值[4]。所以运用曲线拟合求取FBG 反射谱的Bragg 波长值具有较高的准确性。

4 实验结果

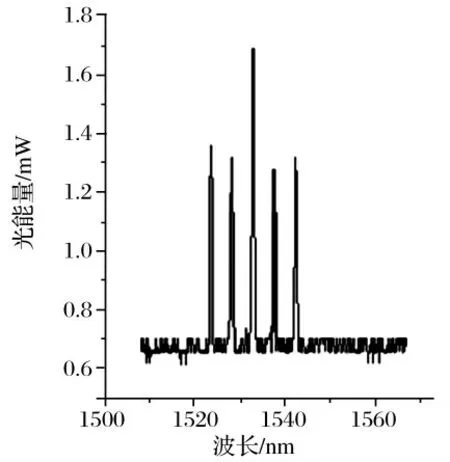

通过实验对该系统的可行性进行验证。试验装置如图1 所示,接入的FBG 光纤光栅的中心波长值分别为1523.238,1528.596,1532.697,1538.45,1543.886 nm。

最终解调结果如图7 所示,解调出波长值分别为1523.233,1528.592,1532.700,1538.455,1543.886 nm,满足设计要求。

整个解调系统解调频率达到1.9 kHz,输出光谱形状满足高斯分布特点,同时在满足耐奎斯特定理的前提下保证了波长解调的稳定性。通过实验结果发现,光谱随时间的波动较小,信噪比高,满足高速、高稳定性的解调要求。

图7 五个不同中心波长FBG 传感器的反射光谱数据曲线

5 结论

本系统运用FPGA 以及上位机软件完成了探测器驱动、探测器数据采集转化、高斯拟合处理、数据网口传输,实现了FBG 光纤光栅解调。通过实验验证了本解调系统能够实现1.9 kHz 高速解调,且解调精度能够达到±5 pm,具有较高的实用价值。

[1]冯忠伟,张力,何彦璋,等. 基于衍射光栅的光纤光栅传感器解调系统研究[J]. 计测技术,2011,31 (4):16-18.

[2]乔学光,丁锋,贾振安,等. 一种基于ASE 光源的边缘滤波解调技术的研究[J]. 光电子·激光,2009,20 (9):70 -73.

[3]Gao H,Yuan S,Bo L,et al. InGaAs Spectrometer and F -P Filter Combined FBG Sensing Multiplexing Technique [J]. J.Lightwave Technol ,2008,26 (14):82 -85.

[4]吴付岗,张庆山,姜德生,等. 光纤光栅Bragg 波长的高斯曲线拟合求法[J]. 武汉理工大学学报,2007,29 (12):116 -118.