一种实用的多通道SPI接口设计*

(中国船舶重工集团公司第七二二研究所 武汉 430079)

1 引言

在通信产品设计中,一般都会采用可拔插的多板卡设计,板卡分为两类:一类为主控板,主要实现数据交换、网管代理、配置保存和下载、状态查询和上报等功能,设计较为复杂;另一类为接口板,主要实现数据转换和接口适配功能,设计一般较为简单。设备中主控板一般只有一块(如果需要冗余设计则为两块),而接口板有多块,所有板卡均插在一块背板上。为了实现统一管理,主控板和接口板间需要增加管理通道。

对于管理通道,也有两种实现方式:一种是主控板和接口板均配置CPU 芯片,板卡间采用HDLC 接口或以太网接口实现管理通道,这样就需要每块板卡都编写软件代码,对于接口众多而接口板实现简单的设备而言,设计工作量大、成本高;另一种是仅在主控板上配置CPU 芯片,通过主控板提供并行数据/地址总线连接到各接口板上,接口板上的芯片可以直接由主控板通过总线进行控制,这样可以简化软件的代码编写,但由于并行数据/地址总线信号数量众多,设备背板设计将会很复杂,同时由于一组总线连接到多块接口板卡,其可靠性会降低。

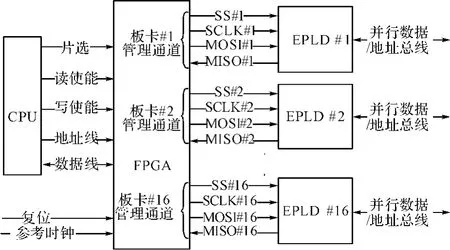

本文综合这两种实现方式的优点,在此基础上提出了一种新的实现方式,即主控板通过FPGA 芯片扩展出多个通道的SPI主模式接口,而接口板通过EPLD 芯片实现SPI从模式接口,再通过背板将主控板的SPI接口与接口板的SPI接口一一对应连接,主控板即可通过SPI接口对接口板进行管理操作。

2 SPI接口简介

SPI(Serial Peripheral Interface—串行外设接口)总线是一种同步串行外设接口,它可以使MCU 与各种外围设备以串行方式进行通信以交换信息。该接口一般使用四条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS。SPI接口传输的数据一般为八位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

3 FPGA 芯片介绍

本方案中采用的FPGA 芯片是Xilinx公司的Spartan-6系列[4]。该系列由13 个成员组成,可提供的密度从3,840 个逻辑单元到147,443 个逻辑单元不等。Spartan-6系列采用成熟的45nm 低功耗铜制程技术制造,与上一代Spartan 系列相比,该系列功耗仅为其50%,且速度更快、连接功能更丰富全面。Spartan-6FPGA 具备坚实的可编程芯片基础,且成本低,非常适用于可提供集成软硬件组件的目标设计平台。

4 多通道SPI接口方案设计

图1 方案设计框图

本方案中采用FPGA 芯片实现16路SPI主模式接口,同时采用EPLD 芯片实现单路SPI从模式接口,具体框图如图1所示。

由于需要扩展16路SPI主模式接口,所采用的逻辑资源较多,所以FPGA 芯片采用了Spartan-6 系列的XC6SLX9型号,该型号具备9152个逻辑单元和102 个可用IO 口管脚,且功耗很小,EPLD 芯片则采用了Altera公司的MAX II系列的EPM240芯片,也同样具备成本低和功耗小的特点。

4.1 SPI接口时序

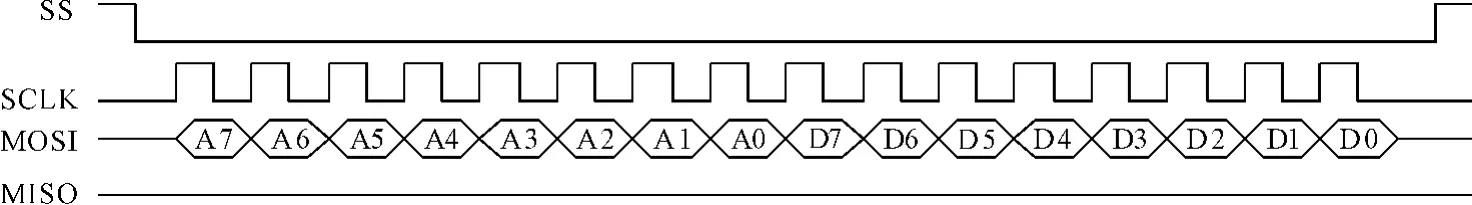

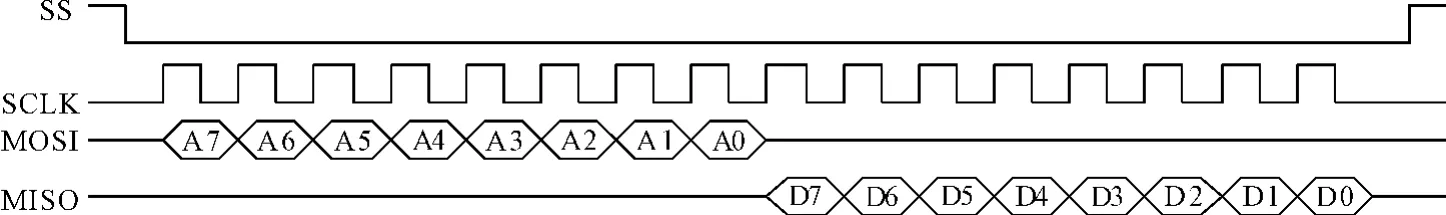

本方案由于SPI接口的主从模式均由逻辑实现,为统一设计,规范SPI接口的时序如下:

写操作时,SPI主模式接口在片选有效后,从时钟上升沿先输出地址,再输出数据,高位在前,低位在后;读操作时,SPI主模式接口同样先输出地址,然后由SPI从模式接口在时钟上升沿输出数据,也是高位在前,低位在后。地址的最高位bit作为读写指示信号,bit为0时表示本次操作是读操作,bit为1时表示是写操作。

图2 SPI接口的写时序

图3 SPI接口的读时序

4.2 SPI主模式接口设计

根据设计框图,为了实现多通道SPI接口,需要在FPGA 芯片内部扩展多组寄存器,CPU 通过并行数据/地址总线对寄存器进行访问,以控制每个通道SPI接口的读写操作。每组寄存器对应一个SPI接口,寄存器包括控制寄存器、地址寄存器,写数据寄存器和读数据寄存器。其中控制寄存器的bit0用于启动读写操作,置1表示启动读写操作,清0则表示停止操作;bit7为只读bit,读出为1表示本次操作尚未结束,为0则表示操作已完成。

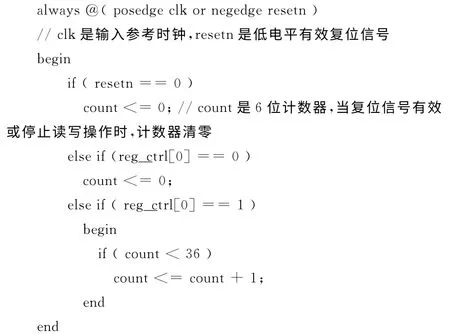

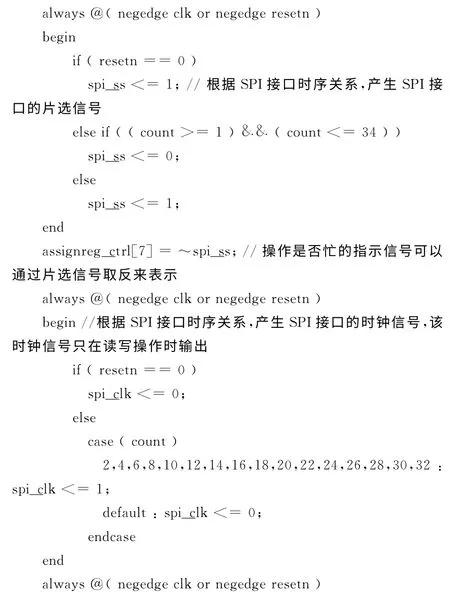

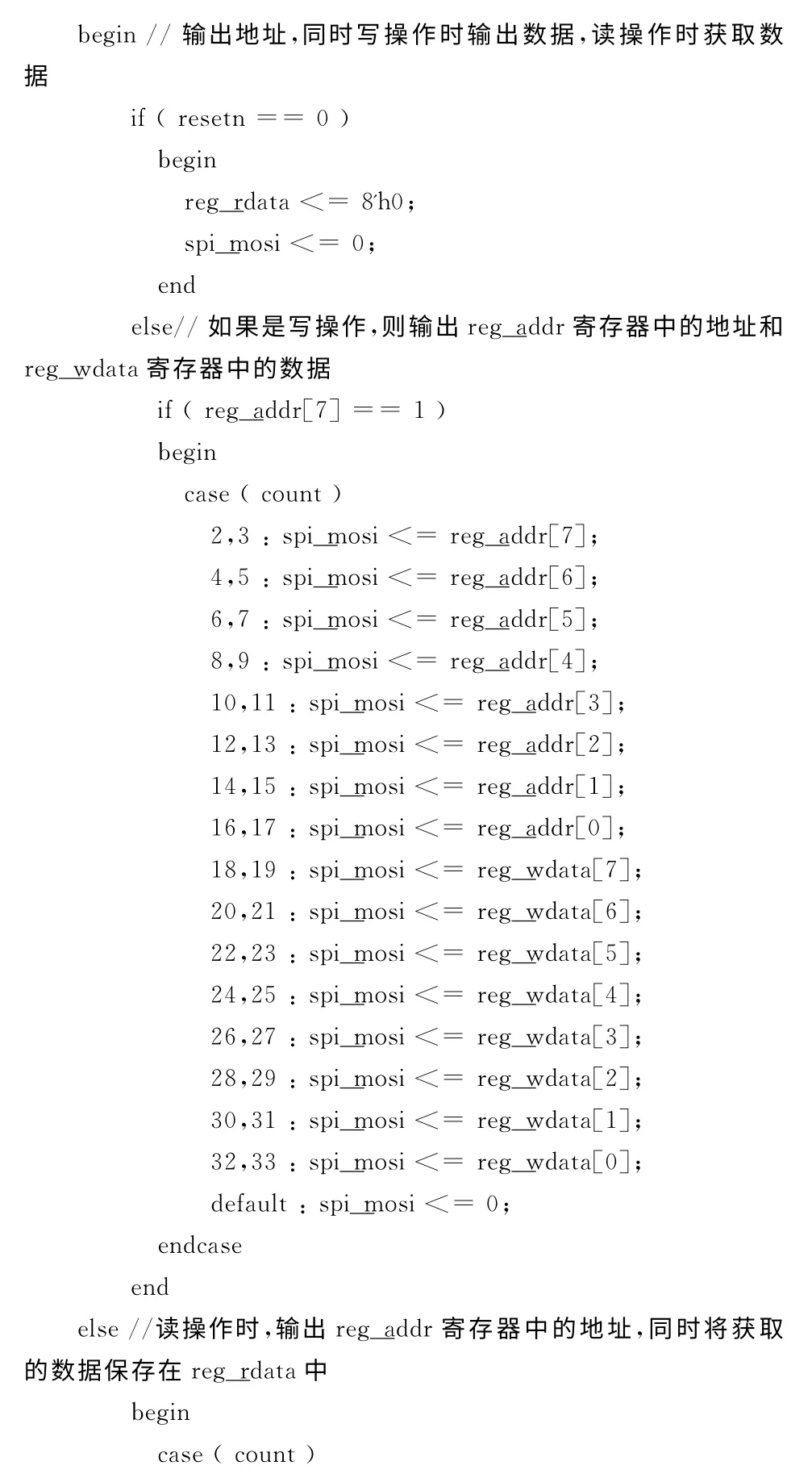

SPI主模式接口的主要逻辑实现代码如下:

4.3 SPI从模式接口设计

由于接口板的接口芯片存在不同类型,而不同类型的接口芯片其CPU 接口的时序要求也可能不同。为了灵活适配,在接口板的EPLD 中扩展了四个寄存器:并行接口控制寄存器、并行接口地址寄存器、并行接口写数据寄存器和并行接口读数据寄存器。主控板可以通过SPI接口对这些寄存器进行访问,以控制EPLD 的并行数据/地址总线的读写时序。其中并行接口控制寄存器的bit0表示是否使能操作,1表示使能读写操作,0表示禁止;bit1表示当前操作类型,0表示读操作,1表示写操作;bit7表示当前操作是否结束,1表示操作尚未结束,0表示操作已结束。

由于SPI从模式接口的逻辑代码较长,无法一一列举,这里将流程框图描述如图4:

图4 SPI从模式设计流程

5 结语

本文对不同设备内的板卡管理通道进行了分析,提出了采用SPI接口作为板卡间管理通道的设计方案。该方案采用FPGA+EPLD芯片实现SPI接口,可以根据项目需求灵活增加接口数量,同时也可以很方便地调整CPU 接口的访问时序。在实际的设备应用中,SPI接口作为管理通道运行稳定良好,有效地提高了设备的开发效率。

另外,本文中应用的SPI接口是8位数据和8位地址,如果实际使用有新的需求,完全可以将SPI接口的位宽扩展到16位或更多,而不会对整体设计架构有任何影响。

[1]田耘,徐文波.Xilinx FPGA 开发实用教程[M].北京:清华大学出版社,2008.

[2]EDA 先锋工作室.Altera FPGA/CPLD设计(基础篇)[M].第2版.北京:人民邮电出版社,2011.

[3]夏宇闻.Verilog数字系统设计教程[M].第2版.北京:北京航空航天大学出版社,2008.

[4]Xilinx,Inc.Spartan-6Family Overview,2011:1-2.http://www.xilinx.com.

[5]Xilinx,Inc.Spartan-6 FPGA Data Sheet,2011.http://www.xilinx.com.

[6]Xilinx,Inc.Spartan-6 FPGA Clocking Resources User Guide,2011.http://www.xilinx.com.

[7]Altera Corporation.MAX II Device Handbook,2009.http://www.altera.com.cn.

[8]麻志鹏,沈小林.PCI总线接口的FPGA 设计与实现[J].计算机与数字工程,2011(2).