STM32与FPGA的B码时统解码设计*

杨会玲,唐彬,王军

(1.苏州科技学院,苏州215011;2.安徽理工大学)

引 言

时间,作为一个基本的参考量,是人们在各个领域进行工作的标准。作为高精度时间传输系统的首选标准码,IRIG-B码因其众多优点得到广泛运用。本设计提出了一种新的B码解调方案,区别于传统的将单片机作为解调核心,而是从硬件处理效率等角度出发,利用微控制器STM32辅助Altera的可编程逻辑器件工作,从而解调出时间信息。

1 系统总体硬件设计

ST的STM32F103是一款增强型芯片,使用ARM公司的Cortex-M3内核技术。Cortex-M3内核功耗、能效比、处理速度、价格等方面的优势以及快速中断处理等技术,不仅满足了工控领域的高实时性要求,还为其在其他领域的运用奠定了一定基础,而且这些优点也完全符合B码时统解码要求。B码有直流码和交流码,交流码解码比直流码解码复杂。直流码可以通过FPGA直接解调出,而交流码则需要经过STM32处理后,将其变成伪DC码输入到FPGA进行解调出处理。

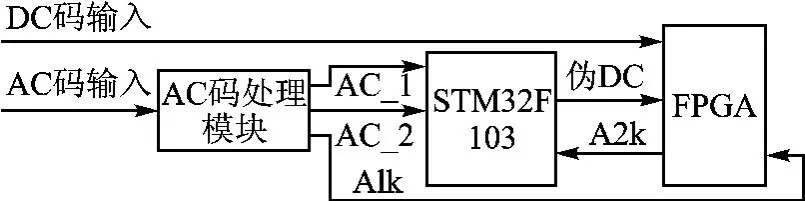

1.1 系统的设计简介

本设计主要功能是将输入B码的DC/AC码信号分别解调出来,DC码信号经电平转换后直接输入到FPGA进行解调,而AC码信号是交流信号,经通道传输后会发生衰减等现象,所以需要将AC码进行波形整形,预处理后再将传输的波形输入到STM32,最后将其产生的伪DC码和1kHz的脉冲进行处理,其总体设计如图1所示。

图1 总体设计框图

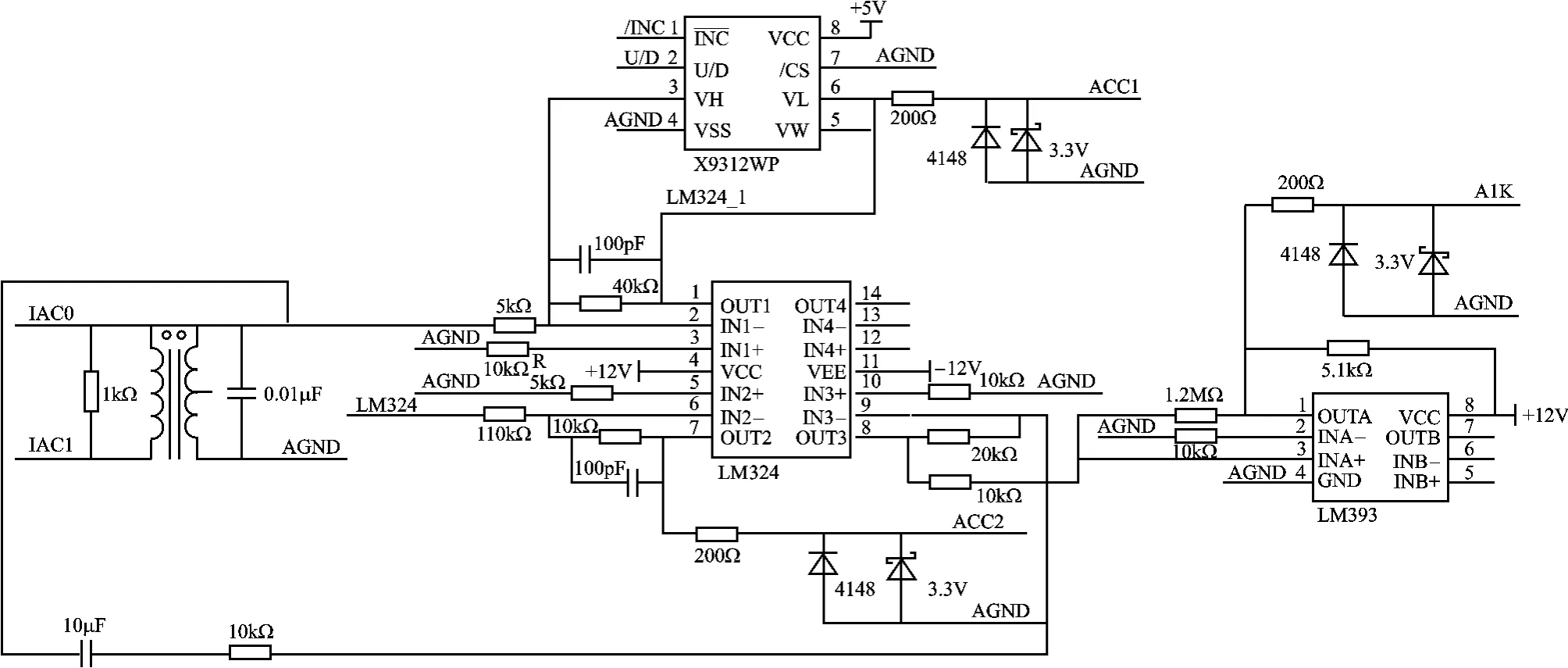

1.2 AC码处理模块

AC码处理模块[1-3]主要包括隔离变压模块、绝对值放大模块和过零比较模块。隔离变压器用来产生两路等幅反相的AC码,为方便硬件处理,需要将波形进行放大与过零比较处理,其硬件设计如图2所示,上半部分是绝对值放大部分,下半部分为过零比较部分。

图2 硬件设计电路

绝对值放大部分主要是由可编程电位器X9312WP和运算放大器LM324组成,作用是通过STM32的上升沿外部中断进行A/D采集,将波形的幅值调节到所需范围之内。X9312WP是Xicor公司生产的具有100个抽头的数字可编程电位器,驱动电压为3.3V,电阻范围为0~10kΩ,利用STM32控制端口INC和U/D来使阻值变化,其功能相当于一个10kΩ可变电阻和R并联成一个0~8kΩ范围的电阻,一路AC经过LM324反相后由这个并联电阻和X9312WP组成的自动增益电路来输出一个2~3V的反相正弦波(即AC_1),再将其经过LM324后输出一路与AC_1反相等幅的AC_2。

过零比较部分主要是由LM324、双电压比较器LM393和反相器组成,作用就是用来产生1kHz的脉冲。另一路AC码经过LM324等幅反相后经过LM393,用来产生标准的1kHz脉冲。为了增加信号翻转的可靠性,在LM393输出部分加了一个5.1kΩ的电阻作为上拉电阻。该部分因涉及模拟信号与数字信号共用,需要将模拟地和数字地进行信号隔离,使系统电路不受电源干扰。

1.3 AC码解码部分[4-5]

本设计使用了STM32的外部中断和A/D转换功能。在外部中断服务程序中启动A/D采集,得到当前输入AC码的幅值,并判断其幅值电压是否介于2~3V之间。如果不在幅值范围,则在中断程序中通过调节X9312WP的阻值控制自动增益放大器倍数,以使AC码幅值满足A/D采集要求,最后通过STM32的I/O口输出伪DC码。

STM32微控制器具有18路12位的ADC,可进行单次或者多次转换,输入时钟在14MHz之内,可将采集的结果放在16位的存储器中。输入2kHz脉冲情况下,利用其下降沿中断启动AC码的A/D采集功能,参考电压是由可调分流基准源TL431提供的3.3V电压,AC_1和AC_2分别连接着STM32的I/O口。若AC码输入是原相位方式而没有反相,则采用一路ADC即可,这样直接输入到STM32的I/O端口进行上升沿中断处理从而得出伪DC码。但是由于AC码的反相问题,所以需要AC_1、AC_2以及2kHz的脉冲。这里要注意的是,经测试STM32的外部中断延时是600ns,由FPGA产生2kHz脉冲信号的高电平脉宽需进行调整,以此来保证采集的幅值是最大的。

由系统的3.3V的参考电压和系统中ADC的12位分辨率得到信号采集灵敏度为0.806mV,AC码的幅值调节在2~3V且高低电平幅值比为1/2~1/6,故得出A/D采集的 VHmin=1240,VLmin=414,STM32系统AC码幅值采集流程图如图3所示。

图3 幅度采集流程图

1.4 DC码解码

在解码设计中,STM32产生的伪DC码和正常的DC码除了在秒头提取的方法上不一样外,时间信息的提取方法是一样的。DC解码分为两个部分:秒头的提取(1pps)和时间信息的提取。利用10kHz的频率进行码元识别时,因为偏差的缘故,所以在判断高电平个数时规定“0”的宽度为10~30,“1”的宽度为40~60,“P”的宽度为70~90,通过此法来提高准确性和精度性。

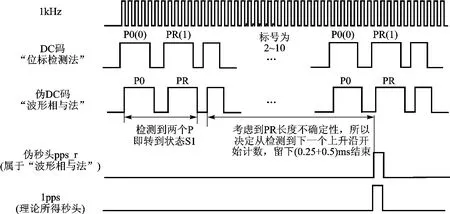

1.4.1 DC码的秒头的同步提取

B码的秒头和PR(一帧的起始位标识)的上升沿是一致的,这是对一个完整的数据进行读取和识别的前提。对于DC码的帧头的提取,提出了两种方法:精准计数法、位标检测法。秒头的同步提取如图4所示,这里使用位标检测法,给每个识别码一个标志,从P0的0标志到P9的10逐一递增,有三个状态S0、S1和S2。S0表示当检测到一个P(一帧所含的标志位)且此时标志位为11(立即赋值为0),即说明下一个状态为PR,此时开启启动开关。当检测到下一个上升沿的时产生秒头,否则返回继续监控并且检测到一个P标志位加1。S1为检测状态,当检测为P,说明此时为PR状态转到S2,如果检测到的不是P,则返回到S0继续检测。S2主要是赋予标志位值,此时为PR状态,所以给标志位为1,当检测到DC码上升沿的时候转换到S0继续监测。

由AC码得出的伪DC码只能用波形相“与”法[6]:为了产生pps_r,这里使用三个状态机:S0、S1、S2。S0用来监测8ms的高电平,当检测到后转向S1,否则不断检测;S1主要是判断连续的两个8ms高电平,检测到即转向S2,否则转回S0;考虑到PR的高电平数目不定,所以当检测到时间上升沿时在S2给予计数起始信号,延时特定时间后留下0.25ms+0.4ms的高电平作为pps_r信号。利用伪秒头pps_r和1kHz进行相“与”,从而得出AC码的秒头。

图4 秒头的同步提取

1.4.2 时间信息提取

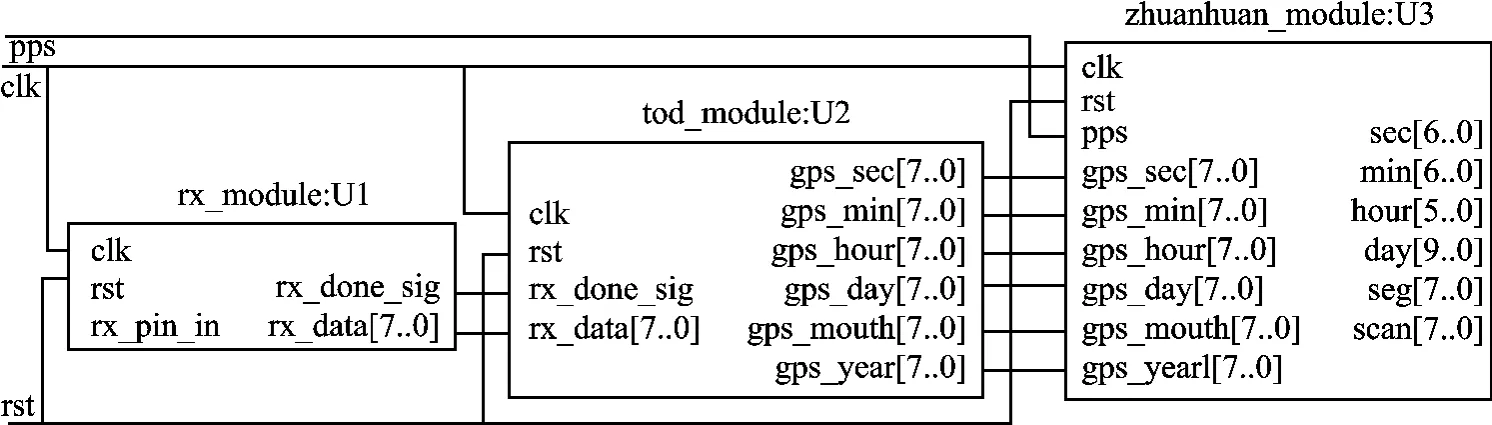

对于时间信息提取的方法,DC码和伪DC码是一样的。通过对DC码的解码,给每个码元一个编号,将其高电平脉冲个数取出,然后判断每个码元的电平状态,将结果存储在寄存器里,最后转换成易于使用的码值。截取时间信息时,在一个完整的时间传输完后,由下一个P状态标志结束后提取,这使得时间的准确性得到保障。设计模块的RTL视图如图5所示。

图5 总的RTL视图

模块U1的功能是保存每个码元的位数及相应的脉冲数;模块U2的主要功能是将每位的脉冲转换成相应的二进制码;模块U3的主要功能是将二进制代码转换成相应的BCD代码。

2 硬件电路实现与分析

2.1 DC码解码硬件实现

在硬件电路中使用两块实验板进行测试。一块实验板用来显示当前接收到的码流所含的时间信息,并通过DC码的形式输出,另一块实验板则用来将解调出的时间信息通过数码管显示。当解码正确时,两者时间显示一致,在示波器中显示授时秒头和解调秒头,如图6所示。

图6采用的是第二种方法,可见精度完全在ns级。DC码解码的两种方法经实验后对比分析如下:第一种因需计数990ms,50MHz晶振所用的计数器位数高达26位,虽然理论上可以得到准确的秒脉冲,但实际运行中考虑到价格问题,使用的是普通晶振,而非恒温晶振,所以产生结果与接收器所产生的秒头有1μs左右的延时,且无论如何补偿都有比较高的延时;第二种虽理论上有一个时钟的延时,但由于没使用计数器,所以对于时钟频率比较高的电路是有效的,这里使用了50MHz的晶振,所以在示波器上显示的延时是30~40ns。

图6 DC码解码秒头

2.2 AC码解码硬件实现

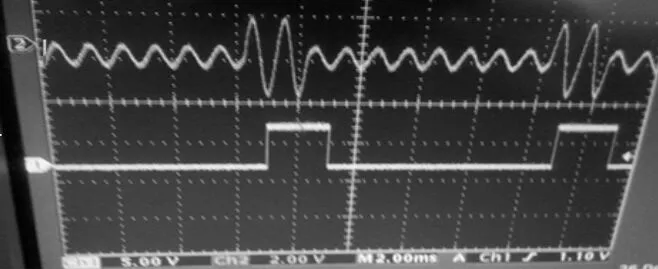

如图7所示,上面是经过模拟电路处理后的AC码,下面是将几个模块整合后由STM32的I/O口输出伪DC码,可以看出它比AC码延时了250μs,符合设计要求。

图7 伪DC码与解码时间

在硬件实验板上将伪DC码输入到FPGA后进行解调处理,硬件电路显示出的时间信息也完全一致。

结 语

本文针对普通单片机执行速度慢及精度低等问题,提出了一种新的B码时统解码方案。在AC码的解码方案中,一方面采用微控制器STM32的高速信号采集功能,另一方面通过STM32系统实现实时自动增益调节功能,辅助FPGA进行解码;在DC码的解码部分采用“位标检测法”使解调精度控制在ns级。通过实验结果分析,该B码解码设计方案具有实时性高、占用资源少和抗干扰性能好等优点,同时提高了B码解码精度,增强了系统可靠性,故本文的设计方案对B码技术在工程中的应用具有积极的借鉴价值。

[1]佟刚,崔明.MSP430F149在IRIG-B码解码中的应用[J].计算机测量与控制,2007,15(11):1597-1599.

[2]黄春林,赵云峰.基于 MSP430与FPGA的高授时精度时码终端系统设计[J].战略导弹技术,2011,1(1):115-122.

[3]李咏豪.时间统一系统终端设备的研究[D].长春:长春理工大学,2008.

[4]任志国.时统信号(B码)在数字信道上畸变问题研究与解决[D].长沙:国防科技大学,2003.

[5]刘懿.基于FPGA的分布式采集系统时钟同步控制技术研究与实现[D].成都:成都理工大学,2009.

[6]赵云峰,崔明,吴志勇.新型高授时精度时码终端系统设计[J].电光与控制,2009,16(3):86-90.