基于边界扫描技术的通用测试系统设计

尤 路, 谭剑波, 夏 勇

(中国电子科技集团 第三十八研究所,安徽 合肥 230088)

随着电子设备的大量应用,其测试维修设备的需求越来越多。数字电路板在电子设备中占有的比例较大,设计一款针对数字电路板的通用测试系统,对于解决电子设备的测试维修具有极大的意义。常规的测试设备多为功能性测试[1],该测试通过对各待测件加入测试激励,在输出端检测输出响应。这种测试设备的设计较为复杂,成本较高,不具备通用性,且很难精确定位故障。运用边界扫描测试技术设计一款既通用又快速的自动测试设备(Auto Testing Equipment,简称ATE),对电子设备的测试维修具有一定的实用价值。

1 通用测试系统的组成

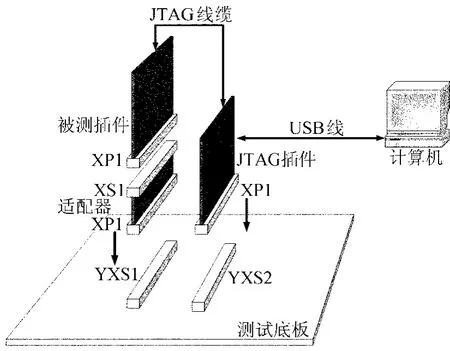

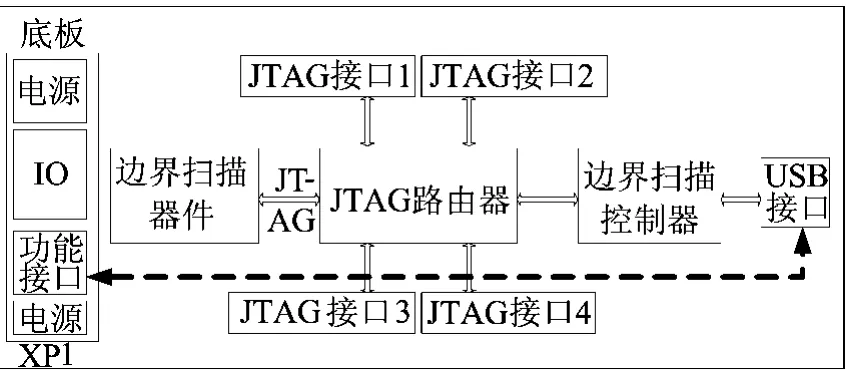

通用测试系统由装有边界扫描测试软件的上位机、测试底板与适配器、JTAG测试插件及被测试插件组成,如图1所示。

图1 通用测试系统的组成

JTAG插件主要由边界扫描器件、边界扫描控制器及边界扫描路由器组成,被测件通过适配器与测试底板相连,JTAG插件在测试时插入底板,底板上连接JTAG插件的插座与连接适配器的插座通过印制板线直连。测试时,需将被测件上的JTAG口连接至JTAG插件上的路由端口,以保证所有的JTAG链路都可被JTAG插件上的控制器控制。

适配器的主要功能是将被测插件的IO转接至JTAG插件上的边界扫描器件的边扫单元,通过给不同的被测件配备不同的适配器来实现测试系统的通用互换功能。

2 系统工作原理

边界扫描测试技术是国际联合测试工作组于1987年提出的一种新的电路板测试方法[2-3],边界扫描测试技术目前已广泛应用于数字集成电路器件的设计及军用民用的电子设备中,“边界”指测试电路被设置在集成电路器件功能逻辑电路的四周,位于靠近器件输入、输出引脚的边界处。“扫描”指连接器件各输入、输出引脚的测试电路,实际上是一个串行移位寄存器,该寄存器被叫做“扫描路径”,沿着这条路径可输入由“1”和“0”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。IEEE1149.1规定的边界扫描测试总线由测试总线输入(TDI)、测试数据输出(TDO)、测试模式选择(TMS)、测试时钟(TCK)、测试复位(TRST)(可选)组成[4],如图2所示。

图2 边界扫描测试系统原理图

边界扫描技术的使用,不仅能测试集成电路芯片的输入/输出管脚的状态,还能测试芯片内部的工作情况以及印制板走线的开路和短路故障。对电路板中边界扫描器件管脚的测试可完全覆盖,且能实现高精度的故障定位,对数字电路测试具有重要意义。

以某被测件为例,被测件中包含一颗边界扫描器件,与此同时外围还包含4组总线缓冲器IC1~IC4及1组SRAM,如图2所示。运用边界扫描技术,通过测试底板及适配器,可实现对其所有器件的测试覆盖。

3 测试系统的硬件设计

3.1 测试底板及适配器的设计

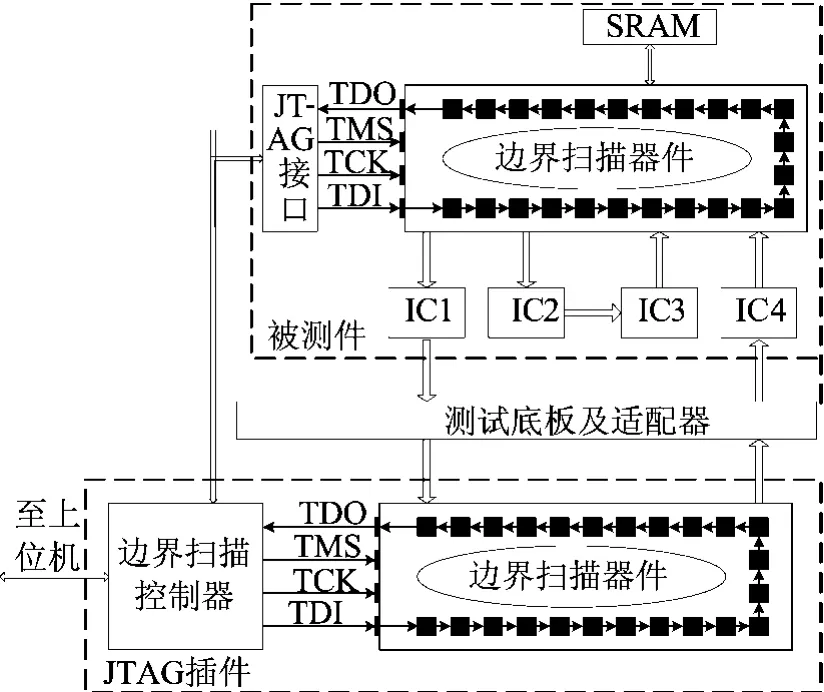

测试底板及适配器的主要功能是给被测件及JTAG插件供电,并完成被测件与JTAG插件之间的信号匹配,所以在设计测试底板时需要将被测插件所需的主要电源类型引入插槽(如5.0、3.3V等),特殊电源类型的插件可在适配器上进行电压转换。测试底板的设计示例如图3所示。

图3 测试底板的设计

图3中,YXS1和YXS2分别为被测件适配器插槽和JTAG插件插槽,其连接器型号与适配器及JTAG插件的接口连接器型号相对应。本文将常用的5.0V和3.3V电源接入以上2个连接器中,其电压管脚完全相同,保证在插件错插时不会损坏器件;2个连接器上的IO管脚尽量保证一致;功能接口可作为备份,也可与外部接口相连,或由设计师根据具体需求自行选择;适配器主要完成测试底板与被测件的信号及电压匹配。

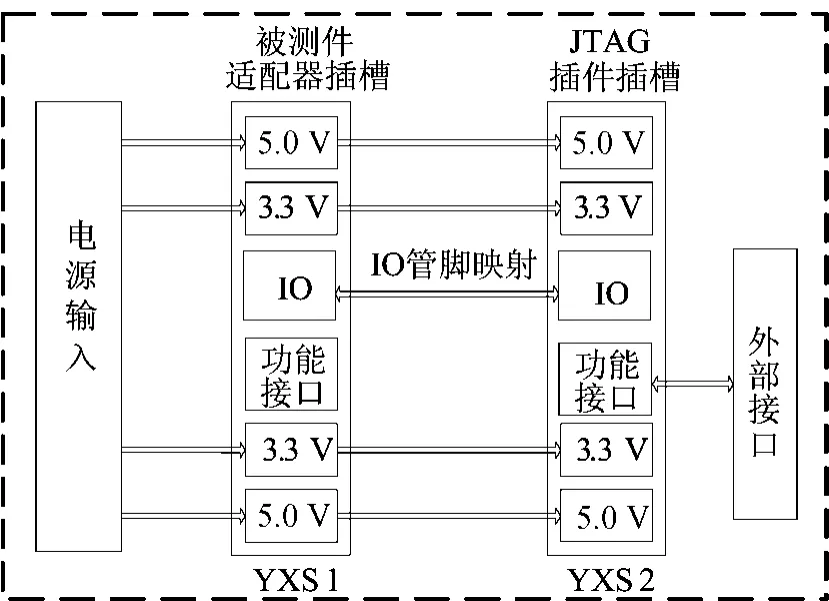

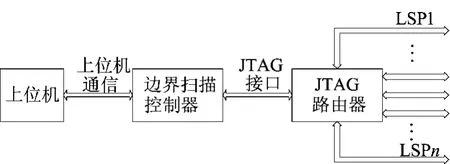

3.2 JTAG插件的设计

JTAG插件包括1颗包含大量可用IO端口的边界扫描器件、1个JTAG路由器(端口数由被测件上JTAG链路的数量决定,一般预留4个JTAG接口)、1个USB接口的边界扫描控制器[5],边界扫描控制器负责与上位机的通信,生成测试向量,并接收测试结果[6]。JTAG插件组成如图4所示,XP1为与测试底板相连的连接器,JTAG接口1~4可根据被测件上JTAG链路的数量选接,USB接口为与上位机的通信接口。

图4 JTAG插件结构图

3.2.1 JTAG路由器的设计

JTAG路由器采用专业的JTAG系统级接口芯片所提供的单点接入到多扫描链结构,具有支持隔离的诊断能力,因此可以选择不同的分支链路进行测试,从而增加了测试的灵活性,使得控制器可以同时控制多条JTAG链,扩大了测试覆盖范围,实现系统级的边界扫描测试,其工作示意图如图5所示。目前,市场上主流的JTAG路由器芯片主要为德州仪器的8997Scan Path Linker,Firecron公司的JTS系列。

图5 JTAG路由器工作示意图

3.2.2 IO接口设计

JTAG插件上的接口部分相对简单,其中电源部分是根据JTAG插件上所需的电源类型所决定的,如有特殊的电压需求,可通过板上的电压转换芯片进行转换。因在适配器中已对被测件的输入输出电平进行了转换,所以在JTAG插件中的IO接口不做方向限制,仅在接口处做限流保护后直接接入边界扫描器件,连接器XP1要与底板上的连接器YXS2相对应。

边界扫描器件的扫描链需接入板上路由器的JTAG接口,保证该链路可被控制器单独控制;路由器的主JTAG接口与控制器的JTAG接口相连,由板上直接供电,USB接口除了预留在插件面板上外,还可引入底板的功能接口,通过底板接入上位机避免外部走线,如图4虚线所示。

4 测试系统的软件设计

4.1 软件的系统构架

测试系统软件由界面程序、后台处理程序[7-8]、数据库管理程序和报表生成程序等组成,如图6所示。其中后台处理程序负责边界扫描控制器的协议控制及测试向量的产生,与其配套的控制器一起使用。该系统中对每个被测件按不同测试类型建立好测试向量,并解析其测试结果。数据库中存放着每块被测件的图片信息及被测件上每个器件的信息,这些信息在设计时通过界面录入,测试结束后将故障信息显示在界面上。最后,所有的测试结果及维修记录均通过报表的形式保存,并打印出来。

图6 测试系统软件组成

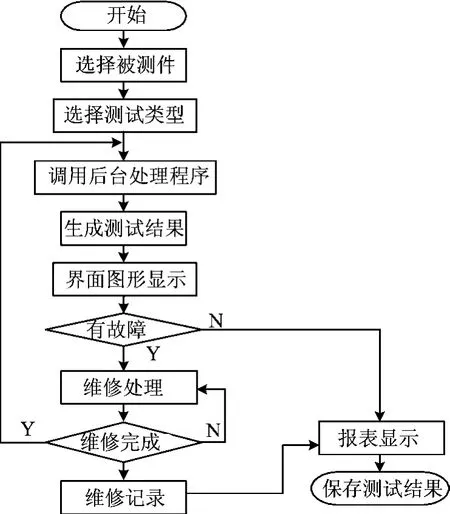

4.2 软件的设计流程

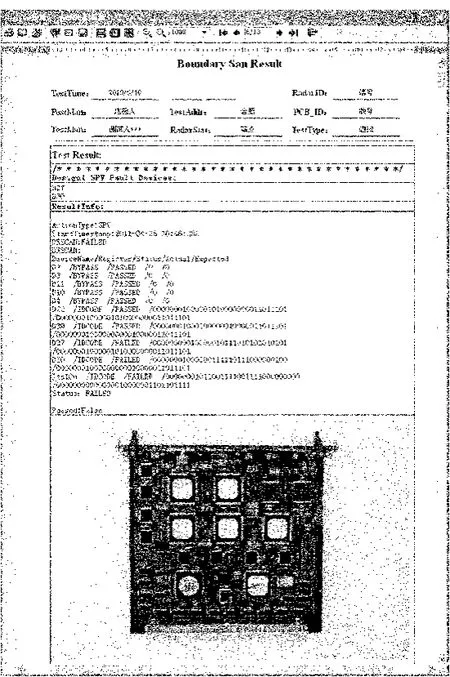

软件在运行时的工作流程如图7所示。选择被测件时,不同的被测件在后台已建立好不同的测试工程,测试结果报表如图8所示。

图7 软件工作流程

图8 扫描链完备性测试结果报表

5 结束语

为了满足电子设备的测试需求,本文运用了边界扫描测试技术设计的测试系统,具有较好的通用性和易操作性,很好地解决了电子设备测试维修的难题,大大提升了测试效率,为各个领域中的数字电路测试维修设备的设计提供了指导方案,具有极大的市场前景和推广价值。

[1]李 宏.雷达数字电路板测试台的开发与应用[J].雷达与对抗,2006(4):28-29.

[2]1149.1-1990,IEEE Standard Test Access Port and Boundary-Scan Architecture[S].

[3]1149.1-2001,IEEE Standard Test Access Port and Boundary-Scan Architecture[S].

[4]Parker K P.The boundary-scan handbook[M].2nd ed.Boston:Kluwer Academic Publishers,2003:1-200.

[5]俞 洋,高 巍,彭喜元.基于USB接口的边界扫描测试控制器设计[J].计算机测量与控制,2007,15(1):31-33.

[6]刘 军.JTAG技术在PCB测试中的应用[J].科技信息,2010(21):7-9.

[7]张建生,李 洋,宋何娟,等.JTAG标准及其与16位微处理器IP软核的集成[J].合肥工业大学学报:自然科学版,2008,31(9):1365-1368,1407.

[8]黄 新,雷 加,颜学龙.基于网络的边界扫描测试技术的研究与实现[J].计算机测量与控制,2010,18(7):1476-1478.

- 合肥工业大学学报(自然科学版)的其它文章

- 基于拓扑优化与灵敏度分析的客车车身轻量化研究

- 基于面部特征的疲劳驾驶检测