综合核心处理机的设计与实现*

段求辉

(中国西南电子技术研究所,成都610036)

随着航空电子技术的不断发展,航空电子系统的结构从最初的分布式模拟结构一直演变到目前的综合式积木结构[1]。在综合式积木结构中,航电系统的数字计算被集中在一起,利用现有的成熟技术或货架产品,设计成高度综合化的通用处理平台-综合核心处理机,以降低系统费用。

机载传感器作为航电系统的重要组成部分,其信号处理和数据处理在航电系统的数字计算中占有举足轻重的地位。本文针对机载射频传感器系统数字计算的特点,对综合化核心处理机(ICP)架构设计的考量因素进行了分析,并给出了一个具体核心处理机的设计和实现结果。

1 ICP架构特征

1.1 架构的基本特征

从计算用途来看,ICP需要完成传感器系统(包括雷达、通信、导航、识别、电子战和光电传感器等)[2]的信号处理、数据处理运算,以及多传感器数据融合、导航计算、火控计算、干扰控制、显示控制等任务处理功能,并且这些计算和处理的数据是突发的或受外部激励导致的,而且往往多种计算是同时存在的,因此ICP应该具备并行计算机的体系结构特征,类似于商业计算中定义的支持多道程序运行或多用户应用的多处理器计算机。此外,作为多个?传感器共用的处理核心,ICP必须有多个I/O和各种传感器或者其他航电设备连接,因此其必须是一个多入多出的计算机系统。

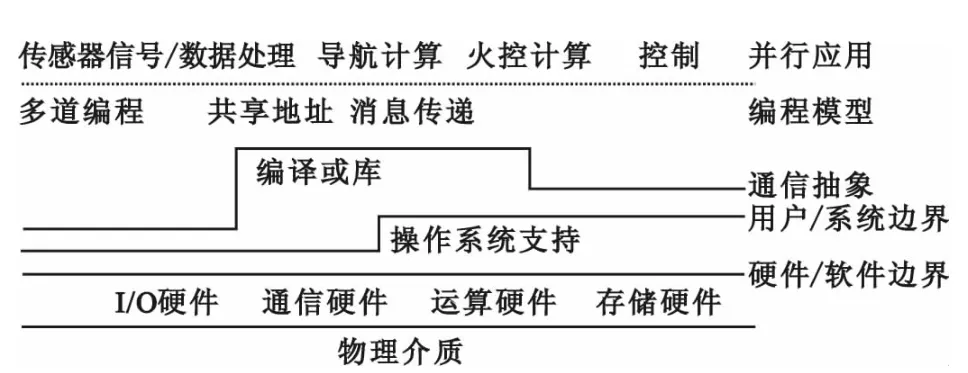

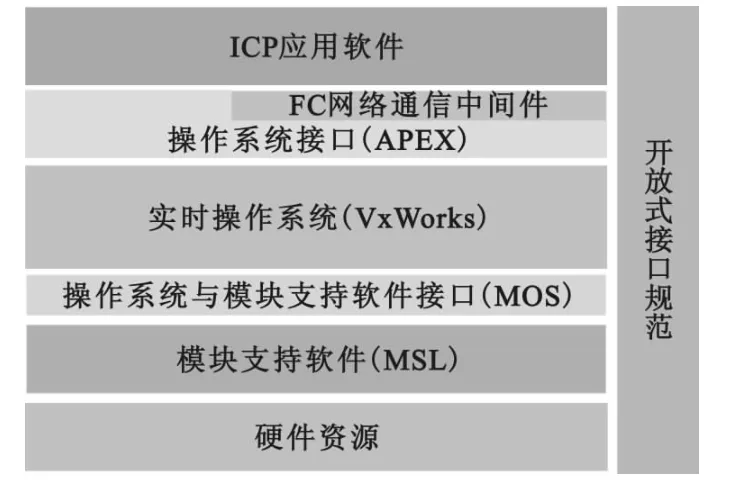

从软件实现的角度来看,完整的ICP体系结构应该同时包括硬件特征以及为了支撑用户编程的软件特征,即ICP的体系结构特征还应包括编程模型以及通信抽象,其中编程模型是程序员在编程时所看到的ICP特征,通信抽象则表现为ICP的通信原语,为应用程序和系统实现之间的一个边界。图1是参照David E.Culler等人提出的并行计算机体系结构抽象层次[3]所定义的ICP体系结构抽象层次。

图1 ICP体系结构抽象层次Fig.1 Abstract level of the ICP

在ICP体系结构抽象层次中,编程模型定义了应用程序的各部分之间是如何协调一致和实现信息交互的,主要包括3种:多道程序、共享地址、消息传递[3]。

编程模型通过下面的通信抽象映射成ICP中的具体实现,通信抽象在ICP中的实现可以是由操作系统提供的通信支持或者是专门为ICP编写的通信支持库。整个抽象层次的最底层是支持ICP实现的各种硬件资源,其设计既要满足ICP的应用需求和体系结构的要求,同时还需要考虑工程约束,如成本、可扩展性等。

1.2 ICP体系结构设计的考量因素

从使用的角度来看,ICP的架构设计必须同时满足两个方面的需求,一是满足数字计算所需的运算性能需求,二是满足最终购买用户关心的成本、体积、重量和可扩展性等需求。

通俗来讲,运算性能可以用程序执行时间来衡量,它可大致分解成两部分,一是处理器执行程序所花费的时间,还有就是程序执行通信所花费的时间。其中处理器执行程序的时间花费和处理器自身的硬件性能以及程序或具体算法的特性有关,一般只能通过选取性能更优良的处理器芯片或改进具体算法来优化,本文对此不作讨论。而程序执行通信的时间花费与编程因素和硬件因素都有关,是ICP架构设计所关心的,一般可采用以下的通信代价模型来描述:

其中,CT(n)为传输n字节数据的代价;FT为程序中通信操作的次数;T(n)为通信时间开销;TOL指可以和其他有用工作同时进行的通信操作部分,例如计算以及其他通信等,这意味着部分通信代价被程序的并行性所抵消。

对于ICP这种需要支持高频度通信的设备来说,通信代价模型中通信时间部分所占比重必须比较小,这意味着ICP必须是低负载、低网络延时以及很小的占用度。对通信代价的关注决定了ICP在通信频率或通信量增加时,其内部通信体系结构应该能很好的适应,从而不会造成计算性能的大幅度下降。

传统上通信时间开销T(n)采用与传输带宽采用线形模型来描述:

其中,n为需要传输的数据量;B是传输通路的带宽;T0为常量,即启动传输所花费的时间。

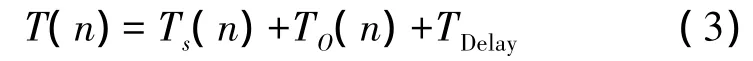

在实际使用中,情况较为复杂,例如传输方式可能是流水线方式,传输通路上可能有多个地方需要缓存数据,多个并发传输之间往往要竞争传输资源,等等,因此一般采用以下改进模型来描述:

其中,Ts(n)指处理器用来启动传输所花费的时间。这可以是一个固定的开销,也可能是n的线性函数,取决于具体的传输机制;TO(n)被定义为占用度,它表示数据通过通信路径上最慢的部件时所用的时间,部件包括缓冲区、交换机和通信辅助部件等,在只考虑通路带宽限制因素时占用度可以表示为n/B;TDelay(n)表征的是一个最小的数据单位经过数据通路所花费的时间,也即所谓的传输路径延时。

ICP的成本、体积、重量和可扩展性等需求一般通过架构中的资源模块化、通用化、资源的可共享、可重构以及架构的开放性等综合化因素来解决。

资源的模块化、通用化意味着在硬件设计时将硬件按功能分类,同类的硬件模块对外提供相同的接口定义以及功能服务。在软件设计方面则需要设计软件中间件,该软件对下屏蔽硬件资源的具体差异,包括处理器的差异、通信电路差异以及模块内部支持资源如定时、BIT等的差异;对上提供应用软件所需的统一接口抽象,实现系统服务调用、数据通信等功能。

资源的可共享和可重构除了资源必须通用外,还必须保证资源之间是可任意连接或者连接是可灵活配置的。一般来说,采用集中式总线或者交换网络都能实现这种灵活互连的需求,但是如果考虑到前面讨论的通信代价,显然交换网络比集中式总线更具有优势。

ICP架构的开放性主要通过两个技术特征来保证,一是将功能进行封装,定义标准统一的接口,二是具体实现技术应对功能透明。前一个特征保证不同承制商根据相同标准设计的组件是可以互换的,后一个特征保证了需求与技术的无关性,从而可以允许承制商选择低成本商用货架构件(COTS[4])来实现组件。

2 综合核心处理机设计实例

本文给出的ICP设计实例主要用于机载射频类传感器的数据计算功能,以及整个系统的控制、调度和管理功能。

ICP对外采用光纤通道(FC)网络与3个传感器前端和1个模拟显控互连,通过FC网络可以直接实现ICP内部模块之间,以及ICP与外部的高速数据传输。此外,ICP对外还采用CAN总线、RS485总线、离散量等同备份控制等机载设备互连。供电方面,ICP输入270 V DC高压直流电源,通过电源模块转换为28 V直流电压供给内部其他模块使用。ICP中提供两块电源模块,支持双余度供电及电源管理。

2.1 硬件架构设计

ICP中的硬件资源采用模块化封装,结构采用传导散热及盲插设计。方案设计时,参考联合标准航空电子委员会(ASAAC)的模块设计规范,对不同模块的功能、性能、组成结构、对外接口、结构、供电等进行了详细的定义,并尽可能地将不同模块中类似功能单元的技术要求进行归一化处理,形成标准功能单元,这些标准功能单元主要包括模块支持单元(MSU)、处理单元、路由单元(RU)、网络接口单元(NIU)、电源支持部件(PSE)和模块物理接口(MPI),如图2所示。

图2 通用功能模块内部组成Fig.2 General structure of the CFM

模块支持单元(MSU)由非易失存储电路(NvRAM、FLASH)、测温电路、授时对时电路、RTC电路、模块内部通信电路组成,主要用于支持模块的BIT监测、时间管理、状态记录等功能。通过MSU,ICP可以实现对模块的计时和温度监测功能进行维护。此外,MSU内部存储的模块制造商名、序列号、生产日期、CFM类型、硬件版本号、软件版本号、网络数量、网络接口类型、网络ID等嵌入式信息可用于支持模块动态配置、维修、升级等操作。模块内部通信电路主要包括SRIO交换电路、Mailbox电路,用于支持模块内部两个处理单元之间的高带宽、低延时通信功能。

处理单元(PU)提供模块的具体功能,其组成配置因各模块功能不同有着明显的差异,用于提供不同的功能特征。例如数据处理单元(DP)的构成为标准的商用处理器及大容量动态存储器(SDRAM),而大容量存储的处理单元(MMM)的构成则为商用处理器+SDRAM+非易失大容量存储器(64 GB)。

路由单元(RU)提供模块内部的网络接口单元(NIU)、处理单元(PU)和模块支持单元(MSU)之间的互联通信功能。RU也提供网络输入链路和网络输出链路之间的直接互联。由于本实例的ICP模块采用的处理器集成了RU的功能,因而不需要再设计单独的RU电路。

网络接口单元(NIU)执行模块处理单元对外的网络通信功能,主要由FC协议处理电路、电/光转换电路和光收发电路组成,用于实现FC网络接口功能。

电源支持部件(PSE)提供外部统一电压转换至模块内部的电压功能,即将电源模块输出的直流电压转换为模块内部电路工作所需的直流电压。

模块物理接口(MPI)定义模块的物理特性、机械结构、光接口、电接口和冷却接口等,在进行具体设计时,对模块的壳体、拔插组件、锁紧装置和连接器类型等进行了统一。

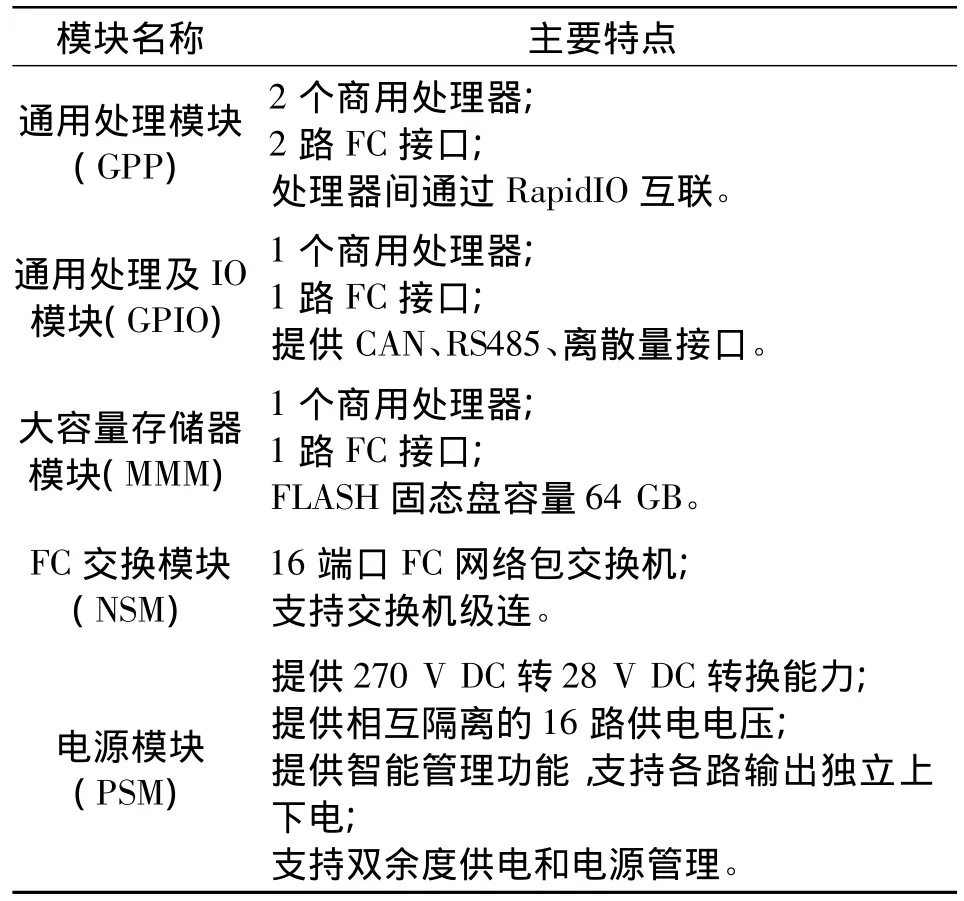

通过采用上述标准功能单元组成模块,保证了ICP内部模块的标准化和通用化。本实例中ICP内部的模块共有5种,如表1所示。

表1 ICP模块类别Table1 The ICP module class

2.2 软件架构设计

ICP中的软件采用层次化系统结构,包括用户软件层、软件隔离层和模块支持层,在不同软件层之间定义有开放式标准接口,使得不同厂家开发的软件可以很方便的进行集成。整个ICP的软件层次如图3所示。

图3 ICP软件架构Fig.3 Software architecture of the ICP

各层软件功能定义如下:

用户软件层:包括用于完成各种传感器信号处理和数据处理的软件、传感器系统控制管理软件等,该层软件的特点是完全与平台具体实现无关,可以在ICP内部同类模块之间动态加载和运行,也很容易在不同ICP平台之间迁移;

软件隔离层:包括操作系统和软件中间件,为用户软件提供多种服务,如操作系统服务(包括进程管理、存储管理、设备管理、文件系统管理、网络协议以及系统应用等几部分)、文件操作(本地和远程)服务、数据通信服务、交换网络管理等,同时向用户软件屏蔽平台实现差异,实现多任务管理、硬件资源管理以及ICP对外数据交互等;

模块支持层:主要对操作系统和软件中间件提供硬件访问的支撑服务,包括硬件驱动程序、硬件自检(BIT)、网络链路层协议管理、ICP系统引导、程序固化、外部接口操作等功能。

ICP中操作系统配置的是风河公司的Vx-Works5.5产品。由于VxWorks具有较好的可剪裁性,允许用户自定义系统,因此VxWorks操作系统本身提供了良好的接口定义,用于和应用软件以及硬件驱动之间的接口。因此,ICP不同软件层之间的接口定义是在VxWorks操作系统提供的接口基础上进行进一步的细化、封装和规范,以保证接口的兼容性和开放性。

通过软件的层次化设计、软件接口的标准化设计,对应用层软件屏蔽了底层细节,再结合模块通用化设计,使得应用软件在ICP内部可迁移,功能可重构。

2.3 总线互连设计

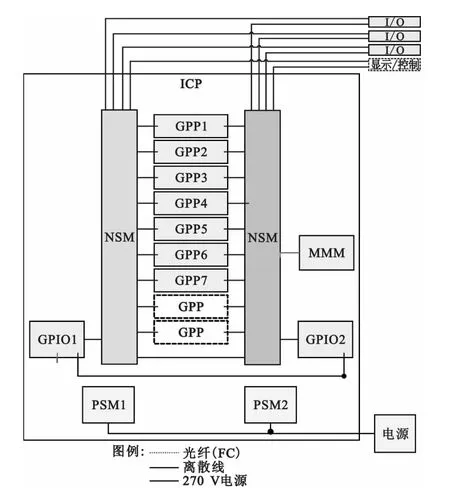

ICP内部模块之间采用FC交换网络互连,同时该网络也是ICP与外部航电设备交互数据的主干通信网络。FC网络的交换结构以2个16端口FC交换机(NSM)为核心,通过NSM级连成一个具有30个通信端口的大规模星型交换结构。整个互连拓扑如图4所示。

图4 ICP内外连接图Fig.4 Connection of the ICP

整个ICP的模块间FC网络由交换模块(NSM)和网络接口单元(NIU)共同组成,采用航空电子环境FC协议(FC-AE),使用匿名消息传输(ASM)[5]。

NSM模块采用无阻交换结构,提供16路2.125 Gb/s通信速率的FC交换端口,在 FC二层(帧和信号层)提供用于网络通信的高速互联接口,满足 FC-FS、FC-PI-4 以及 FC-SW-2 协议标准要求,并支持路由表远程动态加载,支持单播、组播以及广播通信方式,支持网络隐式注册和注销功能。单块NSM点到点无阻交换效率大于线速的90%,约 180 MB/s,端到端交换延迟不大于 12.5 μs,两块NSM级联端到端交换延迟不大于30 μs。

各模块中网络接口单元(NIU)对模块内部提供基于标准的PCI、PCI-E或RapidIO总线的主机通信接口,对外提供2.125 Gb/s通信速率的FC光纤接口,其硬件包括协议处理、通信配置存储器、消息收发缓冲、设备管理控制器、光收发器等部件,能独立完成ASM协议的消息收发调度、FC协议组帧/解析以及数据收发错误处理等功能。NIU与模块内部处理器之间采用DMA数据传输机制来提高从FC网络上收发数据的效率。

通过采用上述资源互连设计,可大大降低传输模型中的Ts、TO参数,并且提高通信代价模型中的TOL参数。在Ts方面,由于采用DMA传输机制,处理器启动一次传输只需要花费十几个程序周期的固定开销。在TO方面,由于NSM的设计时延为小于12.5 μs,NIU中采用FPGA硬件逻辑实现协议处理及缓存管理,因此其时延根据数据包的大小不同大概在几微秒到几十微秒,因此整个TO最大为几十微秒。此外,由于NSM采用的是无阻交换结构,因此在目的地不相同时,多个并发传输之间不存在资源抢占的问题。另一方面,由于NIU能独立完成FC网络数据的收发以及消息管理等工作,因此除了发送数据时需要处理器启动DMA会占用极少的处理器时间外,大部分的通信代价能被程序的并行性所抵消。

3 综合核心处理机实现结果

在最终实现的 ICP样机中,功能电路方面,GPP、GPIO、MMM 3 类模块的处理单元(PU)、模块支持单元(MSU)、网络接口单元(NIU)和电源支持部件(PSE)实现了通用化设计,其中PU配置包括PPC8641 处 理 器、512 MB 的 DDR II SDRAM、128 KB的NvRAM以及128 MB的FLASH;MSU配置包括PPC8641调试接口、时间同步逻辑、RTC、模块复位电路等;PSE配置28 V DC转5 V DC、3.3 V DC等所需工作电压的电压转换电路;NIU配置包括用于FC协议处理及PCI-E接口协议处理的FPGA、光电收发接口以及高速数据缓存电路。根据模块的功能不同,上述通用单元的数量配置略有差异,例如,GPP配置了2个PU和2个NIU,而GPIO和MMM则只配置了1个PU和1个NIU。

此外,在机械、冷却和电气接口方面,ICP中各类模块也实现了归一化。各模块的结构形式相同,由模块壳体、连接器、拔插组件、锁紧装置组成,模块外形尺寸为160 mm(宽度)×233.4 mm(深度),厚度除了PSM为39 mm外,其他均为24 mm,各模块的拔插组件、锁紧装置等均可互换。在电气接口方面,除了PSM和NSM外,其他模块的电连接器完全相同,都通过一个有光信号、电信号和电源信号的连接器与母板进行通信。ICP中各模块采用传导冷却,模块的热量通过模块壳体传导至机架侧壁,由机架将模块热量带到机架外部。

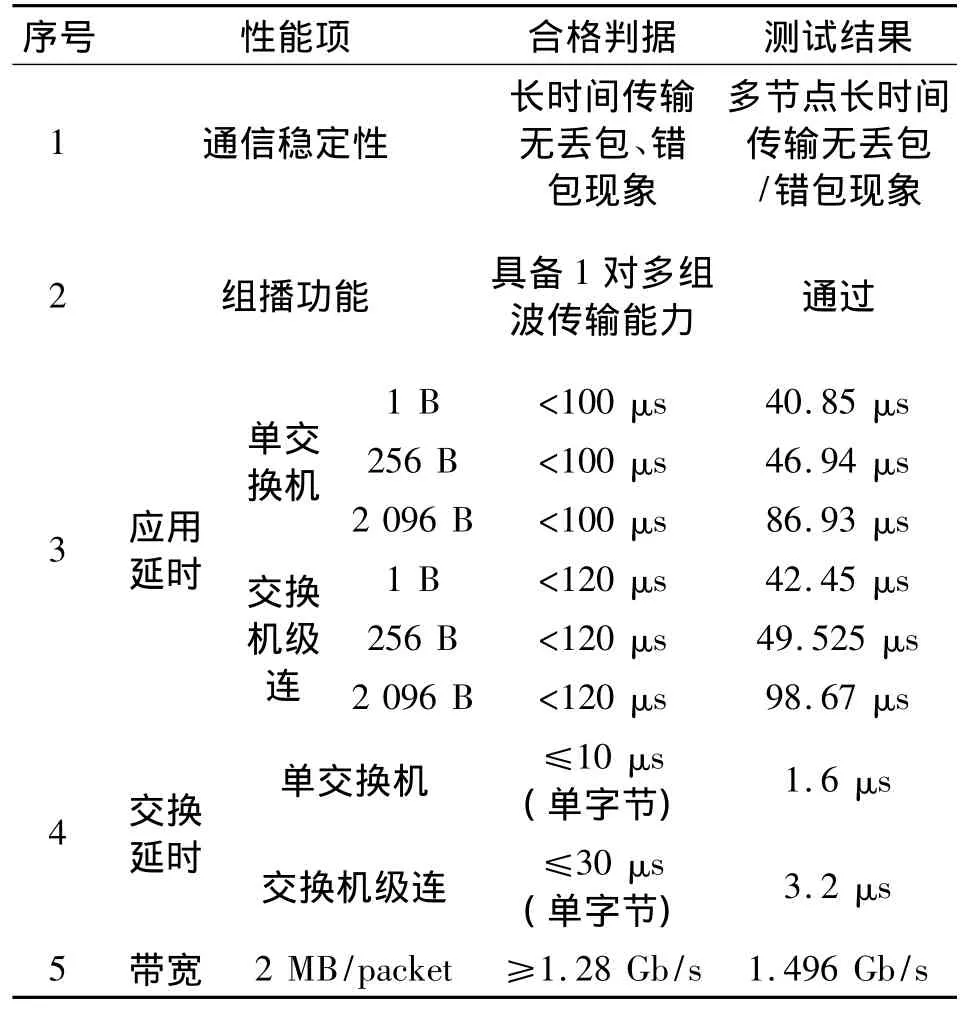

在性能方面,整个ICP共包括16个工作频率为1 GHz(单片极限处理能力为2.3 GIPS)的PowerPC处理器,每个处理器配备有独立的512 MB的DDR II SDRAM用于程序和数据的高速缓存,任意两个处理器之间可以通过全交换的FC网络进行通信,该网络的传输性能测试结果如表2所示。表中应用延时是指处理器应用软件层所观察到的数据传输延时,主要包括FC协议处理、数据串并转换以及数据收发缓存所花费的时间,最大为每字节42.45 μs,在大数据包传输时可进一步降低到每字节21.24 μs。考虑到数据传输主要由各模块的NIU硬件以及NSM共同完成,不占用处理器资源,传输和处理可以并发进行,因此通过合理地设计应用软件,通信代价CT(n)还可以大幅度降低。此外,全交换结构设计使得多点之间并发通信时交换机不会导致CT(n)恶化,能满足多传感器并发运行的需求。

在整个ICP实现的后期,新设计了SP模块和SPIO模块,用于实现光电传感器的信号处理和数据处理。这两种模块采用DSP实现PU单元,其他组成单元与GPP模块类似,充分证明了ICP架构的开放性和良好的扩展性。

表2 网络传输性能测试结果Table2 Performance test result of network transmission

4 结束语

综合核心处理机是航电系统高度综合化的重要组成部分。本文设计的核心处理机,通过对模块内部组成电路进行组件化、归一化的设计,软件层次化的设计,接口的标准化、归一化设计,无阻塞全交换互连网络设计以及底层通信支持部件的自主通信管理设计,在实现ICP内部资源通用化、功能可重构以及架构开放性的同时,还保证了ICP具备强大的运算性能、良好的扩展性。实现结果表明,通过上述设计,各功能模块内部四分之三的电路组成可以完全一样,大大降低了系统的集成和维护难度。此外,在通信代价方面,不考虑通信与计算重叠时,启动一次数据通信代价大约耗时42 μs,在考虑通信与计算重叠时,理想情况下通信代价可以优化到纳秒量级。

[1]Moir I,Seabridge A.军用航空电子系统[M].吴汉平,译.北京:电子工业出版社,2008.Moir I,Seabridge A.Military Avionics System[M].Translated by WU Han-ping.Beijing:Publishing House of E-lectronic Industry,2008.(in Chinese)

[2]乔文昇.机载平台电子信息系统概述[J].电讯技术,2007,47(3):1-3.QIAO Wen-sheng.An Overview of the Electronics Information System for Airborne Platforms[J].Telecommunication Engineering,2007,47(3):1-3.(in Chinese)

[3]Culler D E,Singh J P,Gupta A.并行计算机体系结构[M].李晓明,译.北京:机械工业出版,2002.Culler D E,Singh J P,Gupta A.Parallel Computer Architecture[M].Translated by LI Xiao-ming.Beijing:Machinery Industry Press,2002.(in Chinese)

[4]刘国灿,刘锦德.基于COTS的系统综述[J].计算机应用研究,2003,20(1):5-7.LIU Guo-can,LIU Jin-de.An Overview of COTS-based Systems[J].Application Research of Computers,2003,20(1):5-7.(in Chinese)

[5]王世奎,王国庆,王红春,等.航空电子光纤通道高层轻量协议的研究[J].航空计算技术,2007,37(2):108-111,115.WANG Shi-kui,WANG Guo-qing,WANG Hong-chun,et al.Research on the High-level Lightweight Protocol of Fibre Channel in Avionics Environment[J].Aeronautical ComputerTechnique,2007,37(2):108 - 111,115.(in Chinese)