一种改进的多模数字下变频结构及其FPGA实现*

张庭伟,袁正午,周 牧,田增山

(重庆邮电大学移动通信技术重庆市重点实验室,重庆400065)

1 引言

随着3G和LTE的不断发展,多模终端将成为移动终端的发展趋势。多种通信模式的共存对于移动终端用户而言,就是迫切需要支持多个频段和多种模式的终端,这样可在多种不同制式的系统之间自由切换[1]。而随着3G牌照的发放,3种不同的3G网络覆盖方案共存的局面已经不可避免,再加上目前国内TD-LTE正如火如荼地推广,多模终端无疑将成为运营商和终端用户的首选[2]。目前,绝大部分移动终端为GSM和3G的共存,而TD-LTE与3G共存的移动终端,在业界仍还处于萌发期。而传统的数字下变频只能实现特定制式的处理,无法实现单系统多模式的功能。

基于此,本文提出一种能够兼容多种模式的数字下变频结构,并且完成各模块Verilog代码编写和Modelsim仿真;最后将代码移植到FPGA,并结合ETTUS射频板、自主设计的中频板以及友晶TR4 FPGA开发板多模硬件平台进行了板级调试,验证了多模功能的可行性。

2 改进DDC系统结构设计

图1为设计的多模数字系统结构框图,数字下变频是整个多模系统的核心,完成系统下变频和降采样的任务。

图1 多模数字系统结构框图Fig.1 Structure diagram of multimode digital system

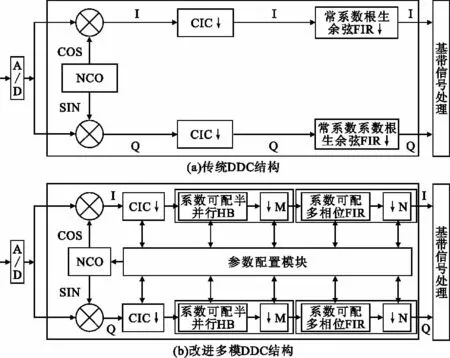

由于传统DDC各级滤波器参数一旦配置完成,便无法实时更改,从而大大降低了系统的灵活性,无法满足系统多模需求[3]。于是,通过对各模式以及DDC各模块的分析,对相关模块进行改造,以适应多模系统的需求。图2为传统DDC结构和改进DDC结构的对比。

图2 传统与改进数字下变频结构框图Fig.2 Structure diagram of traditional and improved digital frequency conversion

图2 中,(a)为传统DDC结构,其采用常系数滤波器,无法适用于多频多模需求且处理效果欠佳;而(b)为改进的多模DDC结构,其各级模块参数均可以实时修改,且采用滤波特性较好的半并行HB及多相位FIR滤波器实现,具有较好的高效性和实用性。

3 数字下变频模块设计

数字下变频技术是应用软件无线电系统中的核心技术之一[3]。软件无线电的核心思想是:构建一个模块化程度高且开放性强的通用平台,将各种需要实现的功能用软件编程来实现,并使数字化处理(A/D)器件尽可能地靠近射频天线,让所有的信号处理都在数字域中进行[4]。

DDC是数字中频在A/D变换后的数字处理部分,可以有效降低采样频率,即通过降低数据量,以达到减轻基带处理对DSP计算需求压力的目的[5]。下面基于改进的DDC结构对各级模块进行阐述。

3.1 NCO模块设计

NCO模块能生成一组严格正交、稳定、频率可控的正余弦信号。选用CORDIC算法的IP核完成NCO设计,CORDIC无需使用乘法器,只需一个最小的查找表,利用移位和加法运算,即可产生高精度正余弦波形,非常有利于FPGA实现[6]。Altera提供的IP核性能卓越,精度高达10-9,能够很好地完成下混频的任务。

3.2 CIC抽取滤波器模块设计

随着现代无线通信中数据传输率不断增加,CIC滤波器的应用显得尤为重要。CIC滤波器只包含加法器、积分器和寄存器,没有乘法器,因此适合高采样率电路。此外,CIC滤波器是一种基于零极点相消的FIR滤波器,在高速抽取系统中可以得到有效利用[6]。由于Altera提供抽取率可变的CIC IP核,故采用IP核完成第一级抽取滤波器设计,可有效缩短开发周期。

3.3 半并行半带滤波器模块设计

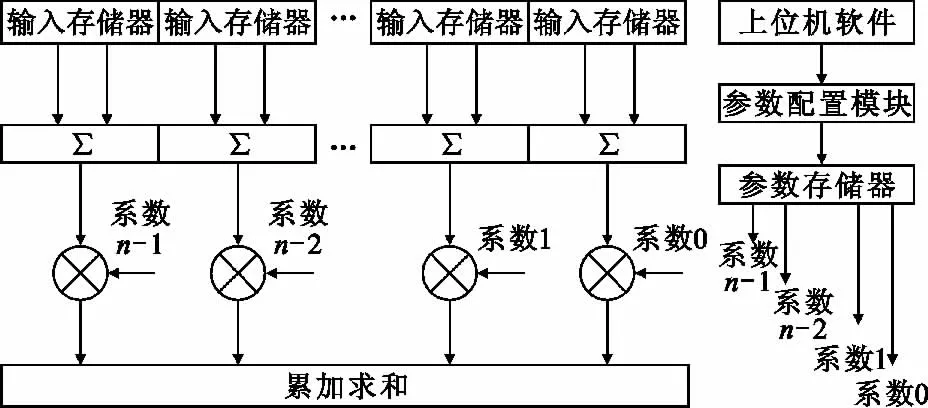

HBF适用于实现D=2M倍抽取,由于减少了一半存储和计算量,故在高速处理中具有计算效率高,实时性强等优点。常系数HBF无法根据制式的不同配置不同特性的滤波器系数,故设计了图3所示的可配置半并行HBF结构,设置HBF各参数为HBF模块的输入接口,由上位机通过参数配置模块根据所选模式对滤波器参数进行配置,参数可配置是设计的重点。采用这种滤波器完成第二级抽取滤波的设计,兼顾灵活、速度和资源的有效整合。

图3 可配置半并行HBF实现框图Fig.3 Structure diagram of configurable half-parallel filter

图3 结构的HBF滤波器,通过改变抽头系数和参数存储器中的滤波器系数,还可以将其灵活地运用于实现高通、带通和带阻滤波器,可移植性好,在提高系统运算速度和提高系统输入取样率方面具有很大优势。此结构不仅能实现滤波器参数的灵活配置,还能提高处理速度和资源消耗。

3.4 多相FIR滤波器模块设计

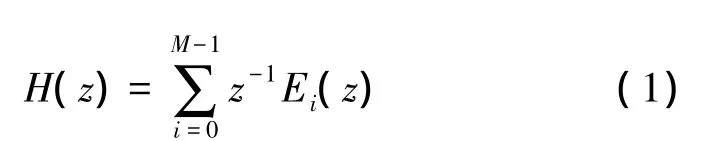

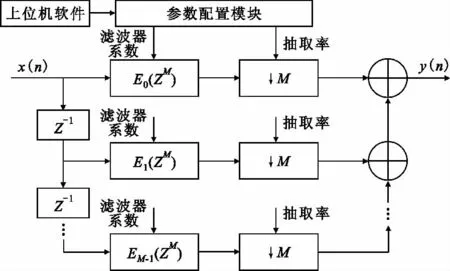

因为HB滤波器所具有的较大过渡带,不能满足滤波特性的总体设计要求,因此不适合作多级滤波器的最后一级[3]。信号经两级抽取滤波后,数据速率比较低,采用具有更高阶频率特性的多相FIR滤波器,作为最后一级滤波,具有更好的通带波动、过渡带宽和阻带抑制等性能[7]。多相滤波器在信号速率转换过程中去掉不必要的计算,同时在抑制镜像和邻频道干扰上具有较好的性能,可大大提高运算速度和信号质量。为将该滤波器运用于多模DDC中,设计了图4所示可配置多相FIR滤波器结构,其参数也是可灵活配置的。其传递函数表达式如式(1)所示:

图4 可配置多相FIR滤波器实现框图Fig.4 Structure diagram of configurable multiphase FIR filter

该结构实现滤波器参数的灵活配置,且运算单元在输出抽样的周期内的所有时刻都在工作,虽占用了一定的资源,但大大提高了滤波器的效率。

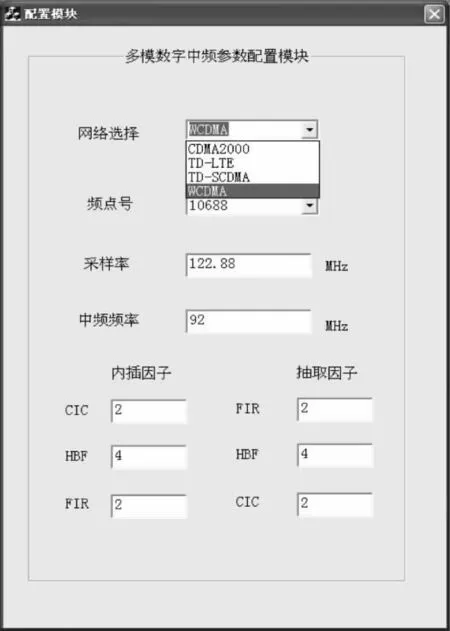

3.5 参数配置模块设计

参数配置模块是上位机软件与FPGA通信的中间模块,能够根据上位机选择的模式,对系统参数进行对应配置,以满足多种模式系统的需求。参数配置模块将需要配置的接口作为输入,将要设定的参数写入上位机软件中,运行后将参数配置到FPGA内的参数配置模块对应的寄存器中,从而完成不同模式下系统参数的配置。图5给出了参数配置模块的上位机界面。

图5 参数配置模块的上位机界面Fig.5 Computer interface of parameters configuration module

4 实验验证及结果分析

4.1 参数分析

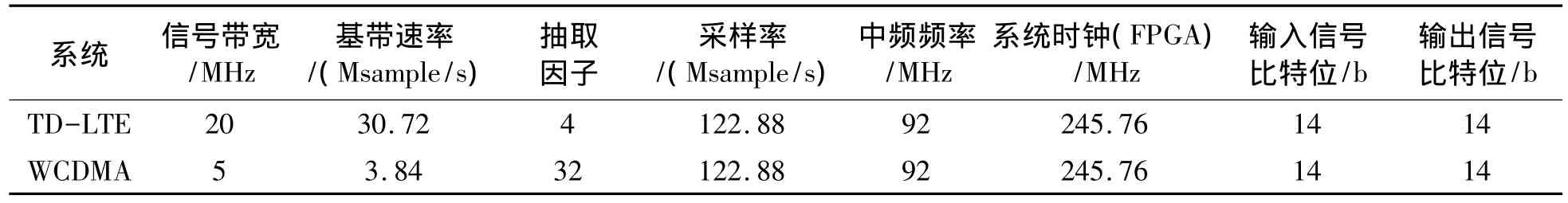

由于3G制式中WCDMA的带宽最宽,其他两种制式原理和WCDMA相同,所以主要针对TDLTE和WCDMA两种模式进行实验和分析。它们的参数如表1所示。

选用4种制式码片速率的公倍数245.76 MHz作为系统时钟频率为数据串并转换提供时钟,122.88 Msample/s为采样率以便实现整数倍抽取。由于抽取系数较大,若采用一级进行抽取,则滤波器的阶数较高,占用资源较多且不易实现,所以实验采用滤波器分级抽取,以降低滤波器阶数。本设计为3级滤波器,故分解为3级抽取。考虑到CIC和HBF阶数较小且便于数据率尽快降下来,将抽取系数大的放在前端,故TD-LTE系统的CIC、HB和FIR的抽取率依次为2、2和1,WCDMA(2倍基带速率)系统 的CIC、HB和FIR的抽取率依次为2、4和2。

表1 TD-LTE和WCMDA下变频参数Table1 DDC parameters on TD-LTE and WCDMA

4.2 软件仿真

根据表1设置数字下变频参数,并通过Modelsim进行仿真,验证系统可行性。选择TD-LTE制式进行可行性验证。考虑到硬件平台的设计,选用92 MHz的中频频率。由于采用122.88 M的采样率,采样后得到30.88 MHz中频信号。NCO产生30.88 MHz的正余弦信号,作为本振信号,与中频信号相乘,得到零频信号,再经过CIC、HB及FIR滤波器完成抽取滤波,将数据率降下来。

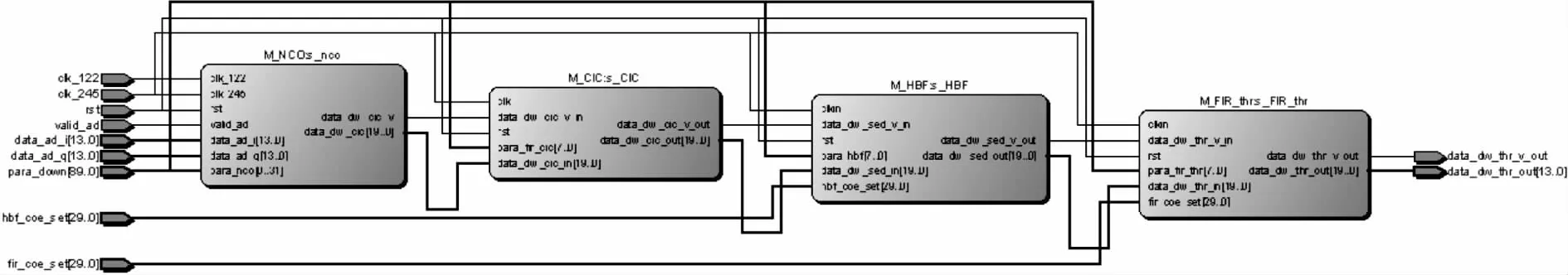

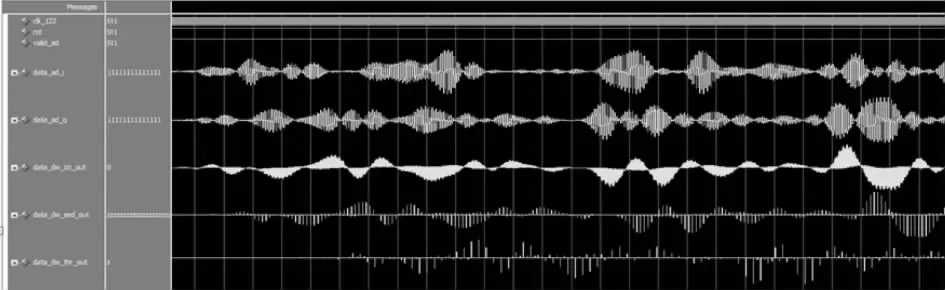

图6为QuartusⅡ中数字下变频代码的RTL级结构。其中 clk_122、clk245是由 AD9510提供给DDC系统的时钟,valid_ad为AD提供给DDC的使能信号,data_ad_i、data_ad_q为AD采样后的信号,para_down为各级抽取率配置入口,hbf_coe_set、fir_coe_set分别为HB、FIR滤波器的抽头系数配置入口;data_dw_thr_v_out为DDC输出使能,同时也是基带处理的使能信号;data_dw_thr_out则为DDC处理之后的信号。完成数字下变频设计后,进行Modelsim功能和时序仿真,并将每一级输出结果以文本形式保存,并用MATLAB绘制频谱。

图6 数字下变频模块RTL视图Fig.6 RTL view of DDC module

图7 为数字下变频的功能仿真时序图,data_ad_i、data_ad_q 分别为 I、Q 两路数据,data_dw_cic_out、data_dw_sed_out、data_dw_thr_out依次为 CIC、HBF和FIR输出,可以看到每一行输出都晚于上一行信号的输出。由于经滤波抽取处理,采样点逐级降低,但整体信号时域特性相似,将每一级数据保存为文本绘制频谱。

图7 TD-LTE的Modelsim仿真图Fig.7 Modelsim simulation diagram of TD-LTE

图8 为TD-LTE中频数据频谱,作为DDC的数据输入。图9为TD-LTE系统数字下变频频谱,其中,(a)为经NCO混频后输出信号;(b)为经CIC滤波2倍抽取后的信号频谱;(c)为半并行HBF滤波抽取后的信号频谱,最后经FIR滤波后的频谱如(d)所示。可见,信号信噪比较高,带外衰减达120 dB,验证了系统的高效性和可行性。

图8 TD-LTE中频频谱Fig.8 TD-LTE intermediate frequency spectrum

图9 数字下变频过程频谱Fig.9 Spectrums in DDC process

4.3 硬件测试

经Modelsim仿真验证后,将代码移植到FPGA芯片,通过上位机选择模式配置参数,接收对应模式数据进行处理。本系统采用ETTUS射频板,自主设计的中频板以及友晶科技TR4开发板作为硬件平台进行实验验证,如图10所示。

图10 数字下变频系统硬件平台Fig.10 Hardware platform of DDC

上位机软件选择要接收的模式并配置参数,上电加载后,信号由射频板天线接收下来,经三级放大后,由混频电路混频至中频;再经AD采样送至FPGA进行数字下变频处理;最后将处理后的数据输出以文本保存,在Matlab中进行同步验证。通过QUARTUSⅡ的在线逻辑分析仪,监视FPGA输入和输出管脚的状态,如图11所示,即为TD-LTE数据管脚的实时状态。

图11 DDC各级数据输出状态图Fig.11 All leves of state diagram of output data in DDC

上电后,射频端接收相应制式的信号并进行AD采样,送给DDC处理,将处理结果导出,在Matlab中进行同步检测,验证数据的有效性。通过上位机选择了WCDMA和TD-LTE模式进行多模验证。

图12为LTE系统下行同步PSS捕获仿真图,对LTE系统一帧数据(307 200个样点)进行仿真,其中PSS在一帧中发送两次。从图中可以看到,在PSS处有明显的相关峰值,在峰值处捕获到PSS,进而完成下行同步后续步骤,包括时间同步、频偏估计,验证了经过数字下变频处理以后的数据是有效的。

图12 LTE系统下行同步PSS捕获Fig.12 Downlink synchronization capture for PSS on LTE system

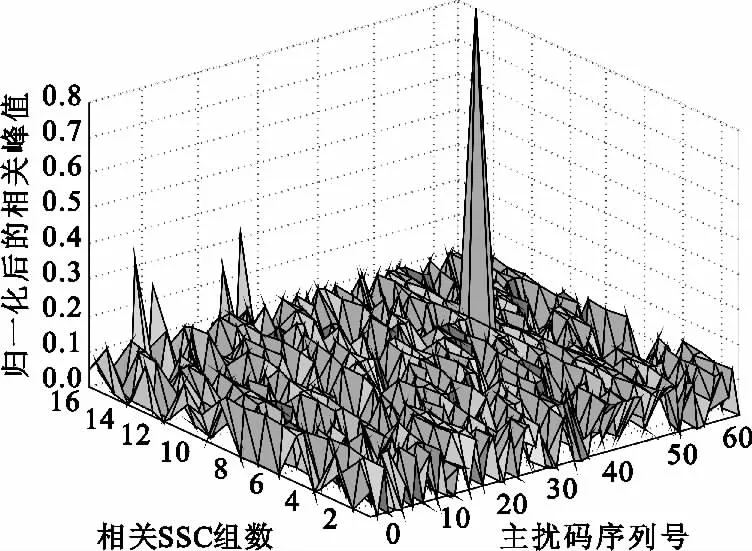

图13 为WCDMA系统下行帧同步仿真图,对WCDMA系统实际数据(768 000个样点)进行仿真。从图中可以看出,信号与辅助同步信道以及主扰码有非常明显的相关峰值,在峰值处捕获到帧同步的位置,进而完成下行同步后续步骤,验证了经过本系统的数字下变频处理后的数据是有效的。

图13 WCDMA系统下行帧同步Fig.13 Downlink frame synchronization on WCDMA system

5 结束语

针对目前多种通信模式共存所带来的系统兼容性问题,而以往研究中同一系统只能完成单一制式处理,于是对传统的数字下变频结构进行了优化改进,使其能够实现兼容多种模式下的数字下变频处理。实验结果表明,经过改进的数字下变频能够有效满足TD-LTE和WCDMA模式下的数字下变频要求,且无需构架不同模式平台,从而节约了资源,缩短了开发周期,并具有较高的实用性和通用性。针对GSM、IS95、CDMA2000以及TD-SCDMA等制式,本系统均可以进行处理,对未来4G、3G和2G的共存提供了平台。

[1]陈明,周健义,赵嘉宁.基于数字中频的多频多模系统的实现[C]//2005年全国微波毫米波会议论文集(第一册).深圳:中国电子学会,2006.CHEN Ming,ZHOU Jian-yi,ZHAO Jia-ning.Implementation of Multi- frequency and Multi- mode system based on DDC[C]//Proceedings of 2005 National Conference on Microwave and Millimeter-wave(Vlume One).Shenzhen:The Chinese Institute of Electronics,2006.(in Chinese)

[2]张学军,张孝林.多模移动终端芯片设计技术及多模终端发展现状[J].移动通信,2006(8):22-24.ZHANG Xue-jun,ZHANG Xiao-lin.Multimode mobile terminal chip design technology and the development situation of multimode terminal[J].Mobile Communication,2006(8):22-24.(in Chinese)

[3]徐双全,蒋宇中,江海.数字下变频技术的改进与FPGA实现[J].无线通信技术,2012,21(4):35-38,43.XU Shuang-quan,JIANG Yu-zhong,JIANG Hai.Improved and implementation of digital down converter based on FPGA[J].Wireless Communication Technique,2012,21(4):35-38,43.(in Chinese)

[4]张海峰,赵爱玲.基于 FPGA的高速 DUC设计与高效实现[J].电讯技术,2012,52(7):1112-1115.ZHANG Hai-feng,ZHAO Ai-ling.The design and high-efficient implementation of high-speed DUC based on FPGA[J].Telecommunication Engineering,2012,52(7):1112-1115.(in Chinese)

[5]Pang L,Zhu B,Chen H,et al.A highly efficient digital down converter in wide band digital radar receiver[C]//Proceedings of 2012 IEEE 11th International Conference on Signal Processing.Beijing:IEEE,2012:1795-1798.

[6]何立志,邱洋,何松.软件无线电数字下变频技术研究及 FPGA实现[J].电子技术应用,2010,36(11):23-26.HE Li-zhi,QIU Yang,HE Song.The research and implementation of Software radio digital down converter technology based on FPGA[J].Application of electronic technique,2010,36(11):23-26.(in Chinese)

[7]Zhang Q,Su X.The Design of Digital Down Converter Based on FPGA[C]//Proceedings of 2012 8th International Conference on Wireless Communications,Networking and Mobile Computing.Shanghai:IEEE,2012:1-4.