基于FPGA的IP承载网损伤仪设计

李 星,张治中

(重庆邮电大学通信网与测试技术重点实验室,重庆 400065)

基于FPGA的IP承载网损伤仪设计

李 星,张治中

(重庆邮电大学通信网与测试技术重点实验室,重庆 400065)

针对IP承载网的结构和技术特点,结合目前网络性能测试的现状和需求,提出了一种基于FPGA的IP承载网损伤仪的系统框架,研究了在FPGA上实现模拟丢包率的方法,阐述了损伤仪硬件模块的设计思想。该方案在仿真测试上通过验证,有着良好的应用前景。

IP承载网;FPGA;损伤仪;正态分布;Modelsim仿真

随着IP承载网的发展,业务的快速增长不断给网络提出更大的挑战,低成本、大容量、传输的高可靠性和安全性成为了IP承载网追求的主要目标[1],因此在IP承载网的建设中需要对网络性能进行一系列的评估和测试,但现有的网络性能测试无法对实际情况中出现的网络延迟、设备故障和数据丢包等问题进行比较准确的估计,这在很大程度上阻碍了IP承载网的发展。为了能够更好地解决IP承载网建设中出现的各种问题,避免因对实际情况估计不足而导致网络建设的缺陷和漏洞,本文设计一种基于FPGA的IP承载网损伤仪,能够模拟在丢包率、时延、抖动和带宽限制等环境下的网络传输情况,对IP承载网的长期发展具有重要意义。

1 IP承载网性能评估

目前IP承载网的建设主要处于网络转型阶段,它的基本结构如图1所示[2]。

随着业务对网络性能的要求越来越高,运营商需要投入更多的资金来保障所承载业务的质量,包括调整网络结构、降低故障发生率、降低运行维护成本等,因此在现阶段必定要求运营商对IP承载网的性能进行评估[3]。以下几个方面对IP承载网的运营和维护有着极其重要的影响,主要包括:

图1 典型的IP承载网架构图

1)吞吐量(Throughput)。测试路由器包转发的能力。在没有帧丢失的情况下,设备能够接收并转发的最大数据速率。

2)时延(Latency)。一个报文或分组从一个网络的一端传送到另一端所需要的时间。它包括了发送时延、传播时延、处理时延、排队时延。

3)丢包率(Packet Loss Rate)。测试中所丢失数据包数量占所发送数据包的比率,通常在吞吐量范围内测试,丢包率的大小与数据包长度以及包发送频率相关。

4)抖动(Shake)。如果网络发生拥塞,排队延迟将影响端到端的延迟,并导致通过同一连接传输的分组延迟各不相同,抖动就是用来描述分组延迟变化的程度。

参照以上的参数指标,设计损伤仪来模拟不同状态下的网络传输情况,能够对IP承载网的网络性能分析提供测试环境。

2 损伤仪的设计与实现

IP承载网损伤仪是一个独立的整体,它由多个模块构成,包括软件控制和硬件平台两大部分,本文主要从FPGA方面来阐述损伤仪的设计与实现。本节内容详细分析了如何利用获取的正态分布随机数来模拟丢包率以及系统各个主要硬件模块的设计思想。

2.1 模拟丢包率

传统的模拟方法是向链路中持续发送模拟数据包,当模拟数据包占满链路时就可以得到最大可用带宽,但是这种方法在进行时延、丢包等测量时需要多台仪表配合,并且由于各台仪表的时钟不同步或者路由限制等问题无法得到准确的测量结果[4],因此本文设计利用较少的FPGA硬件资源,通过获取外部噪声源中的正态分布随机数来模拟丢包率,类似的方法还可以模拟时延、抖动、带宽限制等,图2所示为IP承载网损伤仪的总体框架图,使用一台损伤仪就能为IP承载网的性能评估测试提供不同的环境[5]。

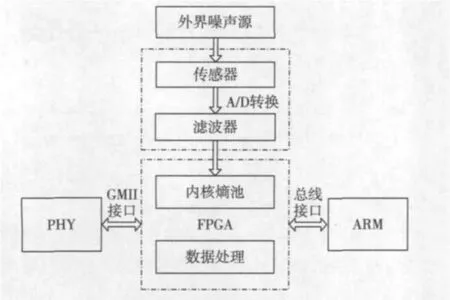

图2 IP承载网损伤仪总体框架图

在模拟网络损伤环境时,例如在指定丢包率下,无法确切地知道数据包在哪一时间段内发生丢包,但是整个丢包的过程是服从正态分布的,因此只要得到有效的正态分布随机数就能够模拟丢包状态下的数据传输情况。利用计算机的算法无法得到真正意义上的随机数[6],但是自然环境中存在的各种各样的噪声,如热量、声音、电流等,甚至机器中的中断时间,用户点击鼠标的时间间隔等都是完全随机的。因此在已知外部噪声符合正态分布的情况下,可以将得到的外部噪声信号源进行处理变成需要的正态分布随机数。

外部噪声源在真正意义上完全符合正态分布,利用传感器将外部噪声源的随机信号进行采样,经过模数转换后传入滤波器,滤波器处理后将有效的信号存入熵池,FPGA就能从熵池中读取随机数源。

设从熵池中得到的多个随机序列为X1,X2,…,Xn,它们相互独立且服从正态分布N(μ,δ2),因此可以得到样本均值为

样本方差为

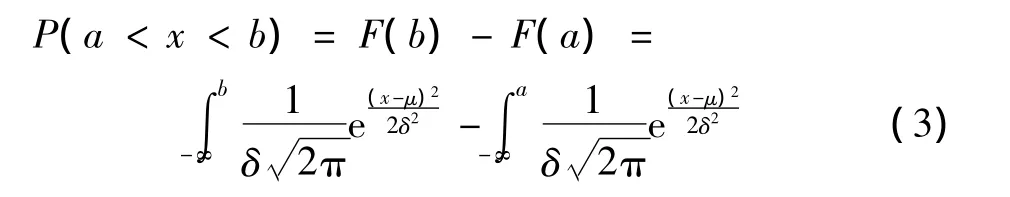

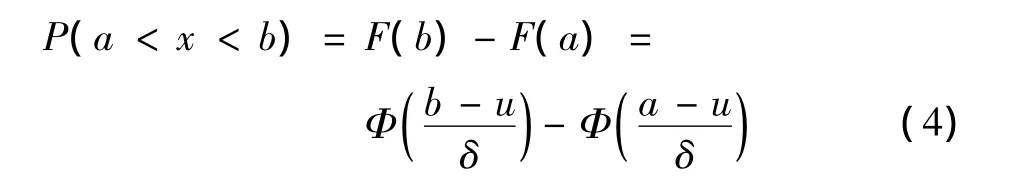

模拟丢包率就是对正态分布区间的概率值进行计算,若a和b是x的两个定值,则可以根据下式计算区间(a,b)的概率

对于标准正态分布,由于它的平均数μ=0、标准差δ=1,因此很容易得到它在某个区间内的概率值,而对于具有平均数为μ、标准差为δ的一般正态分布,只要将它们转化为标准的正态分布,对照正态分布概率表就能够获得随机变量x落入在某个区间内的概率[7]。

将式(1)和式(2)代入式(4)可以求得正态分布任意区间的概率值,同理若已知丢包率的值就可以根据正态分布概率表,求得它在正态分布中所在的区间位置。

若已知设定的丢包率为e,则P(a<x<b)=F(b)-F(a)=e,查表得到它在标准正态分布中的位置在(-k,k),根据式(1)和式(2)得到正态总体X的样本均值μ和样本方差δ的值,所以根据式(4)可以求得b=kδ+μ,a=μ-kδ,即FPGA会在正态分布区间(a,b)内任意位置随机模拟丢包的发生。

通过查标准正态分布表比较容易得到对称区间内的概率值,当然在其他区间也可以得到满足条件的概率值,但依照式(3)比较难得到对概率密度函数积分的结果,因此采用上述将一般正态分布转换为标准正态分布,再通过查表的方式来计算概率值在正态分布中所处的区间位置。

2.2 主要硬件模块的设计

2.2.1 FPGA 模块

FPGA是整个损伤仪系统的核心,完成对网络损伤状态下如丢包率、时延、抖动等环境的模拟和数据在系统内的处理等功能,FPGA的总体设计框架图如图3所示。

图3 FPGA模块的总体框架图

FPGA通过总线接口和GMII接口与ARM和PHY相连接,当数据从外部网络传入系统后,FPGA会统一协调各个模块的工作状态,对数据进行相关的处理,根据相应的系统配置与ARM的传输指令分配硬件工作资源,最后将处理得到的数据结果传至上层。

对滤波器传过来的数字信号进行处理分析,根据上述模拟丢包率的方法,模拟指定丢包率下的数据传输情况,除此之外还可以提供时延、抖动和带宽限制等网络损伤环境。

根据FPGA与ARM的命令交互格式对寄存器进行相关的设置,包括网络访问地址、基础状态、MAC配置、模拟网络损伤环境和测试结果等,驱动程序向寄存器访问地址配置上相应的信息,FPGA根据配置信息执行相关的操作。

2.2.2 ARM 模块

ARM模块是损伤仪系统中上层软件与底层硬件交互的枢纽,承载提供测试界面的操作系统,对数据信息进行处理。

ARM通过接口与各个模块相连,根据相关的参数设置对其他模块和系统的工作状态进行切换和控制。

ARM与FPGA进行命令交互时的大部分数据操作在寄存器中完成,只有加载/存储指令可以访问存储器,使得指令执行速度更快,效率更高。

ARM的运行模式可以根据上层传输指令进行改变,也可以通过外部中断或异常处理改变。

2.2.3 PHY 模块

PHY是与外部信号接口的芯片,在损伤仪系统中将外部网络与FPGA模块进行互联,是损伤仪与外部连接的重要模块。

PHY将定义的数据传输信号类型、线路状态、发送地址信息和数据校验信息等通过RJ45接口发送到外部网络,还向网络层提供寻址机构和标准的数据接口。

3 仿真测试结果验证

3.1 验证正态分布随机数

根据以上设计思路,FPGA对从熵池中得到的多个正态分布随机样本进行分析,模拟指定丢包率下的数据传输情况。图4为得到的标准正态分布曲线图。

图4 标准正态分布曲线图

此法用到多块RAM,每块RAM储存多个随机信号的采样数据,最终输出速率主要由FPGA的速度决定,如果需要进一步提升运行速度,可以降低采样精度或者缩短随机数的生成周期。设置指定数据(如丢包率30%)传入FPGA进行模拟测试,根据上述方法,对照标准正态分布概率表,损伤仪在标准正态分布区间(-0.39,0.39)任意位置随机模拟丢包发生。同理若已知随机样本为一般正态分布,它的平均数为μ=30、标准差为δ=10,则根据式(4)可以算出损伤仪在正态分布区间(26.1,33.9)的任意位置随机模拟丢包发生,在其他区间则按正常情况发送数据包。

3.2 模拟仿真测试

根据以上的设计方案,基于Xilinx Vertex 6工具,使用Verilog语言对硬件逻辑进行描述,在Modelsim上进行仿真测试[8],模拟指定丢包率下的数据传输情况。

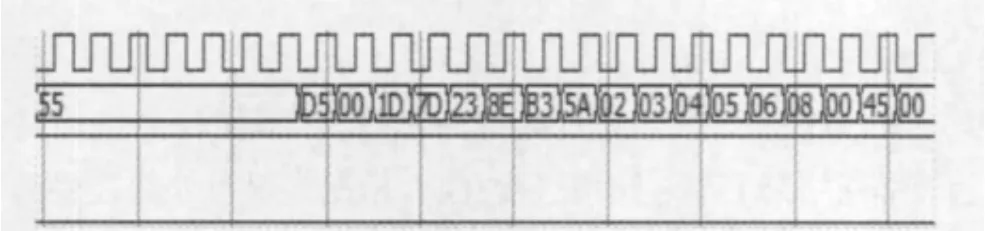

图5所示为Ethernet_II的部分数据帧结构。包括了8 byte长的前导码,6 byte长接收端的MAC地址,6 byte长发送端的MAC地址,2 byte长的数据包的类型,以及46~1 500 byte长被封装的数据包和4 byte长的错误检验码。

图5 Ethernet_II的部分数据帧结构

按照上述所示帧格式,在Modelsim上进行丢包率的模拟测试。由图6可以看出,在120 008~141 438 ns时间段内发出了30个数据包,设置丢包率为1/3,则每发3个数据包就有1个数据包被丢弃,例如在128 600~130 510 ns时间段内发送了3个数据包,在129 822~130 510 ns时间段内丢弃一个数据包,其他时间段同样得到了此结果。最后测试结果得到了20个数据包,符合1/3的丢包率,此方案达到设计目的。

图6 模拟丢包率仿真截图

4 结束语

本文对当前IP承载网性能测试的需求进行分析,提出一种基于FPGA的IP承载网损伤仪系统的设计方案,研究了利用正态分布随机数模拟丢包率的方法,阐述了各个功能模块的设计思想,最终得到了性能较好的正态分布随机数,并在仿真测试上通过了验证。本设计方案能够为IP承载网的性能评估测试提供不同的模拟环境,达到了预期目的,有着良好的应用前景。

:

[1]OHIZE H O,ONWUKA E N.Impact of differentiated service billing on the quality of service of an IP network[C]//Proc.the 2010 2nd International Conference on Computer Technology and Development.Minna,Nigeria:ICCTD,2010:739-743.

[2]LUO Chuanfei,SUN Jun,XIONG Hongkai,et al.Design and implementation of an end-to-end system importing DTV from broadcasting network to broadband IP network[C]//Proc.the 2004 IEEE Asia-Pacific Conference on Circuits and Systems.[S.l.]:IEEE Press,2004:777-780.

[3]SUSUMU Y,TERUMASA A.Simple IP network based on QoS free concept[C]//Proc.the IEEE International Conference on Communications.Tokyo,Japan:IEEE Press,1998:1309-1314.

[4]EIJI O,NATTAPONG K,SHUNICHI T,et al.Scalable network emulator architecture to support IP+optical network management[C]//Proc.2010 IEEE Network Operations and Management Symposium.Tokyo,Japan:IEEE Press,2010:902-905.

[5]MAHADEVAN S,ANGIOLINI F,SPARS SPARSO J,et al.A reactive and cycle-true IP emulator for MPSoC exploration[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and System,2008,27(1):109-122.

[6]BANKS S,BEADING P,FERENCZ A.FPGA implementation of pseudo random number generators for monte carlo methods in quantitative finance[C]//Proc.the 2008 International Conference on Reconfigurable Computing and FPGAs.Singapore:IEEE Press,2008:271-276.

[7]SHU Haiyan,HUANG Haibin,LI Te,et al.Bit-plane coding for source with generalized Gaussian distribution[C]//Proc.the 11th IEEE International Symposium on Multimedia.[S.l.]:IEEE Press,2009:17-23.

[8]ARSHAK K,JAFER E,IBALA C.Power testing of an FPGA based system using modelsim code coverage capability[C]//Proc.the 2007 IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems.[S.l.]:IEEE Press,2007:157-160.

Design of FPGA-based IP Carrying Network Emulator

LI Xing,ZHANG Zhizhong

(Key Lab.on Communication Networks and Testing Technology,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

In view of the IP carrying network structure and technical characteristics,firstly,a system framework of the FPGA-based IP carrying network emulator is proposed which combines with the current situation and requirements of network performance testing.Then,a way to emulate the packet loss rate based on the FPGA is researched.Finally,the design idea of the emulator hardware module is discussed in detail.The result of the simulation test shows that the system has a good application foreground.

IP carrying network;FPGA;network emulator;Gaussian distribution;Modelsim simulation

TN919.5

A

【本文献信息】李星,张治中.基于FPGA的IP承载网损伤仪设计[J].电视技术,2013,37(3).

国家科技重大专项(2012ZX03005002- 005;2012ZX03005-008);重庆市科委攻关项目(CSTC 2010AC2147);重庆市教委自然科学基金项目(KJzh10204)

李 星(1988— ),硕士生,主要研究方向为嵌入式软件和驱动开发;

张治中(1972— ),教授,主要研究方向为第三、四代移动通信测试技术和NGN网络测试技术等。

责任编辑:任健男

2012-09-20