图像数据远距离传输及高速实时存储技术

安航行,孟令军,赵 林,李鹏飞

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,山西太原 030051)

图像数据远距离传输及高速实时存储技术

安航行,孟令军,赵 林,李鹏飞

(中北大学仪器科学与动态测试教育部重点实验室,电子测试技术国家重点实验室,山西太原 030051)

研究了一种可以实现图像数据的远距离传输和高速实时存储的技术。该技术以FPGA为逻辑控制单元,通过LVDS接口电路远距离传输采集到的图像数据;利用交叉双平面页编程技术流水线式写Flash以提高存储速度。用CY7C68013A控制的USB2.0接口上传Flash中的数据到计算机,最后用上位机软件分析数据。结果表明,该系统稳定可靠地远距离传输并高速存储了图像数据。

LVDS;流水线;交叉双平面页编程

在航天航空、工业自动化、通信等领域,在某些特殊的条件下,有时需要实现图像数据的远距离传输和高速实时存储,并且能够实现数据的回放,以及后续的数据分析和处理。本文提出的方案,应用电缆延展器芯片组使上百米的LVDS远距离传输稳定可靠;Flash存储芯片中无效块地址的统筹管理,交叉双平面页编程以及分级缓存使图像数据的储存速度几乎可高达480 Mbit/s。与传统的图像数据存储系统相比,该系统具有数据传输距离远、存储速度高的特点。

1 工作原理与系统组成

1.1 工作原理

尽管LVDS传输技术具有传输速率高、低噪声、低功耗等优点,但远距离传输也会使信号衰减,距离越远、传输速率越高,衰减也就越大[1]。因此,通常设计的LVDS远距离传输不够十分理想。LVDS串化/解串器接口也是有一定的距离限制的,一般情况下最远不超过几米,但是如果在发送端使用LVDS电缆驱动器DS15BA101进行驱动,在另一端使用电缆均衡器芯片DS15EA101对长线传输后的图像信号均衡处理,便可以很好地弥补LVDS远距离传输方面的不足,最终成功传送长距离的图像信号。

对Flash芯片中的无效块地址的统筹管理、交叉双平面页编程以及流水线式的操作等方法的应用,提高了时间利用率,极大地提高了图像数据的存储速度,实现了高速图像数据的实时存储。

1.2 系统组成

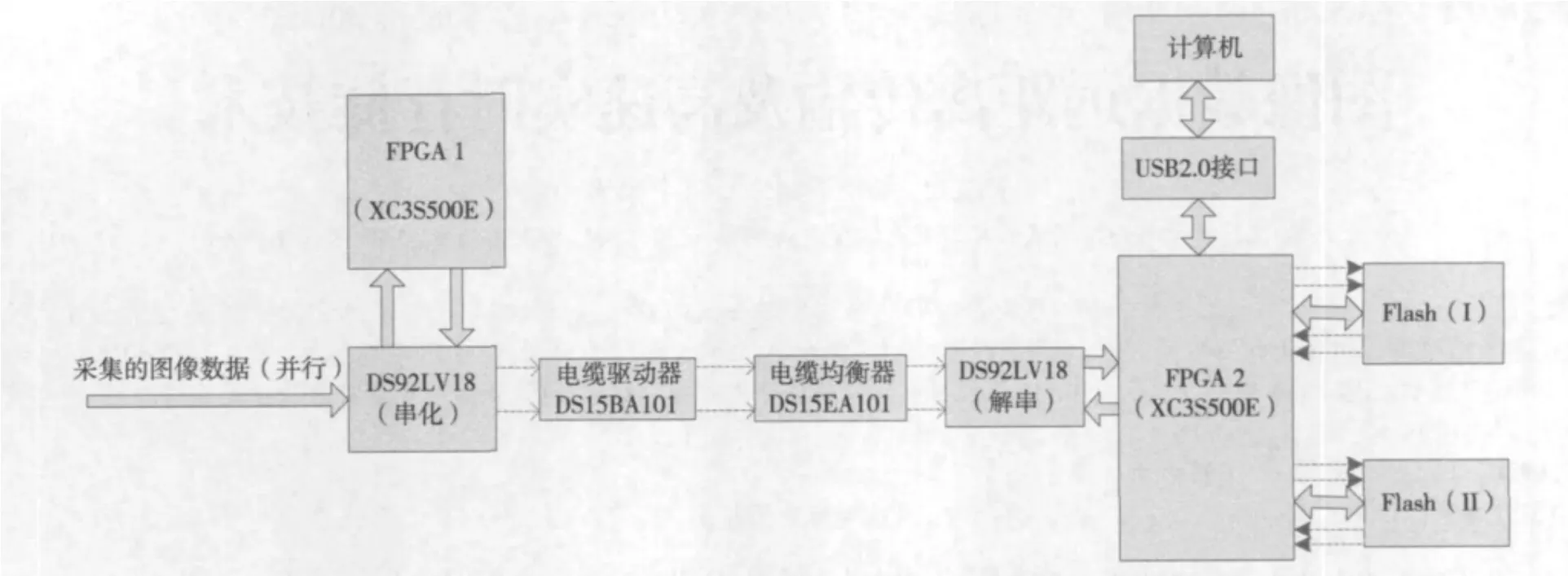

系统主要由Spartan-3E系列的FPGA芯片XC3S500E、电缆驱动器芯片DS15BA101、电缆均衡器芯片DS15EA101、4 Gbyte的Flash存储芯片K9WBG08U1M、18 bit总线的双向LVDS解串/串化器DS92LV18、CY7C68013A等芯片和相应的外围接口电路构成。系统工作时钟频率为66 MHz。系统组成框图如图1所示。

2 关键技术分析

本系统选用National Semiconductor公司的DS92LV18作为LVDS传输的串化器和解串器。DS92LV18是18 bit总线的双向的LVDS解串/串化器,工作时钟频率范围为

2.1 LVDS 远距离传输

图1 系统组成框图

15~66 MHz。DS92LV18串化/解串器芯片组,能把一个18 bit的并行数据转换为一个带内嵌时钟的LVDS串行数据流。用时钟同步的方法,这个串行数据流很容易地转换为18 bit并行数据或低于18 bit的并行数据[2]。如图1所示,前一个DS92LV18把采集到的8 bit并行的图像数据转换为串行数据,后一个DS92LV18则用来解串,两者配合实现LVDS传输。

为了实现远距离的LVDS传输,本系统选用电缆驱动器芯片DS15BA101以及电缆均衡器芯片DS15EA101,它们都是美国国家半导体公司的产品。DS15BA101和DS15EA101电缆延展器芯片组,可以通过双绞线或同轴电缆来驱动来自串化/解串器DS92LV18和FPGA芯片的串行数据流。DS15BA101是一种性能十分良好的缓冲器,能缓冲高速的差分信号,可以用于电缆驱动、信号缓冲和电压转换[3]。与其配对使用的芯片是DS15EA101,它是一种具有自适应能力的均衡器,能够在很宽的速度范围内工作,从150 Mbit/s~1.5 Gbit/s。这样,串化后的数据流经电缆驱动芯片DS15 BA101驱动,远距离高速传输后由电缆均衡器DS15EA101恢复调理,再经过解串器解串,便能成功实现图像数据的LVDS远距离高速传输。

2.2 Flash芯片中无效块的管理

在对Flash存储芯片进行操作时只能对有效存储块进行操作,因为对无效块进行操作会造成数据的丢失、数据存储错误等严重的后果。因此,无效块的检测是不可回避的。如果能合理地管理这些无效块的地址,则能大大提高Flash读、写、擦除的速度。

1)把无效块检测放在系统上电之后,块擦除、页编程、读数这些操作之前。

传统的步骤是“坏块检测—操作,再检测—再操作”的模式。在对Flash芯片中的每一块进行擦除、编程、读数之前都不得不进行坏块检测,这极大地影响了操作的速度。当系统一上电立刻对存储芯片中全部的存储块(block)进行检测,并且将检测到的坏块地址写进FPGA内部建立的一个ROM中,在对Flash进行块擦除、读数、页编程等操作时,只需要把当前块的块地址与ROM中存放的无效块地址进行比较,只要检测到该地址存在于ROM中,那么这个存储块(block)就一定是无效块,否则它就一定是有效块。若系统工作频率为66 MHz,传统的方法检测一个块是否为无效块大概要用2 400个时钟周期。若采用本文提出的方法,在每次操作前只需读出ROM中存放的无效块地址值与当前块的块地址进行比较即可,一次判断仅需要4个时钟周期。

2)统筹管理无效块地址。

在检测无效块时,只要检测到CE1中的block(2n),block(2n+1),block(2n+4 096),block(2n+4 097)和CE2 中的block(2n),block(2n+1),block(2n+4 096),block(2n+4 097)这8个存储块(block)中有一块为无效块,就把这8个存储块都当作是无效块来处理。这种无效块地址的统筹管理,虽然浪费了芯片中一小部分有效块资源,但这极大地方便了流水线式的交叉双平面页编程操作(便于流水线式操作过程中块地址的切换),降低了控制逻辑的复杂度,对存储速度的提高十分重要。

2.3 交叉双平面页编程(芯片内部独立单元流水线式操作)

本系统采用NAND型Flash K9WBG08U1M作为存储芯片,它是三星公司的产品,1片芯片存储容量就高达4 Gbyte。实际上是由2片K9WAG08U1M集成的,单片K9WAG08U1M的存储容量为2 Gbyte,通过管脚CE1和CE2来控制选通。1片K9WAG08U1M由8 192个存储块(block)组成,这8 192个存储块(block)平均划分为4个平面(Plane),Plane 0,Plane 1,Plane 2 和 Plane 3,其中Plane 0和Plane 1是独立的存储单元,Plane 2和Plane 3是独立的存储单元。这样,1片K9WBG08U1M内部有4个独立的存储单元,对每个独立的单元能进行独立的操作而互不影响。

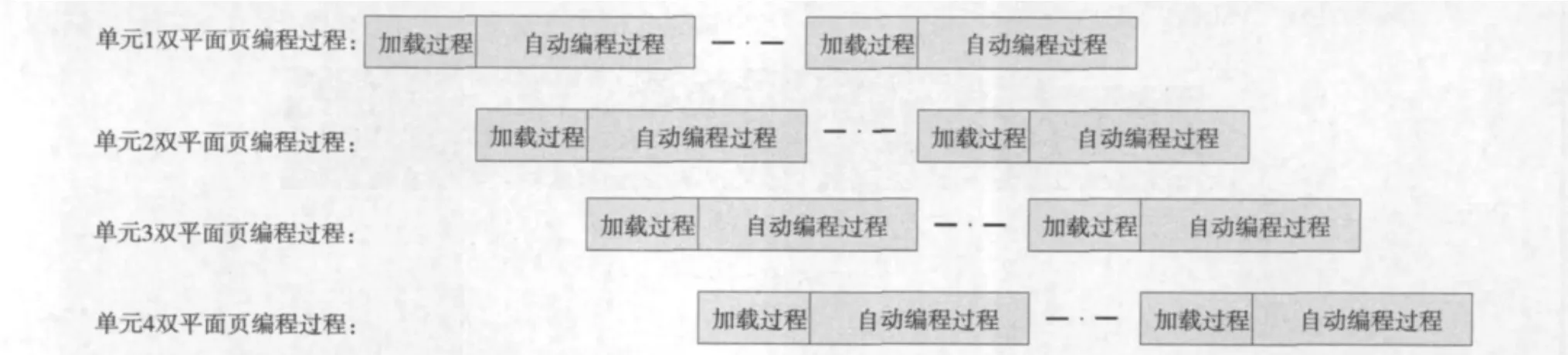

K9WBG08U1M芯片的数据存储是一页一页(page)地进行编程存储的,其页编程(page program)过程可分为命令、地址、数据的加载过程和自动编程过程。加载过程就是通过芯片外部的时序控制把命令字、地址和数据写入芯片内部的寄存器的过程;自动编程过程就是芯片按照地址把寄存器中的数据自动地转移到存储阵列中的过程,这需要一段相当长的编程时间(tprog),一般为200 μs左右,不会超过700 μs,在这段相对较长的时间里芯片的该单元是不再响应其他任何操作的。双平面页编程的特点是把2组命令字、地址和数据连续加载到同1个平面(plane)的2个页寄存器中,这样完成2个页(page)的编程的时间几乎减少了1个自动编程时间(tprog),从而提高了单个页(page)的平均存储速度。实验证明,页编程的时间正是限制Flash存储速度的关键因素,因此在对其进行页编程操作时采用流水线技术来实现高速大容量Flash的存储。由于每个独立单元都由2个平面(plane)组成且每个独立单元的页编程过程中它是不响应任何操作的,可以对4个独立单元都采用双平面页编程(Two-plane Page Program)方式,对1片K9WBG08U1M内部的4个独立单元进行流水线式的操作,实现时间上的复用,因此提高了整个芯片的平均页编程速度。其操作流程为,当第1个单元在进行双平面页编程操作的时候,依次往第2个单元、第3个单元、第4个单元加载命令、地址和数据。经过计算可知,当对第4个单元加载完成后,第1个单元已经完成自动编程,可以立刻对第1个单元再次加载命令、地址和数据。如此循环下去,提高了时间利用率,省去了等待页编程的时间,从而提高了整片的写入速度。操作过程如图2所示。

图2 K9WBG08U1M内部4个单元流水线操作过程

时钟晶振为66 MHz时,单个K9WBG08U1M采用交叉双平面页编程方式、流水线操作,平均写入速度超过240 Mbit/s。

2.4 分级缓存平分数据流

FPGA内部有很多的RAM块,如果能够合理地使用,就能简化外部电路的复杂度,降低成本。使用它们建立1个8 kbyte的FIFO作为第一级缓存,建立2个4 kbyte的FIFO,FIFO(I)和FIFO(II)作为第二级缓存。二级缓存结构如图3所示。

图3 二级缓存结构示意图

LVDS高速数据流经过DS92LV18解串后先写入这个第一级缓存,当第一级缓存FIFO半满后,将第一级缓存中的数据快速读出4 kbyte再写入第二级缓存FIFO(I)中,而FPGA内部控制Flash的模块判断到第二级缓存FIFO(I)中的数据量非空后,则以240 Mbit/s的速度连续读取4 kbyte个数据写入Flash(I)中;之后再次判断第一级缓存中的数据是否半满,如半满,则将第一级缓存中的数据高速读出4 kbyte再写入第二级缓存FIFO(II)中,以同样的方式将数据从第二级缓存FIFO(II)中读出再写入Flash(II)中,这样反复交替,直到数据记录完毕。这样,整个系统的平均数据写入速度几乎高达480 Mbit/s,能够完成图像数据高速实时存储的任务。

3 USB 2.0通信接口和上位机软件

为了实现数据的高速上传,尽可能达到USB2.0的最大带宽,本系统选用控制器CY7C68013A。它是Cypress半导体公司的产品,属于EZ-USB FX2LP系列。系统选择它的同步SLAVE FIFO传输模式,整体框图如图4所示。IFCLK使用48 MHz内部时钟。FLAGA,FLAGB,FLAGC,FALSD是内部端点标志位,它们用来供外围电路使用,SLOE是输出使能信号,SLRD和SLWR分别是读、写信号。PKTNED为包提交信号,FD[15:0]为数据总线,选用8位。FIFOADR[1:0]为内部端点指针,分别指向端点2、端点4、端点6和端点8,通过 IFCONFIG寄存器设置。

图4 USB2.0 SLAVE FIFO传输模式框图

上位机软件通过USB2.0通信接口实现命令的下传和存储数据的快速上传,并最终完成对图像数据的定性、定量分析与特定处理。

4 系统测试结果

经过实际测试,该系统能够可靠地实现图像数据的远距离传输,并且它也能够实现高速实时存储。图像信号源以480 Mbit/s的速度发送图像信号,每帧有289行有效数据,每行有384个有效像素,经过118 m电缆传输,通过特定图像信号源实际测试后,通过上位机软件回读的数据如图5所示。由图5回读的数据验证了该方案是正确可行的。

5 小结

本系统采用电缆延展器芯片组,能可靠地进行上百米的LVDS远距离传输;采用分级缓存、流水线式操作、对Flash存储芯片无效块的合理管理以及交叉双平面页编程,这大大提高了存储的速度。通过实际测试后表明该系统同时具有两大功能——图像数据远距离传输和图像数据高速实时存储。

图5 上位机回读的图像数据(截图)

:

[1]储成群.基于LVDS接口的高速数据记录器的设计[D].太原:中北大学,2011.

[2]严帅,孟令军,胡肖斌,等.红外相机数据高速实时存储技术[J].电视技术,2011,35(13):25-27.

[3]周立功.USB 2.0与OTG规范及开发指南[M].北京:北京航天航空大学出版社,2004.

Long-distance Transmission and High-speed and Real-time Storage Technology of Image Data

AN Hangxing,MENG Lingjun,ZHAO Lin,LI Pengfei

(Ministry of Education Key Laboratory of Instrumentation Science&Dynamic Measurement,National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

A kind of technology which is about long-distance transmission and high-speed storage of image data is researched.FPGA is the logical control unit of this technology.The technology can acquire image data over a long distance by LVDS interface circuit.The pipeline technology and the interleave two-plane page program technology are used to write Flash which can improve the storage speed.USB 2.0 interface which is controlled by CY7C68013A is used to upload the image data to computer and the data is analyzed by software.Results show that the system can transmit the image data over a long distance and store image data with a high speed steadily and reliably.

LVDS;pipelining;interleave two-plane page program

TN911.73

A

【本文献信息】安航行,孟令军,赵林,等.图像数据远距离传输及高速实时存储技术[J].电视技术,2013,37(3).

国家自然科学基金项目(51075375)

安航行(1980— ),硕士,主要研究方向为测试计量技术及仪器;

孟令军(1969— ),博士,副教授,主要研究方向为无线传感器网络节点定位技术;

赵 林(1987— ),硕士生,主要研究方向为电路与系统;

李鹏飞(1985— ),硕士生,主要研究方向为微纳技术及仪器。

责任编辑:任健男

2012-11-15