基于PCI总线的高速串口通信卡的设计

叶 勇,沈三民,郭 铮,崔 婧,苏虎平,张雪莲

(中北大学a.仪器科学与动态测试教育部重点实验室;b.中北大学电子测试技术重点实验室,山西太原 030051)

基于PCI总线的高速串口通信卡的设计

叶 勇,沈三民,郭 铮,崔 婧,苏虎平,张雪莲

(中北大学a.仪器科学与动态测试教育部重点实验室;b.中北大学电子测试技术重点实验室,山西太原 030051)

介绍了一种基于PCI总线的高速串口通信卡的设计,采用PLX公司的PCI9054作为PCI总线桥接芯片,FPGA作为本地总线的控制器和系统主控单元,选用LVPECL电平单模双纤光收发一体模块OCM3723为串口传输介质。最后介绍了利用visual C+++DDK进行设备驱动开发。该设计的高速串口通信卡,其通信速率可达80 Mbit/s,传输距离超过10 km。具有设计简单、速率快、可靠性高、传输距离远等特点,已经成功运用于某航天遥测系统。

PCI总线;高速串口通信;PCI9054

PCI总线标准是一种将系统外部设备连接起来的总线标准,它是PC机中最重要的总线。其他设备例如:USB总线、ISA总线等总线都挂接在PCI总线之上。如果时钟采用33 MHz,它的传输速率可达132 Mbyte/s(PCI总线为32位),对于64位PCI总线,其吞吐率能达到264 Mbyte/s峰值[1];64位66 MHz PCI总线,数据吞吐率理论值为528 Mbyte/s。一般在PC机中,显卡、网卡都被设计成PCI总线设备,插于PCI插槽,有利于方便更换已坏设备。

本文设计的基于PCI总线的高速串口通信卡,采用PLX公司的PCI9054作为PCI总线与本地总线的桥接芯片,控制方便,实现简单。从硬件电路的设计,到软件的编写,再到驱动程序的撰写,本文将一一予以探讨。

1 系统硬件逻辑设计

基于PCI总线的高速串口通信卡的设计总体结构如图1所示,整个通信卡可分为三部分:信号采集单元、中心控制逻辑单元和PCI桥接电路。此卡插于PCI扩展槽中,与PC机进行通信。

图1 系统总体结构图

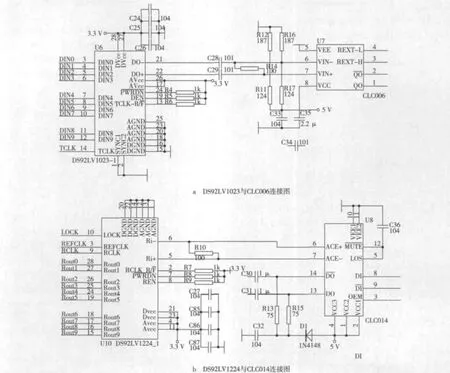

信号收发单元包括光模块与LVDS高速接口电路。LVDS高速接口可以确保数据传输的快速性,光模块解决遥测系统的传输距离。本设计采用1对10位总线型低压差分信号应用芯片组DS92LV1023(串行器)与DS92LV1224(解码器)。其中DS92LV1023可以将10位并行CMOS或TTL数据转换为具有内嵌时钟的高速串行差分数据输出;DS92LV1224则将输入的差分数据转换成并行10位数据输出,同时内部锁相环可从串行数据中重建并行时钟。因LVDS芯片组的差分电压摆幅为0.7 V,不能直接与1.5~2.3 V电压差输入的光模块OCM3723直接相连,所以配合使用电缆驱动器CLC006与电缆均衡器CLC014。可将电压摆幅提高到2 V,这样能使信号良好地搭载在光模块,使传输距离得到极大改善[2]。

PCI接口电路使用PLX公司的PCI9054,也是目前主流的PCI总线接口芯片之一,其逻辑控制简单,无需复杂的固件编写,且PLX公司提供官方的驱动程序作为参考,可以大大缩短开发周期。此卡通过PCI总线与上位机通信,可以实时进行监测和高速的数据存取。

中心控制逻辑单元采用一片Xilinx公司的XC3S400作为逻辑控制器,其主要作用是作为本地总线的逻辑控制单元与PCI总线通信、数据缓存及信号采集模块的控制器,也是高速串口通信卡的主控芯片。FIFO存储器作为数据缓存器,本设计采用XC3S400的内置块RAM配置而成。系统采用40 MHz晶振,经FPGA内部的时钟管理模块倍频得到80 MHz时钟,使得传输数率可达80 Mbit/s。

1.1 信号收发单元

进行串口通信时,数据流在信号线上传输必然产生信号的畸变,波特率与传输距离成为一对矛盾体。为此,本文提出LVDS+光模块的设计,在一定程度上解决了传输速率与传输距离的瓶颈现象,可将高速通信距离提高到10 km以上。

LVDS是一种小振幅差分信号技术,使用低压(约350 mV)差分信号传输数据。允许单个信道传输速率达到数百兆比特每秒,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。其LVDS应用芯片组与电缆驱动器、电缆均衡器的连线图如图2所示。这里R5与R10为匹配电阻,大小为100 Ω。

而光模块的使用,利用其良好的光电转换作用,可以使传输距离提高到10 km以上。本设计选用LVPECL电平单模双纤光收发一体模块OCM3723,其特点为:1)SC/FC插拔式光接口;2)单+3.3 V/+5 V供电;3)接口电平兼容标准LVPECL电平;4)标准1×9管脚封装,引脚配置与Multi-source协议兼容;5)发射器件可选用工作波长为1 310 nm的FP激光器或1 550 nm DFB激光器;6)接收采用平面结构InGaAsP PIN探测器。

图2 LVDS应用芯片组与电缆驱动器、电缆均衡器连线图

1.2 PCI接口电路

PCI9054的操作方式有M,C,J这3种模式,本设计采用时序控制相对简单的C模式。

PCI9054的工作方式有3种:主模式、从模式及DMA模式。本设计采用从模式的多周期传输方式。其中,主模式是由本地处理器作为主设备,发起PCI存储器或I/O对访问,PCI9054作为本地总线的目标设备;从模式是由PCI主设备发起整个数据传输,PCI总线可以对配置寄存器及本地总线内存进行访问,PCI9054作为PCI总线的目标设备;DMA模式是一种快速的数据传输机制[1],由PCI9054的DMA控制器控制在不需要CPU的干预下,对本地总线的存储器或I/O与PCI总线的存储器或I/O之间的数据交换。考虑数据流不是非常大,使用从模式下的突发传输发式即可。

PCI9054的配置信息通过上电后从E2PROM中读取。这里选用Microchip Technology公司的93LC56。93LC56的接线图如图3所示。为了便于调试用,在EEDI/DO引脚上设计有上下拉电阻,需要配合PCI9054调试时,焊接下拉电阻,正常工作时接上拉电阻。

图3 93LC56的接线图

1.3 中心控制逻辑单元

中心控制逻辑单元控制着信号收发时序、搭建内部FIFO以及作为本地总线逻辑单元与PCI总线通信。这里选用XI-LINX公司的XC3S400,其具有4×105门的门电路,896个CLB和360 kbit的块RAM。符合其设计要求。

1)内部FIFO的搭建

通过FIFO进行数据缓冲来解决数据匹配问题。因选用资源丰富的XC3S400,内部块RAM可达360 kbit,可以在内部搭建FIFO以减少设计成本。

如图4所示,采用8块双端口的块RAM RAMB_16_S4_S4搭建为4 k×32位FIFO。块RAM的A端口作为写端口,B端口作为写端口。它们的使能端都与VCC相连,不同的是,写使能一个接VCC,一个接地。需要注意的是,对块RAM读写操作时,不能同时进行,否则输出将是不定值,造成输出失败。

图4 块RAM搭建FIFO结构图

2)本地总线逻辑单元

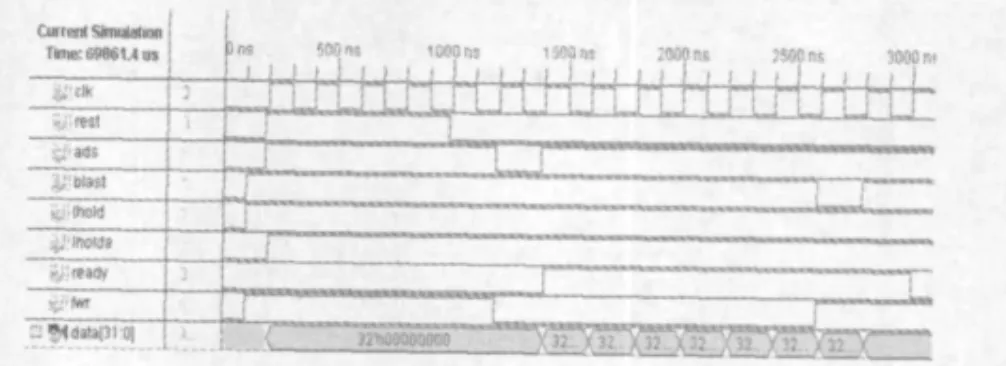

在FPGA中实现PCI9054的读写,即对本地总线总裁。包括本地总线请求信号LHOLD和本地总线应答信号LHOLDA的处理。在很多的设计中,都是将PCI9054的LHOLD和LHOLDA两个引脚直接相连接,或在FPGA/CPLD内部用连续赋值直接将LHOLD的值赋予LHOLDA,利用器件的引脚传输延迟配合总线仲裁电路来进行时序控制。因为当尖峰脉冲耦合进FPGA内部时会造成逻辑电路的误触发[4],所以采用这些方式将会导致计算机出现读数错误、死机等现象。PCI本地总线通信仿真图如图5所示,PCI9054进行量7个长字的突发传输模式。

图5PCI本地总线通信仿真图(截图)

2 设备驱动开发

PCI板卡插入PCI扩展槽,如果要正常工作,需要在Windows下撰写驱动程序。驱动程序主要有以下几个步骤:打开设备;设备初始化[5];设备读写;关闭设备。Windows系统下的驱动用的最多是DDK,driverstudio,windriver这机种工具。其中,DDK的效率最高,但编写起来难度太大,多数技术人员使用driverstudio,windriver这两种工具编写出来的程序也称为WDM(Windows Device Module)程序。本课题采用DriverStudio工具。

DriverStudio中的DriverWorks软件为WDM驱动程序提供了完整的框架,本设计利用其DriverWizard生成驱动程序框架,然后添加各功能函数。这里利用类KMemoryR-ange实现对BU-61585内部存储器的读写访问,类KIoR-ange实现对其寄存器的访问。下面是驱动程序中类实例KMemoryRange0的初始化及其对BU-61585内部存储器的写操作功能函数。

3 结束语

PCI总线满足现代设备传输数率越来越高的要求,PCI9054为PCI总线接口技术提供了较为简单的开发过程,其高速的传输数率将会被广泛应用。本文设计的高速串口通信板,已成功应用于图像数据的传输。当数据总线扩展到64位,数据传输模式采用DMA方式,对于数率的提高仍有较大的裕度。

:

[1]赵锡凯.PCI总线扩展技术研究[J].计算机工程与科学,1997(2):12-15.

[2]袁伟涛,张斌珍,刘文怡.箭载遥测变换器测试台的设计与实现[J].测控技术与仪器仪表,2008(2):87-90.

[3]荣思远,景新幸,陈用昌.基于PCI总线的视频采集卡研究[J].电视技术,2006,30(11):32-35.

[4]蔡祁鹏,王宏远.HDTV信号源中PCIDMA的WDM程序开发[J].电视技术,2001,25(4):17-20.

[5]何瑾,张烨君,于彤彦.基于PCI总线的数据采集卡的设计[J].现代电子技术,2006(17):109-110.

Design of High-speed Serial Communication Based on PCI Bus

YE Yong,SHEN Sanmin,GUO Zheng,CUI Jing,SU Huping,ZHANG Xuelian

(a.Key Laboratory of Instrumentation Science&Dynamic Measurement,Ministry of Education;b.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

A kind of high-speed data transmission system based on PCI bus is presented,which exploits a PCI bridge chip PCI9054 which produced by PLX company,FPGA as local bus controller and system control unit,data transmission with the external system through duplex fiber single mode PECL transceiver OCM3723.At last,the use of visual C++&DDK for equipment driver development is introduced.Design of high-speed data transmission system,its communication rate of up to 80 Mbit/s,the transmission distance more than 10 km.It is simple in design,speed,high reliability,long distance transmission and other characteristics,is been successfully used in a space telemetry system.

PCI Bus;high-speed serial communication;PCI9054

TP274

A

【本文献信息】叶勇,沈三民,郭铮,等.基于PCI总线的高速串口通信卡的设计[J].电视技术,2013,37(3).

国家自然科学基金重点项目(60871041)

叶 勇(1988— ),硕士生,主研电路系统和微系统集成。

责任编辑:时 雯

2012-06-07