基于帧头信息的载波同步设计及FPGA实现

韦照川,谢 栋,蔡成林

(桂林电子科技大学信息与通信学院,广西桂林 541004)

基于帧头信息的载波同步设计及FPGA实现

韦照川,谢 栋,蔡成林

(桂林电子科技大学信息与通信学院,广西桂林 541004)

论述了一种基于帧头信息的载波同步设计及FPGA实现方法。首先介绍了频偏相偏估计原理,然后分别介绍了FPGA设计的系统框图和子模块的原理,最后进行了Modelsim仿真和SignalTap的板级测试验证。

帧头信息;频偏估计;相偏估计;载波同步;FPGA

现代数字通信中,像QPSK,QAM这样的正交调制应用广泛。正交调制是把数据信息映射到I、Q两路,同时要插入帧头作为帧同步信号。普通的帧头信号和某些特定格式的帧头信号,不仅可以作为帧同步判断,还可以用来做频偏和相偏估计。这种方法已经在OFDM上得到了广泛应用,其中频偏是基于自相关函数的估计算法[1~3],相偏是基于数据幅度衰减的估计算法。

1 频偏相偏估计原理

1.1 频偏估计原理

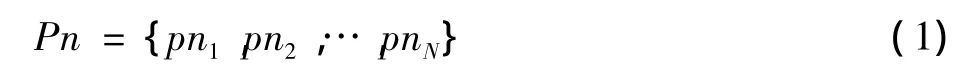

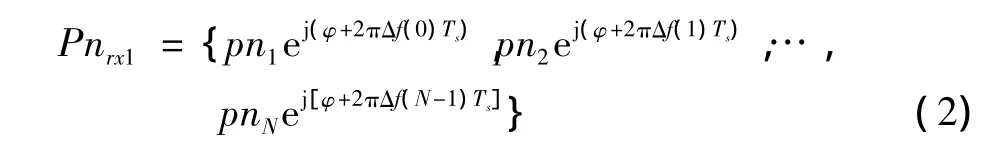

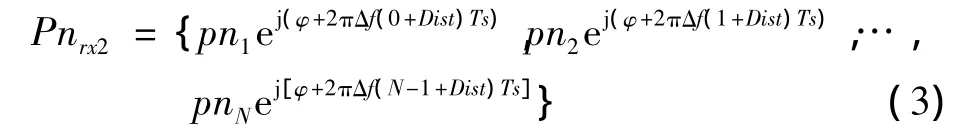

假设由I,Q两路发送的帧头序列为

由于在传输过程中存在初始相位和固定的频偏,所以接收端接收到的信号为

在间隔为Dist所接收到的信号为

式中:φ是载波相位差,Δf为载波的频偏,Ts为基带码元速率。这里Dist的大小决定了频偏估计的范围和精确度,和帧头格式有直接关系[4]。如果帧头信号采用了通常的非重复随机序列,那么可以用相邻两帧的帧头来计算频偏,这时候Dist的数值就等于一帧数据的长度。如果帧头信号采用连续两个相同的随机序列,那么Dist就等于一个随机序列的长度,本文中的频偏和相偏估计设计就是基于后面这种假设。

由式(2)、式(3)可得

式中:*表示取共轭。因此,

式中:arg[·]表示取复数的辐角。

1.2 相偏估计原理

相偏估计是在频偏估计并且纠正的基础上,根据I,Q两路的幅度衰减计算出来的。

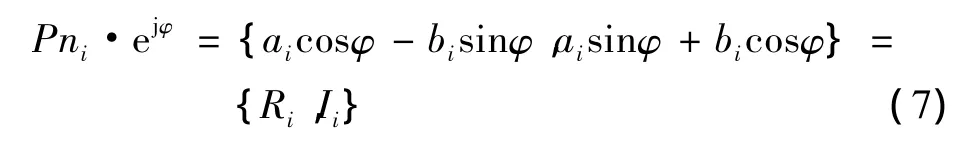

由式(2)可知,当频偏Δf的值为0时候,接收到的序列如式(6)

假设式(6)中的复数序列pni=ai+jbi,ejφ=cosφ+jsinφ,那么可以得到

式中:i=1∶N,大括号里面分别表示接收端序列的实部和虚部,也就是I,Q两路的数据。因为已知发送端帧头序列pni中为设置ai=bi=1,那么由式(7)可以得到相差角度为

2 FPGA硬件模块设计

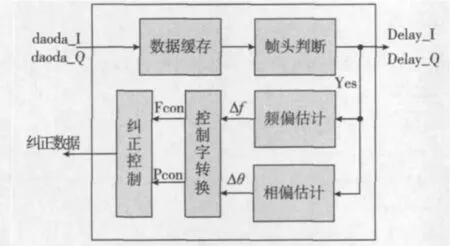

系统采用QPSK调制方式,基带数据率设置为50 bit/s。帧头采用连续2个相同的7位数据,总长度为14,每帧数据长度共300个。频偏和相偏联合的FPGA实现框图如图1所示。

图1 FPGA硬件框图

图1的载波同步模块分为数据缓存、帧头判断、频偏估计、相偏估计、控制字转换、纠正控制6个部分。数据在模块内部的处理流程是:当到达检测模块输出的有效数据到达时,即daoda_I与daoda_Q,首先被送入数据缓存模块,数据缓存模块的作用是先将数据缓存起来,接着把缓存的数据送入帧头确认模块进行确认,若帧头确认正确,则产生一个使能信号激活频偏估计模块,同时输出延迟后数据;若帧头确认错误,则不进行频偏计算,直接输出。通过频偏估计模块进行计算的数据,接着被送入控制字转换模块转换成控制NCO的频率控制字。帧头确认模块输出的数据Delay_I与Delay_Q是将延迟的数据输出提供给相位估计纠正模块。

2.1 数据缓存模块

数据缓存模块为整个载波同步模块的第一个子模块,主要完成输入数据的缓存,并送入后续单元。假设数据帧头长度是14,缓存的数据长度取15个,即帧头的长度加1,若保存的太多则会消耗FPGA比较多的资源。它的一个作用是便于帧头确认模块直接判断帧头,另一个作用则是为了减少乘法器的消耗,因为频偏计算模块计算频偏的时候并不是一个时钟周期计算完成,而是通过移位相乘累加,通过多个时钟来计算,采用流水线的思想,这样节省了乘法器的消耗。移位寄存器的结构图如图2所示。

2.2 帧头判断模块

图2 移位寄存器的结构图

帧头判断模块主要负责判断到达检测输出的帧头是否正确,若检测到帧头到达,则产生帧使能信号,来激活频偏计算模块和相偏计算模块,并且频偏和相偏的纠正有一定的顺序,如果在没有纠正频偏的基础上纠正相偏,那频率的偏差会叠加到相位的偏差上,所以帧头确认模块还产生一个纠正控制信号,来决定频偏和相偏的纠正顺序和次数。若没有检测到则不产生使能信号,即不进行计算,以防止利用错误的帧头计算出错误的频偏反馈回系统从而影响系统的正常工作。若找到帧头,则拉高帧标志位Flag,并且驱动频偏估计模块开始工作。

2.3 频偏估计模块

频偏估计模块主要负责利用数据缓存模块输出的帧头数据,运用公式进行相关计算求出载波频率的偏差。

由于接收到的是复数序列A={α1,α2,…,αN},B={β1,β2,…,βN},则A和B的互相关定义为

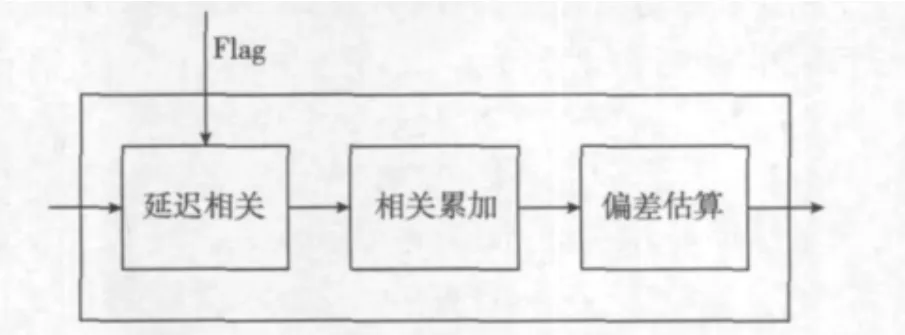

依据式(9)对频率偏差进行估算。硬件实现上包括延迟相关、相关累加和偏差估算3个部分,如图3所示。

图3 频偏估计模块

2.3.1 延迟相关模块

当用于频率偏差估算的帧头到达,并且帧头使能信号拉高时,为了便于计算前后2个对应取样的相关值,在数据缓存中使用移位寄存器。帧头信号判断到达后,帧头的第1位与第8位已经移到了移位寄存器的第8级与第15级,所以只需计算第8级与第15级相乘便可得到计算相关值的4个部分。

2.3.2 相关累加模块

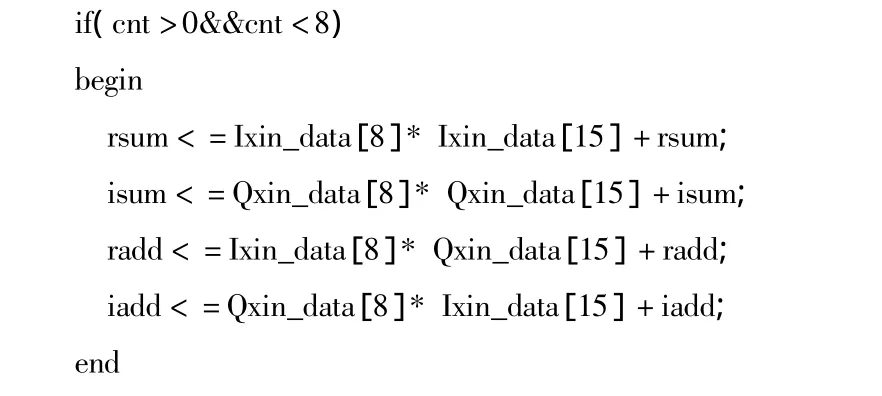

由于计算相关值运算的时候是复数运算,所以式(9)相关值的4个部分需要累加起来,累加的个数是2个重复序列的个数。下面代码实现了式(9)的相关累加

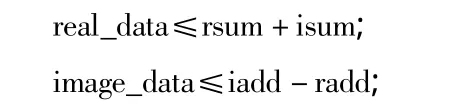

2.3.3 偏差估算模块

偏差估算主要负责在得到相关累加值后,从中提取相位信息,如图4所示。

图4 偏差估算模块

其中:

由以上可以看出,频率偏差的估算的关键是从相关累加值中提取相位信息,即Tan-1的运算。采用近似算法实现此功能。Tan-1的运算采用下面的近似公式[5]

采用这种方法的主要原因是避免了查找表的精度不高的问题。

2.4 相偏估计模块

相偏估计的主要作用是完成频差纠正后对相差的估计。相偏估计包括相关计算、求反正切、累加平均三个部分,如图5所示。

图5 相偏估计模块

2.4.1 相关计算模块

由于对相位偏差的计算只需要1组数据便可计算出相位,所以这里不需要缓存,只需要直接计算数据的相关值。相关计算的输入为帧头确认模块的输出Delay_I和Delay_Q,如下面代码所示:

2.4.2 Tan-1模块

2.4.3 累加平均模块

为了弥补之前角度的一些偏差,所以后面进行累加求平均来弥补。这里选用累加的个数为8,这样在求平均的时候只需要左移3位,便可以实现除以8的功能,而不需要调用除法器的IP核。

2.5 控制字转换模块

控制字转换模块的主要功能是将频偏估计和相偏估计模块算出来的频偏和相偏转换成控制NCO的频率控制字和相位控制字。

频率控制字换算公式为

相位控制字的位数为12位,因此对应将360°分成212=4 096份,得到相位控制字的换算公式为

其中,fclk是系统工作时钟,Fcon位频率控制字,N为相位累加器的比特数。算出了Δf后,将Δf代入公式得到

2.6 纠正控制模块

纠正控制模块主要完成对频率控制字和相位控制字的纠正,从控制字转换模块出来的频率控制字和相位控制字并不能直接使用,要叠加到初始的频率控制字和相位控制字上,并且频率和相位的纠正有一定的顺序,必须先纠正频率再纠正相位,因为频率的偏移会以相位的形式表现出来。纠正控制模块就是完成频偏和相偏的纠正及纠正的顺序和次数的控制。

纠正的顺序和次数采用计数的方法,计数器采用2个,一个是帧内数据的计数,另一个是纠正的次数。当帧确认模块被确认后,会输出一个纠正信号,并且这个信号的输出是在频偏和相偏算完的情况下,在第一帧的情况下,帧内数据计数器记到一个值时,便产生一个纠正信号,使纠正计数器加1时,开始进行频偏的纠正,当频偏纠正后,下一帧便进行相偏的纠正,这样实现频偏、相偏交替纠正。

3 仿真测试

3.1 Modelsim仿真

预先设置某个频偏,用Modelsim仿真得到图6。从图中可以看出,频偏引起的数据幅度调制基本得到了纠正。

图6 频偏纠正前后对比波形(截图)

频偏纠正的基础上,相偏导致的是数据等幅度的衰减,图7给出了详细的相偏仿真过程数据图,从图中数据可以看出计算过程与预期一致,相偏也基本得到了纠正。

图7 相偏纠正的时序仿真图(截图)

3.2 Signaltap测试

将数据送入载波同步模块后,首先按照公式进行相关计算,得到相关值的实部和虚部。通过求反正切和换算转化为要纠正的频率的控制字data_pinpian,在flag_jiuzhen控制信号的作用下对频率控制字fcon进行纠正,设置发射机载波的频率控制字为298251617,设置接收机载波的频率控制字为298400747,对应收发两端频差是500 Hz。接收机纠正后频率控制字为298251922,与发射端的对比,频率控制字偏差值为305,换算成频率后误差为约0.25 Hz。频偏基本纠正后,通过计算delay_I与delay_Q相关值来计算相偏。首先将进来的数据通过相关计算算出相关值delta,通过查找表的方式算出角度theta,接着将角度换算成相位控制字,最后累加8个求出平均值,在flag_jiuzhen有效时将phase_right进行纠正。从图8可以看到,频率差基本得到了纠正,相位差稳定在一个很小的范围内。

图8 频偏和相偏纠正Signaltap测试图(截图)

4 结束语

由上述可以看出,这种频偏和相偏联合纠正的方法,载波同步速度很快,不会锁定在模糊相位上,而且可以适用于各种正交调制方式,适用于不同的数据率,应用范围很广,相比传统的数字式锁相跟踪环路的载波同步方法有特定的优势。

:

[1]廖腾达,谢显中,郑平莲.基于循环前缀的LTE系统多普勒频偏估计算法[J].电视技术,2010,34(1):56-58.

[2]李新花,曹叶文.一种改进的适用于分组传输的OFDM频偏估计方法[J].电路与系统学报,2011(5):1-7.

[3]许奥林,王军,彭克武,等.TDS-OFDM系统两种载波频偏估计算法及对比[J].电视技术,2007,31(12):8-10.

[4]王成,吴瑛,韩广.基于自相关函数的前向载波频偏估计算法[J].计算机工程与设计,2010,31(17):3790-3792.

[5]李永波.基于软件无线电的OFDM同步系统的研究与实现[D].重庆:重庆大学,2004.

[6]刘礼刚,曾延安,常大定.基于FPGA的反正切函数的优化算法[J].微计算机信息,2007(17):203-205.

Design of Carrier Synchronization by Using Frame Header Imformation Based on FPGA

WEI Zhaochuan,XIE Dong,CAI Chenglin

(Department of Communication and Information System,Guilin University of Electronic Technology,Guangxi Guilin 541004,China)

A design of carrier synchronization by using frame header imformation is expounded based on FPGA.First,the theory of the frequency offset estimation and phase offset estimation are described in this paper,then the design of system block diagram and submodule theory are presented based on FPGA.Finally,it is verified by Modelsim simulation and SignalTap of board-level testing.

frame header imformation;frequency offset estimation;phase offset estimation;carrier synchronization;FPGA

TN919.8

A

【本文献信息】韦照川,谢栋,蔡成林.基于帧头信息的载波同步设计及FPGA实现[J].电视技术,2013,37(3).

国家自然科学基金项目(61162007);广西区自然基金重点项目(2012GXNSFDA053027)

韦照川(1973— ),硕士,高级实验师,主研数字通信,信号处理;

谢 栋(1986— ),硕士研究生,主研数字通信;

蔡成林(1969— ),博士,教授,主研卫星导航定位,卫星通信。

责任编辑:魏雨博

2012-08-25