EDA设计中的层次化设计方法

胡 青,黄 勤,唐 丹,王延川

(重庆大学 自动化学院信息工程与自动化系,重庆 400030)

随着电子技术的飞速发展,EDA技术借助硬件描述语言对FPGA和CPLD芯片进行了编程,彻底改变了数字系统的设计实现方法[1-3]。国内多所高校开设了EDA设计的相关课程,在教学实践过程中发现了一些问题,见参考文献[4-7]。EDA技术以FPGA或CPLD芯片为编程对象,应用Quartus等开发软件,采用层次化设计方法完成数字系统设计[8-10]。本文以Quartus II为开发软件,详细说明层次化设计步骤和实现方法,并以秒表设计为例,演示了层次化设计方法的应用。

1 层次化设计的重要性

层次化设计将整个设计任务按功能划分为多个子模块分别实现和验证,大大降低了设计和仿真验证的难度[11]。更重要的是,只有掌握了层次化设计方法才能将一些常用的基本功能,如定时器、锁存器、多路开关等设计为基本元件,建立自己的元件库。这样在以后的设计开发中就可以直接调用元件库中的元件。丰富实用的元件库将大大缩短开发进程,提高开发效率。

此外,有些硬件功能必须通过宏功能模块才能使用,如ROM存储器、LPM加法器等。Quartus提供了MegaWizard Plug-in Manager工具,帮助用户根据自己的需求新建和编辑宏功能模块的设计文件,但用户必须掌握了层次化设计实现方法,才能在自己的设计文件中调用宏功能模块。

2 EDA的层次化设计方法

2.1 层次化设计思想

传统的硬件设计就是选择合适的元件,在印制电路板上将多个元件连接起来,实现某个具体的功能。这种设计思想在EDA技术中依然适用,并且更加灵活。层次化设计方法是将具体的设计任务按功能分成多个独立的模块,分别实现,经过时序仿真验证无误后,再以这些模块为基本元件,完成整个设计任务。随着设计经验的增加,元件库也越来越丰富,这是设计者的宝贵财富,可以大大缩短开发周期,降低开发难度。

层次化设计方法在设计任务时自顶向下进行分析设计,将任务划分为多个独立的子模块,而实现时则是自底向上逐层实现。

2.2 EDA设计的输入方法

EDA设计的输入方式主要分为两种:原理图方式和硬件描述语言方式。

(1)原理图设计输入是在画布上放置元件,用导线将元件引脚连接起来,添加输入输出引脚,最终完成设计。原理图设计方法比较简单、直观,缺点是Quartus应用软件提供的元件库中只有一些常用的基础元件,完全符合需求的元件比较难找。

(2)硬件描述语言将设计者从具体的硬件设计细节中解脱出来,设计者不需要深入了解具体的硬件设计,只需要用指令描述元件的逻辑功能就能完成功能设计。硬件描述语言的出现大大降低了硬件设计的难度,用硬件描述语言完成电路设计是EDA技术的核心内容,虽然有多种不同的硬件描述语言,但它们没有本质区别,都是编写代码、综合适配成相应的硬件电路。VHDL和Verilog HDL是使用较多的两种硬件描述语言。本文的设计实例采用的是VHDL描述语言方式。

2.3 层次化设计的实现方法

应用层次化设计方法完成具体的设计任务时,应自底向上逐层实现,以下层设计为基础元件完成上层设计。每一层次的设计都可以采用原理图输入或硬件描述语言输入。

(1)采用原理图输入方式。此时需要先将下层设计包装成元件,方便在原理图中调用。具体步骤:先打开下层设计文件(原理图或VHDL),选择File选单(菜单)—Create/Update子 选 单 (子 菜单)—Create Symbol Files for Current File选项,将下层设计文件生成对应的元件;然后再新建原理图设计文件完成上层设计,此时元件对话框中在Project文件夹下会多出刚才生成的元件,调用它们即完成了上层设计。

(2)采用VHDL输入方式。此时只需在VHDL文件中用COMPONENT语句声明要使用的基本元件,然后就可以根据需要定义多个元件实例,并用PORT MAP语句完成端口映射连接即可。元件声明的作用是说明要使用的元件类型;元件实例则等同于在画布上放置所需的元件芯片,根据设计需要,同一类型的元件可以有多个实例;端口映射等同于在画布上用导线连接芯片的引脚。

3 层次化设计实例——秒表

以一个简单的秒表设计任务为例说明层次化设计方法的思路和实现。秒表可以启动/暂停计时,复位则重新开始计时,时分秒以“X-XX-XX”的形式在7位LED上显示出来。7位LED的位选信号通过插孔ds1~ds7引出,而段选信号连在一起,通过插孔a—h引出,2个开关分别用作复位键和启停键。对FPGA芯片编程可以实现秒表功能,并控制LED显示。

3.1 秒表的层次化设计分析

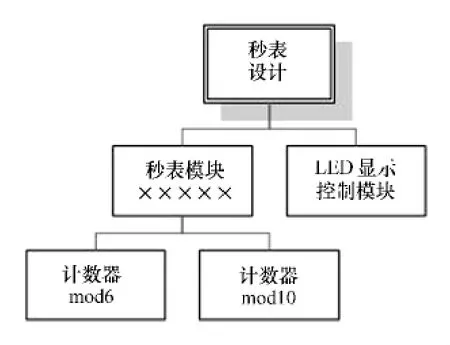

首先分析设计任务,将其划分为多个独立的子模块。按功能划分,这个设计任务明显可分为两大模块:秒表模块和LED显示控制模块。而在秒表模块中的时、分、秒都是计数器,为了方便LED显示,可以用分、秒的十位和个位分别实现,这样只需要用3个计数值为0~9的mod 10计数器和2个计数值为0~5的mod 6计数器,就可以完成秒表功能。图1为层次设计框图。

图1 秒表的层次设计框图

3.2 秒表的层次化设计实现

实现时应该自底向上,先实现下层模块,再调用下层设计完成上层设计。

3.2.1 最底层的计数器设计

用VHDL编程分别实现mod 6和mod 10定时器设计,文件名分别为mod6.vhd和mod10.vhd。

3.2.2 第2层的秒表模块设计

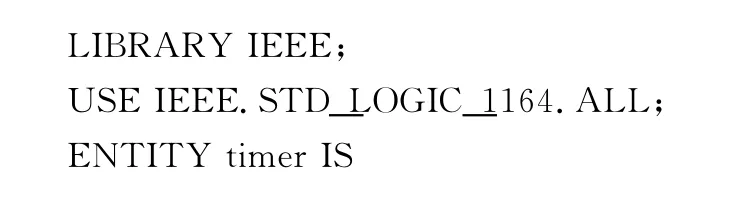

(1)用原理图输入方式完成。先打开mod6.vhd文件,点击选单生成相应的symbol文件;再打开mod10.vhd文件,同样点击选单生成symbol文件;最后新建原理图文件timer.bdf,此时双击画布的空白区域,弹出的Symbol窗口,在Project文件夹下就多了mod6和mod102个元件,如图2所示。

在画布上放置3个mod10元件,2个mod6元件,添加输入输出接口,并将它们用导线连接,就完成了秒表模块的设计。

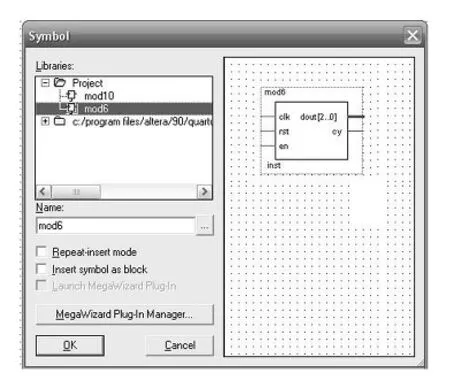

(2)用VHDL完成。新建VHDL文件,文件名为timer.vhd。只需要在结构体中给出mod 6和mod 10的元件声明,然后根据需要定义2个mod 6和3个mod 10的实例,参考程序如下。

图2 生成计数器元件后的Symbol窗口

此外Quartus可以自动生成元件声明语句,只需打开元件的设计文件,选择File选单——Create/Update子选单——Create VHDL Component Declaration File for Current File选项,就会在项目文件夹下生成与设计文件同名、后缀为.cmp的文件;打开该文件,将内容复制粘贴到当前层次设计的VHDL文件中即可。

3.2.3 实现7位LED控制器设计

用VHDL完成LED显示控制模块,文件名为ledctrl.vhd。由于篇幅限制,省略具体代码,只给出LED控制器的实体定义。

输入引脚en控制LED是否显示;输入时钟信号clk的周期控制每一位LED的显示时间,7位LED每次只有一位显示,具体显示的数值由din1~din7决定;输出引脚ds和seg分别控制LED的位选和段选。

din1~din7端口输入的数据分别显示在从右到左的第1位~第7位LED上。若输入数据在”0000”~“1001”之间LED则显示对应的字形;输入为”1010”LED则显示“—”;若为其他数据LED不显示。当clk信号频率在1kHz左右时,视觉暂停效果使得看上去7位LED同时显示不同的数值。

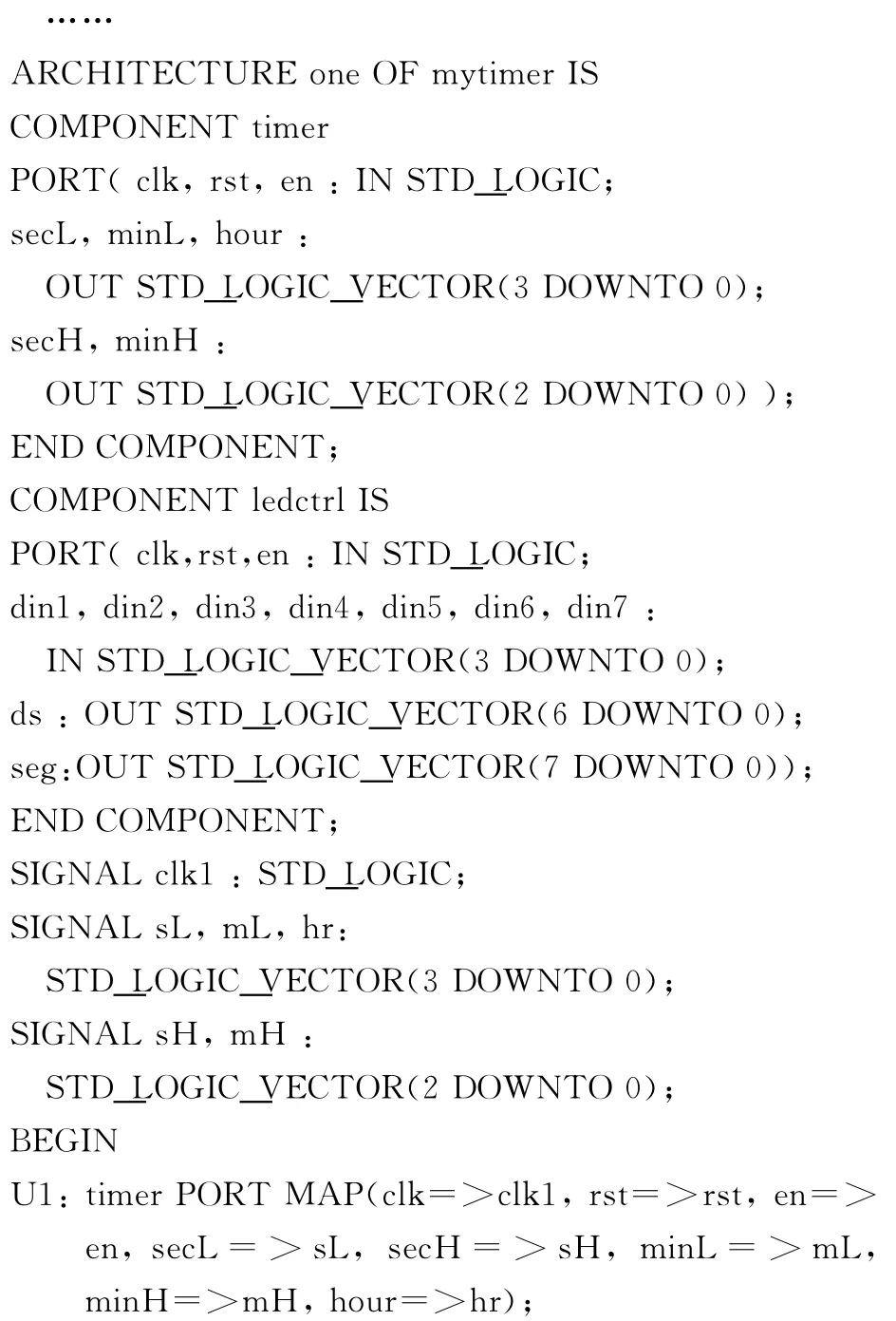

3.2.4 实现最顶层的秒表设计

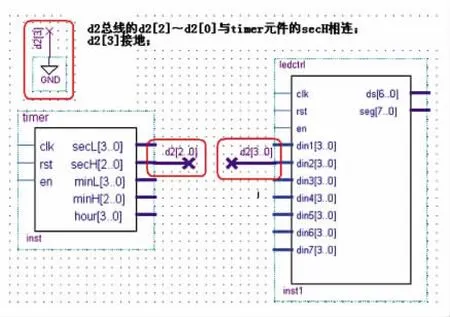

以timer和ledctrl为基础元件完成整个秒表设计和显示,需要将timer元件的输出端口与ledctrl元件的输入端口相连,而timer元件的输出secH、minH为3位总线,ledctrl元件的din1~din7均为4位总线,2个总线位数不一致时不能直接连接。第6位和第3位LED始终显示“—”,即din6和din3的输入始终为“1010”,需要向端口输入常数。

(1)原理图中的总线、分线和常数。原理图中需要分别连接某总线端口的各位信号线时,可以将元件端口用总线引出并命名,例如将ledctrl元件中的din2用总线引出并命名为d2[3..0]。d2为总线的名称,[3..0]说明该总线为4位;然后就可以用d2[3]、d2[2]、d2[1]和d2[0]分别表示d2总线中的各位信号线。

电路图中的常数意味着信号固定接地(GND)或接电源(VCC),在Symbol对话框中输入 GND或VCC,就能在原理图上放置地或电源,再用导线连接即可。

图3将timer元件中3位的secH与ledctrl元件中din2的低3位相连,din2的最高位接地。为突出连接,将相关部分用红色框出。

(2)VHDL中的总线、分线和常数。用VHDL实现最顶层秒表设计的部分程序段如下,相关代码用红色框出。

图3 3位总线与4位总线之间的连接

4 结束语

EDA技术彻底改变了数字系统的设计实现方法,硬件编程语言降低了硬件设计的难度和复杂度,而层次化设计方法自顶向下将设计任务分解为独立的功能模块分别实现和仿真验证,用户可建立自己的元件库,重复利用以往的设计成果,大大提高了设计的灵活性和效率,缩短了设计周期。

(References)

[1]赵辉.基于EDA技术的数字系统设计[J].电子设计工程,2012,20(2):34-37,41.

[2]赵刚,何志敏,陈利学.基于FPGA的EDA综合实验系统设计[J].微计算机信息,2012,28(1):49-51.

[3]潘松,黄继业.EDA技术实用教程[M].北京:科技出版社,2006.

[4]牛军浩,胡聪,殷贤华.EDA分层教育方法改革[J].电气电子教学学报,2011,33(6):115-116,119.

[5]任国凤.项目式教学法应用于EDA本科教学的探索[J].太原师范学院学报:自然科学版,2011,10(4):158-160.

[6]张惠国,潘启勇,华强,等.EDA课程层入式教学及实验平台建设[J].常熟理工学院学报:2011(12):107-109.

[7]张艳,靳孝峰.对EDA技术课程教学改革的探讨[J].教育与职业,2011(21):143-144.

[8]张艳春.数字电子系统的EDA设计方法研究[[J].现代电子技术:2009,32(17):188-190.

[9]王晓峰.可编程逻辑器件及硬件描述语言的EDA方法[J].长春大学学报,2005,15(4):14-16.

[10]孟中.基于EDA层次化设计方法的出租车计费器设计[J].现代电子技术,2011,34(16):23-24,30.

[11]王戎丞,陈可中,明鑫.基于VHDL的数字频率计的设计与实现[J].现代电子技术,2005,28(15):102-104.