基于DPLL同步的高频降压型DC-DC转换器设计

穆念强

(山东铝业职业学院 电气工程系,山东 淄博 255065)

最近10年,嵌入式技术促进便携式电子产品以惊人的速度迅猛发展和普及。目前,高效能、高精度、微体积的DC-DC转换器成为除高效能电池以外制约小型轻量高档便携式电子产品进一步发展的瓶颈。高效能DC-DC转换器改变了传统的电源设计方法,成为电子产品的关键设计技术。基于数字锁相环(DPLL)同步的降压型DC-DC转换器设计正是致力于便携式电子产品的电源应用要求而进行的研究成果。

随着数字和微处理器技术的迅速发展,锁相环(PLL)在各种各样的应用电路设计中以一种常见的构建模块得到了广泛的应用。与模拟系统相比,DPLL精度高且不受温度和电压影响,环路带宽和中心频率编程可调,不需要A/D及D/A转换,更适用于高效能、高精度和集成化的嵌入式系统。因此,本文的设计专注于数字实现,在调查了高频DC-DC转换器应用中数字锁相环电路的使用的基础上,提出了采用DPLL实现高频DC-DC转换器的数字辅助同步方案,设计了基于DPLL同步的高频降压型DC-DC转换器,并通过建模仿真验证了其优越性能。

1 采用DPLL同步方案的降压DC-DC转换器

1.1 基本降压型DC-DC转换器

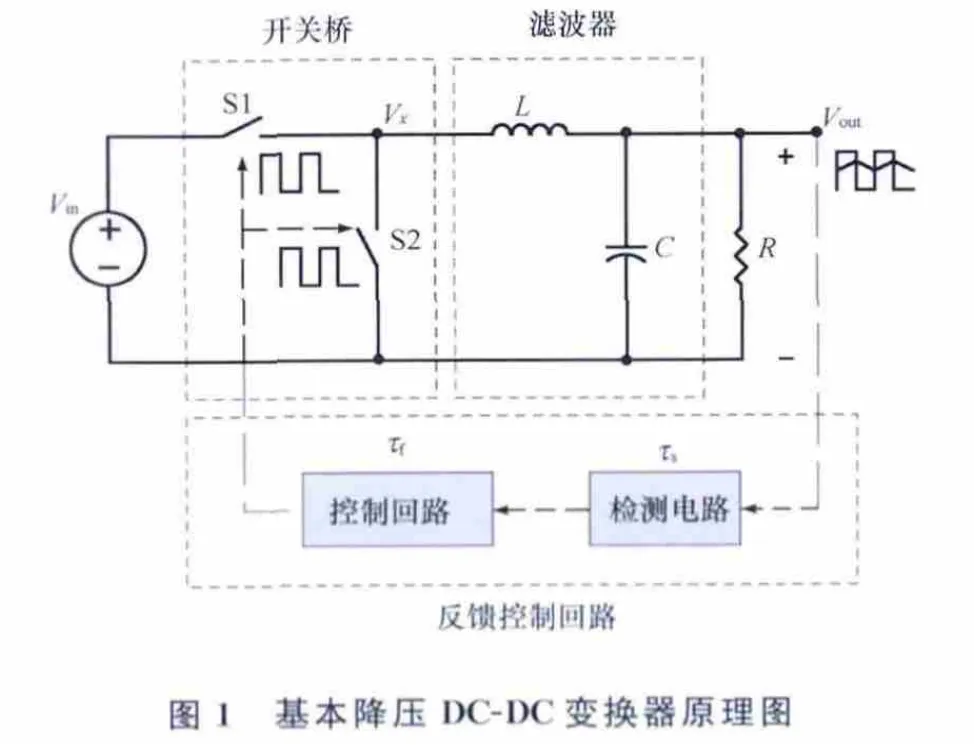

图1显示了基本降压型DC-DC变换器的基本原理。转换器可分为3个基本组成部分:开关桥、滤波器和反馈控制回路。桥输出占空比D的开关信号Vx通过滤波器生成直流输出Vout,其平均值与Vx的占空比D成正比。检测电路监测Vout,并通过反馈控制回路控制占空比,以得到稳定的直流输出。

有两种最常用的控制回路,即脉宽调制(PWM)回路和滞回控制回路。PWM回路有约为10个周期的响应时间,而滞回控制回路可以实现2~3个周期的响应,且本质上更稳定[1]。

在本设计中,选用具有迟滞特性的滞回控制回路。滞回控制DC-DC转换器适合高频率运行模式,以减小电容和电感的数量级,适应更大负荷的高性能系统的完全集成化。对高性能微处理器来说,当需要从多个电源快速切换时如电压瞬变,快速响应是特别重要的。

滞回控制回路的缺点之一是其开关频率fs对转换系数和占空比D的依赖。开关频率fs公式为

其中D是占空比,τs是传感延迟,τf是回路延迟。

可见,该转换器的开关频率fs对占空比D具有抛物线特性[2]。由于随转换电压的变化导致开关频率的变化,寄生电感与解耦电容的互连谐振可能导致电源的意外跌落。因此,需要一个已知的参考频率来固定开关频率[3]。

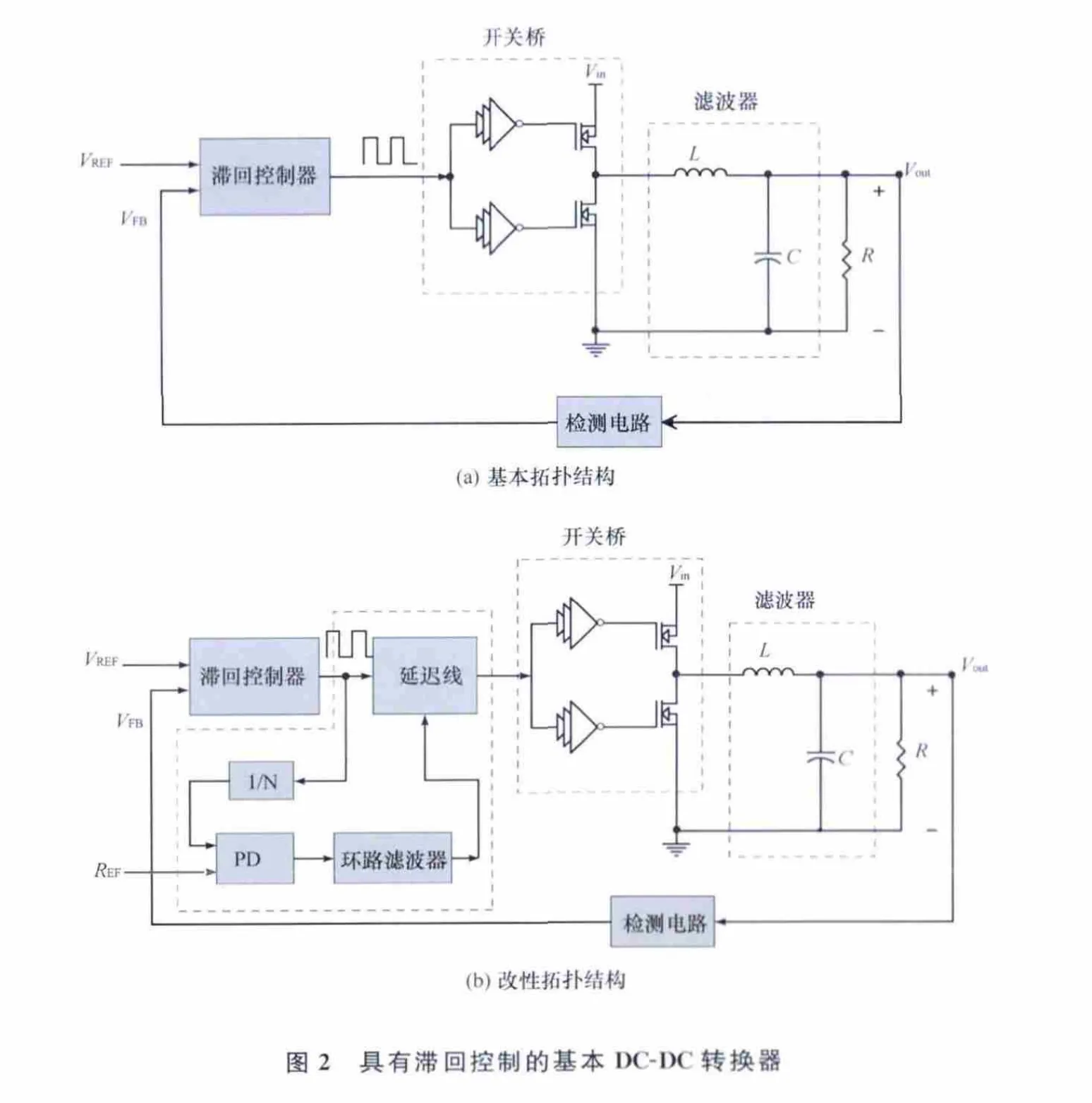

图2(a)显示具有滞回控制的DC-DC转换器基本拓扑。滞回控制器包含迟滞比较器,生成的开关信号的占空比取决于检测网络提供的反馈信号。

图2(b)显示了修改后的控制器。为了控制开关频率,在循环中插入补偿延迟线,通过改变环路延迟补偿占空比的变化。延迟线由基于锁相环的环路控制,该环路的开关频率锁定到参考频率(REF)。在本设计中,使用DPLL实现滞回DC-DC转换器的同步。数字锁相有可编程的参数,有助于调节环路的稳定性[4-5]。

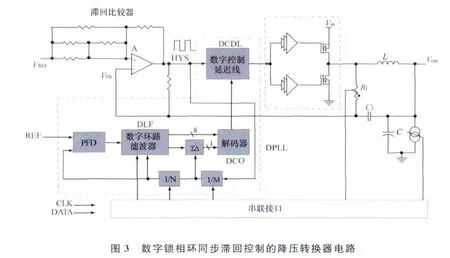

1.2 使用DPLL同步方案的降压DC-DC转换器

图3显示数字锁相同步的滞回控制降压DC-DC变换器电路的体系结构。有2个反馈回路:一个从直流输出Vout到基准参考电压VREF的电压反馈回路,另一个从迟滞比较器输出HYS到片外时钟基准REF的相同步反馈回路。电压回路有开关桥、LC低通滤波器,高通RfCf电路检测输出Vout,通过迟滞比较器的开关信号控制占空比。

电压回路可以被视为一种开关角频率ωs的自激振荡器,其振荡角频率由下式[6]决定:

振荡角频率取决于占空比D,时间常数τRC和环路延迟τf。因为D设置转换范围,而τRC同时影响负载响应和纹波,所以最好通过改变环路延迟τf实现振荡频率的同步。

为了用数字调整回路延迟,在控制器反馈路径插入一个数字控制延迟线(DCDL),如图3所示。

滞回比较器的输出HYS分频与外部参考时钟REF的比较使用开关型鉴频鉴相器(PFD)。产生的相差信息经比例-积分(PI)数字环路滤波器(DLF)过滤。环路滤波器输出的二进制数字供给一阶ΣΔ调制器和解码器DCO,进而控制DCDL。ΣΔ调制器提高了DCDL的延迟分辨率。串行接口用于DPLL参数编程,如增益和分频率。其他,如DC-DC变换器的低/高侧范围和反馈网络系数、RfCf时间常数都可编程[7]。

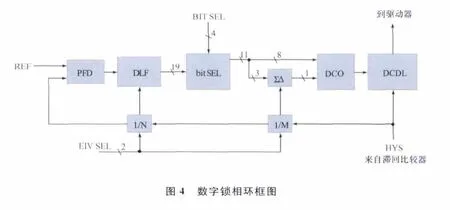

1.3 数字锁相环

图4显示了DPLL框图。开关型鉴频鉴相器(PFD)对滞回控制器的输出分频与基准时钟REF进行比较,产生相差信号送数字环路滤波器(DLF)。通过串行接口对环路滤波器的PI增益进行控制,增益系数是回路稳定的关键[8-9]。环路滤波器的输出经过bit选择器(bit SEL)选择19位中的11位,其中3位由一阶ΣΔ调制器生成一个一位比特流,与其余的8位一起形成9位的控制字(A<8:0>);其中高6位(A<8:3>)提供给2个3-8解码器(DCO)用于控制DCDL的粗延迟,低3位(A<2:0>)(包含ΣΔ输出的一位A<0>)控制DCDL的精细延迟。可编程分频器为PFD、ΣΔ、DLF和SEL提供必要的时钟。

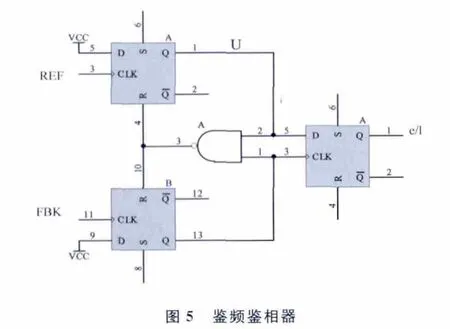

1.3.1 鉴频鉴相器

鉴频鉴相器(PFD)是锁相环的一个关键部件[4-5]。简单的鉴相器,如XOR门和j-k触发器,只在一个很小的范围内可以跟踪相位误差。当系统启动至最终锁定之前,反馈和参考信号的频率差异很大,这些鉴相器只能运行在一个有限的频率范围内,它们的能力有限。图5给出的鉴频鉴相器不受上述问题的影响。

当参考信号REF领先于反馈信号FBK信号时,e/l信号置“1”;当参考信号REF滞后于反馈信号FBK信号时,e/l信号置“0”;在采集阶段,e/l信号保持“1”或“0”。当锁定时,e/l不断在“1”和“0”之间切换。

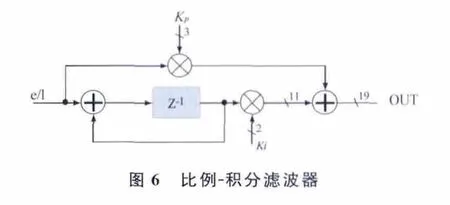

1.3.2 比例-积分滤波器

图6是一个比例-积分(PI)滤波器。滤波器的积分路径是一个可调增益的累加器,比例路径是一种可调增益的前馈路径。在这个设计中用了1个19位累加器,1个2位积分增益控制和1个3位比例增益控制。保持比例路径增益Kp高于积分路径增益Ki,增加系统的阻尼因子,提高系统的稳定性[7,10]。设计中为了回路稳定,取Kp/Ki比为3或更高。

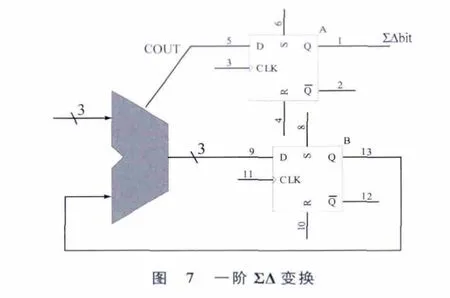

1.3.3 一阶ΣΔ变换

为增加DPLL的分辨率,设计中采用了1个一阶ΣΔ调制器(见图7)。ΣΔ调制器从滤波器取3位,采样倍数为8,生成一个一位比特流并发送到DCO。这个比特流是正常控制字速度的8倍,并在精细延迟线中控制一个三态,这有效地提高了延迟线的分辨率和抑制高频率的相位噪声。

1.3.4 数字控制延迟线

采用数字控制延迟线为控制回路提供可变延迟。延迟线分为2个优化阶段:粗调和细调。

粗调节延时链如图8所示,由63级延迟缓冲器组成,每级都有一个固定延迟,约40ps。63级延迟单元分为8组,第1组有7个延迟单元,其他组都是8个。三态门用于控制延迟量。

图8 粗调延时链

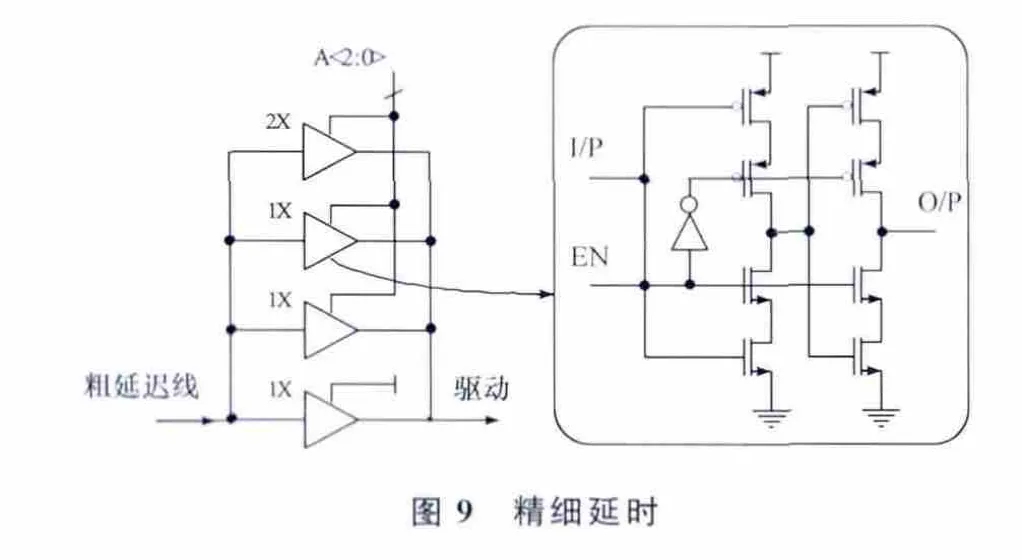

2个解码器生成粗延迟级所需的延迟时间,取决于控制字的高6位(A<8:3>)。A<8:6>选择延迟组数,A<5:3>选择末组延迟单元数。粗延迟级的输出被传递到细延迟级。细延迟级(见图9)包含1个换流器和3个并行的三态门(1x,1x,2x)。从ΣΔ变换的位流(A<0>)控制第1个三态1x,剩下的2位(A<1>,A<2>)分别控制其他三态1x和2x。

2 建模仿真结论

通过转换器的建模仿真[11-13],本文设计的数字锁相DC-DC转换器在90~240MHz的宽频率范围内,转换电压达到输入电压的33%~80%,即0.4~0.96V(Vin=1.2V)的转换范围。使用单个8.2nH电感器和20nF外部滤波电容,转换器获得120mA荷载下,阶跃响应到40ns时使纹波电压小于25mV。

(References)

[1]Hazucha P,Schrom G,Hahn J,et al.A 233-MHz 80%~87%efficient four-phase DC-DC converter utilizing air-core inductors on package[J].IEEE J Solid-State Circuits,2005,40(4):838-845.

[2]Li P,Bashirullah R,Hazucha P,et al.A delay locked loop synchronization scheme for high frequency multiphase hysteretic dc-dc converter[C]//IEEE Symposium on VLSI circuits Dig Tech Papers,2007:26-27.

[3]Xu J.On-die Supply Resonance Suppression Using Band-Limited Active Damping[C]//IEEE Int Solid-State Circuits Conf Dig Tech Papers,2007:286-287,603.

[4]李永明.锁相环设计、仿真与应用[M].5版.北京:清华大学出版社,2007.

[5]Best R E.Phase Locked Loops:Design,Simulation and Applications[M].5th ed.New York,NY:McGraw Hill,2003.

[6]Nabeshima T,Sato T,Yoshida S,et al.Analysis and design considerations of a buck converter with a hysteretic PWM controller[C]//IEEE Power Electronics Specialists Conf,2004:1711-1716.

[7]Razavi B.Design of Analog CMOS Integrated Circuits[M].New York,NY:McGraw Hill,2002.

[8]陈鑫,吴宁.数字锁相环的最优化设计[J].南京航空航天大学学报,2012,44(1):87-92.

[9]郝为强.同步降压式DC-DC转换器的稳定性设计[J].电子设计应用,2010(2):96-97.

[10]Fahim A M.A Compact,Low-Power Low-Jitter Digital PLL[C]//IEEE European Solid State Circuits Conf (ESSCIRC),2003:101-104.

[11]倪虹霞,杨信昌.基于VHDL的全数字锁相环的设计[M].长春工程学院学报:自然科学版,2005,6(3):53-56.

[12]夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[13]薛定宇.控制系统计算机辅助设计:MATLAB语言与应用[M].2版.北京:清华大学出版社,2006.