基于FPGA的新型雷达图像处理系统设计与实现

达 平,张金林,谷京朝

(空军预警学院,武汉430019)

0 引 言

随着半导体器件的不断更新换代及嵌入式系统的飞速发展,雷达信号的显示技术也发生了翻天覆地的变化。传统的雷达信号显示大多数采用单片机控制,主要依靠硬件电路实现,技术成熟,灵活性好,但设备体积大,可移植性和通用性差。近年来,雷达组网系统向数字化、信息化、智能化不断发展,越来越多的预警探测装备接入情报网络传输分发系统,这就对雷达信号的显示终端提出了新的要求。本文针对雷达视频信号数据量大、对处理速度要求高的特点,介绍了一种基于现场可编程门阵列(FPGA)的雷达视频信号采集处理系统的设计方案,并在工程中得到了很好的应用。FPGA丰富的内部资源可以充分满足高速视频采集处理系统的要求。FPGA的硬件可编程性和可重构方面的应用也使得系统集成度更高,工作模式切换更简单。

1 系统总体架构

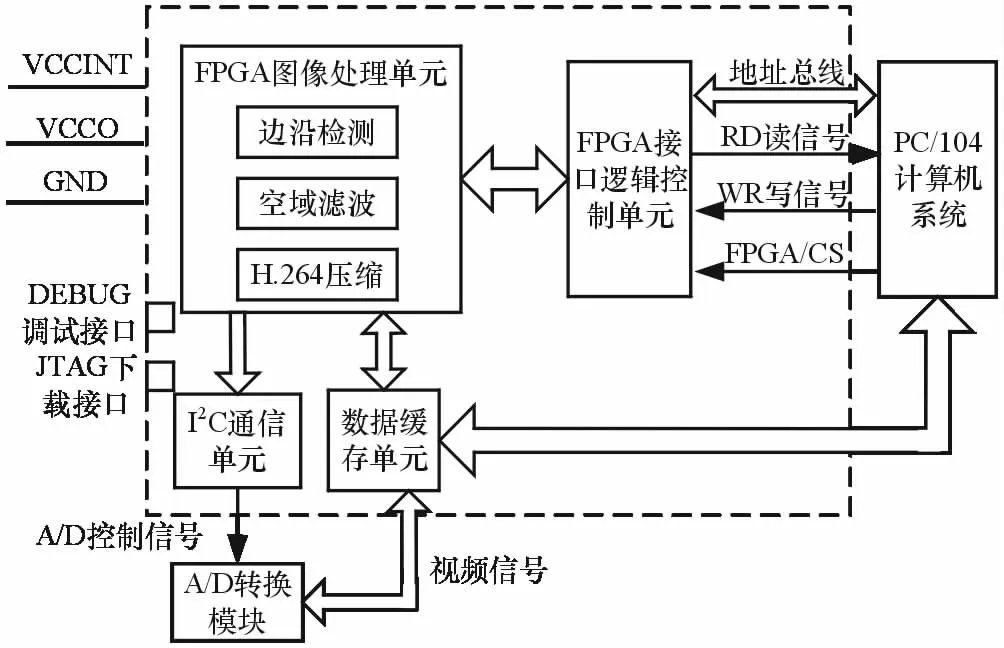

本文设计的雷达视频信号采集处理系统从功能上主要分为隔离与驱动模块、模/数(A/D)转换模块、FPGA采集控制模块、图像显示模块等。其中,FPGA是该系统的核心器件,主要实现逻辑控制,与计算机之间保持通信。系统的总体架构框图如图1所示。

当系统工作时,首先将雷达模拟视频信号输入到隔离与驱动模块进行缓冲放大及同步处理,FPGA通过I2C总线发出A/D控制信号,使A/D转换模块对其解码,转换为雷达数字视频信号。然后将其送入FPGA中进行边沿检测、滤波及视频压缩等逻辑运算处理。FPGA通过地址总线和数据总线与PC/104计算机系统进行通信,计算机可以实时地给FPGA发送控制信号,完成雷达视频信号的采集、处理和存储等功能。最后FPGA将处理完毕的雷达数字视频信号送回到A/D转换模块中,编码为雷达模拟视频信号后送至图像显示模块进行雷达情报的显示。

2 隔离与驱动模块设计

隔离与驱动模块是雷达模拟视频信号前期必不可少的预处理过程,主要功能是将输入的雷达模拟视频信号经过隔离和驱动,送入A/D转换模块进行模数变换,主要分为缓冲放大电路、同步触发电路和同步分离电路。

2.1 缓冲放大电路

缓冲放大电路主要是由射极跟随器和多级放大器构成的。射极跟随器的输入阻抗高,对前级电路影响小,可以作为多级放大器的第一级。同时它的输出阻抗低,带负载能力强,可作为多级放大器的输出级。因此射极跟随器在多级放大器中应用非常广泛,通常用作缓冲级,调整直流偏置。

2.2 同步触发电路

视频同步触发电路主要是对放大后的雷达模拟视频信号进行滤波,滤除毛刺、尖峰等,并且识别出脉宽信号,找到雷达视频信号的起始点。

2.3 同步分离电路

同步信号分离电路要保证正确地重现雷达发送终端的视频图像,主要是从雷达模拟视频信号中提取出复合同步信号(SYNC),可以用微积分电路计算出微分时间常数,与触发器组合实现。复合同步分离电路主要由运算放大器、二极管、低通滤波器、比较器组成。本系统采用的视频同步分离芯片是LM1881,可提取出复合同步、行场同步、奇偶场识别等信号。

3 A/D转换模块

数字视频信号相对于模拟视频信号来说,可以进行无数次复制且复制过程无失真,长时间存放后视频质量不会降低,并且能够进行非线性编辑。因此,模拟视频信号通常都要转换成数字视频进行处理、存储和传输。现今模数转换技术与数模转换技术都非常成熟,相关芯片设备等应用也十分方便,常用的有AD公司和TI公司的模数转换器(ADC)与数模转换器(DAC)等。

本系统选用飞利浦公司生产的视频解码芯片SAA7113及视频编码芯片SAA7121,它们内置了多标准编解码器,能够实现PAL、NTSC、SECAM复合视频的数字编解码,使用9位A/D转换器,可以接收复合视频和Y/C分量视频,具有很好的图像效果[1]。其主要作用是通过编解码将模拟视频信号与标准的视觉持久示波器(VPO)数字信号进行转换。

解码芯片SAA7113将隔离与驱动模块送来的模拟视频信号作为输入,经过模数转换为数字视频信号后送入FPGA进行后续处理。编码芯片SAA7121将FPGA处理完成的数字视频信号作为输入,经过数模转换后送入图像显示模块进行视频显示。

编解码芯片的控制信号由FPGA产生,通过Xilinx公司的ISE集成开发软件,运用超高级定义语言(VHDL)编写控制程序,具体程序如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity AD is

Port(start:in STD_LOGIC;

clk:in STD_LOGIC;

rst:in STD_LOGIC;

datain:in STD_LOGIC_VECTOR(8DOWNTO 0);

dataout:out STD_LOGIC_VECTOR (8 DOWNTO 0);

re:out STD_LOGIC;

res:out STD_LOGIC);end AD;

architecture Behavioral of AD is

signal c:STD_LOGIC_VECTOR(1DOWNTO 0);

begin

process(clk)

begin

if rst=‘1’then

if clk'event and clk=‘1’then

case c is

when“00”=>

re<=‘0’;

res<=‘1’;

dataout<=datain;

when“01”=>

re<=‘1’;

res<=‘0’;

when“11”=>

if start=‘0’then

c<=c-‘1’;

end if;

……

使用ISE软件对程序进行综合,得到的RTL级综合图如图2所示。使用Modelsim仿真软件对程序进行仿真,仿真结果如图3所示。

4 FPGA采集控制模块

FPGA是整个视频处理系统的时序逻辑控制的核心,主要实现视频信号的采集、分析、处理、存储、输出等功能。FPGA的规模比较大,适合于时序、组合等逻辑电路的应用。它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及实时在线检测等优点[2]。

按照系统的功能特点,可将FPGA的内部逻辑资源分为4个部分,即FPGA图像处理单元、FPGA接口逻辑控制单元、I2C通信单元和数据缓存单元。如图4中虚线框内所示。

图4 FPGA的采集控制模块的功能单元图

4.1 FPGA图像处理单元

该单元主要接收其他单元送来的数据,对其进行处理,经过运算产生A/D控制信号,通过I2C通信单元控制A/D转换模块的工作模式。按照信号处理流程,主要分为边沿检测、空域滤波及H.264压缩3个步骤。

边缘检测是图像处理和计算机视觉中的基本前提,主要是对数字图像中亮度明显变化的点做出标记。边缘检测去除了视频信号中许多不相关、可有可无的信息,将展示图像结构属性所必需的重要的信息保留下来,显著减少了视频信号的数据量。

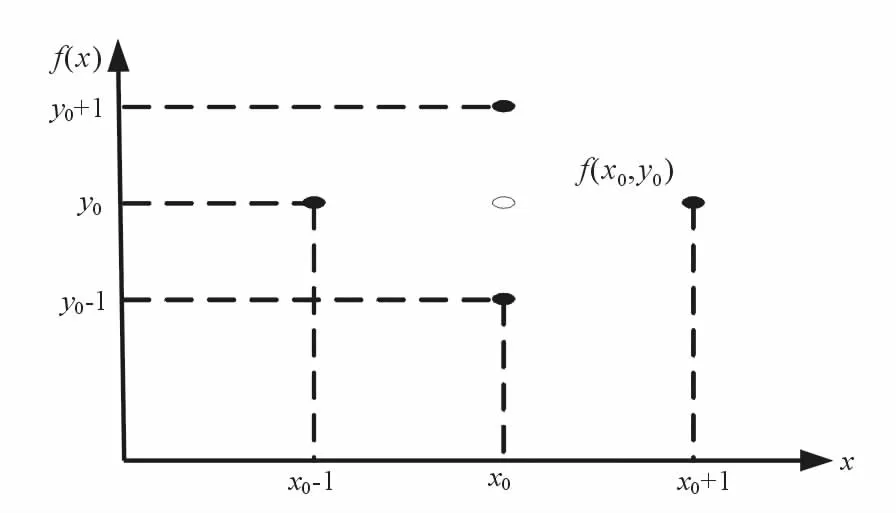

空域滤波是一种视频信号的去噪平滑技术,它首先采用均值滤波方法,确定每一像素点附近4个点的像素值的中值,去除脉冲噪声(采点位置如图5所示);然后通过低通滤波器减小高斯噪声、电子热噪声等;最后利用图像锐化滤波对图像的边缘信息进行增强,补偿压缩引起的视频信息衰减。

图5 均值滤波采样点分布图

H.264视频标准也称为高等视频编码(AVC)标准,是一种面向块的基于运动补偿的编解码器标准。H.264采用了帧内空间预测、整数变换与量化、环路滤波、熵编码、帧间编码中的运动补偿预测等新技术,能够在更低的带宽下提供优质的视频。它是以计算复杂度的增加为代价,换取编码效率的提高。在同一重建图像质量下,它的编码效率比H.263和 MPEG-4提高了1.5~2倍[3]。

4.2 FPGA接口逻辑控制单元

本系统不仅要完成视频信号的采集处理,还要进行时序逻辑控制,各个模块间要协同工作,保持同步及通信畅通。因此在FPGA中设计此接口逻辑控制单元与PC/104计算机系统进行通信。计算机产生控制信号对FPGA进行实时的控制,通过地址总线和数据总线与其进行通信。

4.3 I2C通信单元

A/D转换模块中的解码芯片SAA7113及编码芯片SAA7121可以兼容全球各种视频标准,在不同的国家应用时必须按照其使用的视频标准对芯片内部的寄存器进行设置,否则就不能相应地输出符合要求的信号。这个过程也称为初始化过程,需通过I2C总线进行,遵从I2C总线协议[4]。

用VHDL编写程序,烧写在FPGA中,可控制SAA7113及SAA7121的工作状态,准确调控各信号时序,可移植性好,能适应高速信号控制的需要。

4.4 数据缓存单元

FPGA断电后数据丢失,每次工作时都需要在加电的情况下将程序重新下载到FPGA中,因此在系统设计的过程中,增加一个同步动态随机存储器(SDRAM)。将程序保存在SDRAM中,使每次加电后程序自动加载到FPGA中。

数字视频信号经过FPGA逻辑运算单元处理后,在先进先出(FIFO)中以数据帧的形式暂存。由于FPGA的内部资源有限,且数据掉电丢失,故而也送至SDRAM中存储。

5 结束语

针对目前雷达视频信号的数据量大、信号格式类型繁多等问题,本文提出了基于FPGA的雷达视频采集处理系统。该系统运用FPGA对雷达模拟视频信号进行数字化,通过多级处理,实现雷达视频信号的采集提取、去噪压缩、高分辨率显示。

与传统的雷达视频采集处理系统相比,本设计具有占用资源少、体积小、低功耗、可扩展性好、处理速度快等优点。目前,该设计已成功应用于某系统中,具有较高的工程应用价值,军事经济效益显著。

[1]谢剑斌,徐晖.数字视频处理与显示[M].北京:电子工业出版社,2010.

[2]李林,谢代华,冯正勇.基于FPGA的数字光端机的设计与实现[J].重庆职业技术学院学报,2006,15(3):148-150.

[3]高文,赵德斌,马思伟.数字视频编码技术原理[M].北京:科学出版社,2010.

[4]曾庆立,孟凡斌,陈善荣.基于CPLD的SAA7113的初始化及其控制设计[J].吉首大学学报,2009,30(6):66-70.