基于FPGA 的DDR2 PHY 层控制器设计

魏腾飞

(西安电子科技大学,西安,710000)

0 引言

目前由于DDR2 成本低,PCB 设计和信号完整性设计的相对容易,所以仍广泛使用。DDR2 和以前传统的SDRAM 不同,DDR2 采用双倍数据速率接口,也就是说在相同的系统时钟频率下DDR2 的接口数据速率是SDRAM 的两倍。而且由于DDR2 接口工作频率较高,所以DDR2 的数据线一般是每8bit 就有一位独立的数据采样信号DQS。这样就能较好的满足数据采样的建立和保持时间。而且DDR2颗粒的工作时钟使用差分时钟线,能够减少共模干扰和时钟的抖动,提高了时钟信号的质量。

在一般的工程应用中,基本使用的是xilinx 或Altear 公司的FPGA。各自都提供有DDR2 控制器的IP CORE,其使用也比较简便。但是在一些特定的应用环境下,并不能达到最优的效果。而且IP CORE 内部代码是不可见的。由此考虑到,设计一个DDR2 PHY 层控制器,把和DDR2 控制相关的逻辑,全都放在PHY 层。而最底层的DDIO 和上层的应用逻辑,则可以根据实际情况来设计。这样,使得逻辑的代码修改量减小,提高了重用性。下面就Altera 的Cyclone系列的FPGA 来介绍设计的相关重点。

1 DDR2 PHY 层控制器的整体结构分析和设计

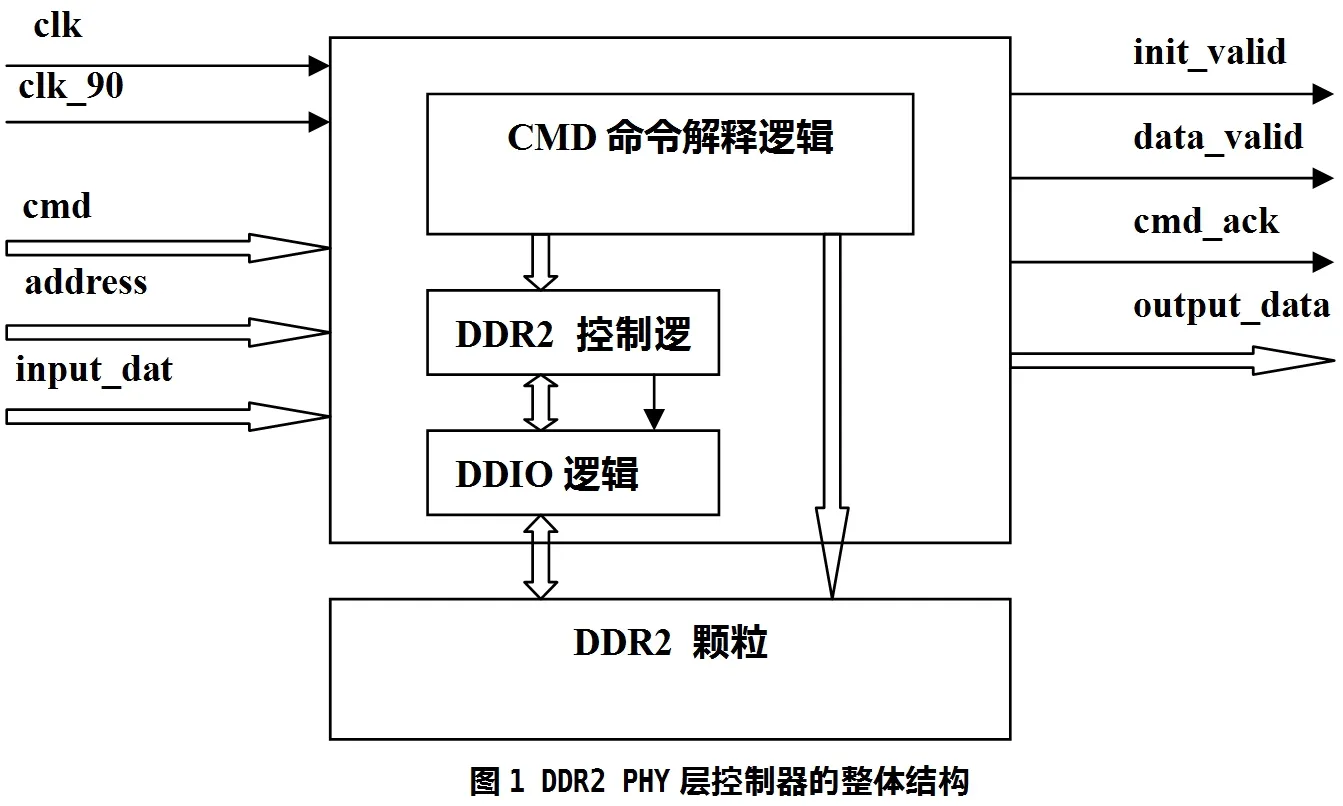

DDR2 PHY 层控制器主要由命令解释逻辑,DDR2 控制逻辑和DDIO 逻辑三部分构成。其中DDIO 逻辑,由于各个系列的IOB 结构有所不同,需要根据器件,并由工具生成。在Altera 的Cyclone 系列中DDIO 逻辑的IP CORE 使用是免费的。本着使用简便,和接口信号少的原则,DDR2 PHY 层控制器的整体结构如图1。

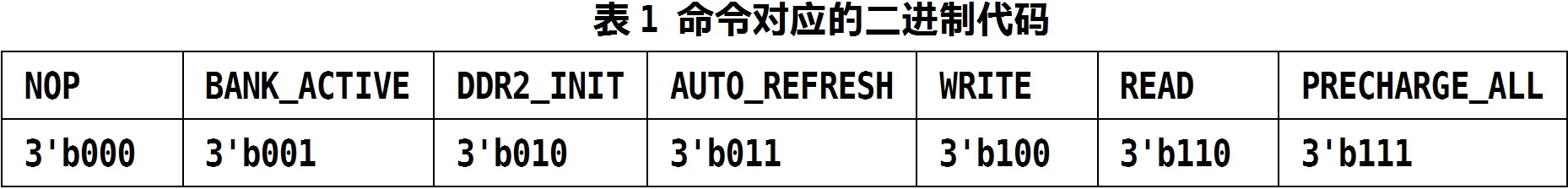

控制器的信号介绍,整个系统的时钟由clk 和clk_90 输入,clk 和clk_90 同频,但是clk_90 的相位超前clk 相位为90 度。一般有FPGA 内的PLL 锁相环提供这两路时钟信号。Cmd 信号是控制整个逻辑的命令线由3bit 组成,命令包括:NOP,BANK_ACTIVE,DDR2_INIT,AUTO_REFRESH,WRITE,READ 和PRECHARGE_ALL。具体的对应关系见表1。address 是控制器的地址输入线,位数由 DDR2 颗粒的容量决定。input_data 是数据的输入端。init_valid 信号输出高电平表示DDR2 颗粒初始化完成可以进行其他操作。data_valid 信号输出高电平表示output_data 输出数据线上的数据有效。cmd_ack 信号为高表示控制器正在执行当前命令。为低表示当前命令完成,并进入到NOP 状态。

2 DDR2 PHY 层控制器的设计与实现

2.1 DDR2 PHY 层控制器的DDIO 实现

DDIO 接口逻辑是连接FPGA 和DDR2 之间的桥梁。它完成如下功能:数据输入,通过特有的DQS 信号采样。数据输出,并产生相应的DQS 信号。实现数据速率的转换。因为在系统时钟频率和DDR2颗粒数据位宽一定的情况下,FPGA 内部一般是单沿数据处理的,而DDR2 是双沿采样,所以如果DDR2 颗粒的数据位宽为16bit 的情况下,那么转换到FPGA 内部就形成了一拍32bit 的数据位宽。

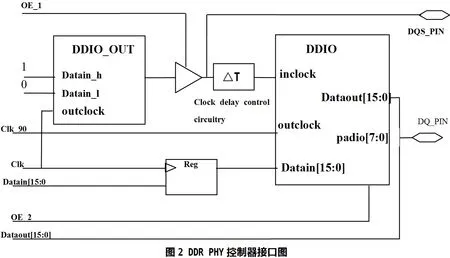

在Altera 的Quartus 中的MegaWizard Plug 先生成8bit 的DDIO 和1bit 的DDIO_OUT 的例化模块。具体结构如图2。

其 中 的Clock delay control circuitry 是Cyclone 系 列FPGA 内部的一个固件逻辑。固定连接在一个PIN 上面,所以在分配PIN 的时候,要把DQS 分配在有延时功能的PIN 上面。Cyclone系列构成的高数据速率的DDIO 接口,在写周期时,其DQS 信号是由DDR2 PHY 控制器产生的,而DQS 的边沿和DQ 数据组的中心对齐。在读周期时,其DQS 信号是由DDR2 颗粒产生的,而DQS 的边沿和DQ 数据组的边沿对齐。这个要特别注意。因此在读周期时,DQS通过FPGA 内部的Clock delay control circuitry 模块,将DQS的边沿和DQ 数据组的中心对齐,实现DQ 数据组的采样。在写周期时,DQS 的边沿和DQ 数据组的边沿相差90 相位移,所以要用超前90 度的Clk_90 来打DQ 数据,而用clk 来输出DQS,这样就实现了DQS 的边沿和DQ 数据组的中心对齐。

2.2 DDR2 PHY 层控制器的逻辑实现

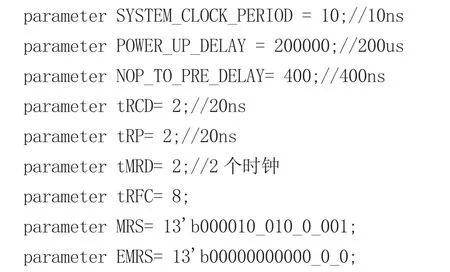

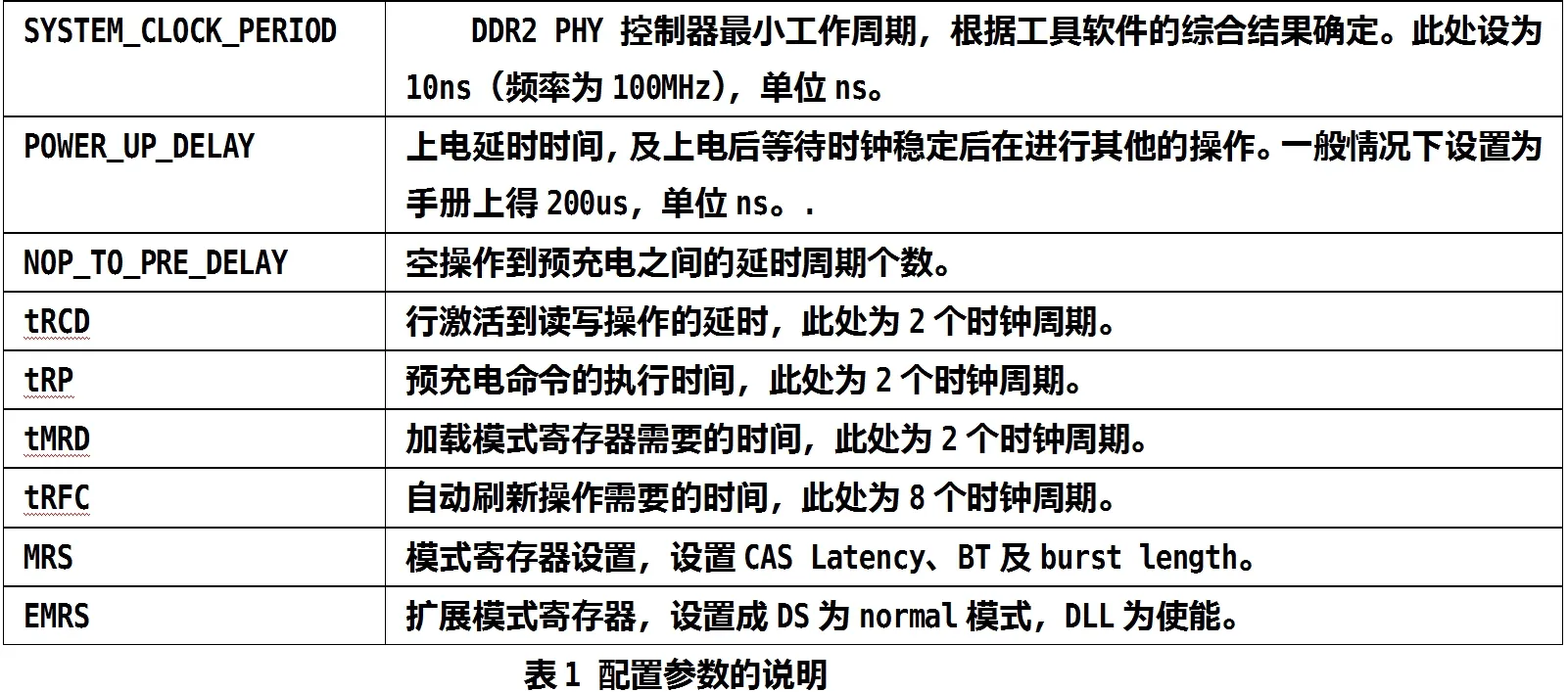

本逻辑是整个DDR2 PHY 层控制器的核心,所有操作DDR2 颗粒的工作,都由其完成。在应用本控制器前,需要根据DDR2 颗粒器件的数据手册,来设置一些合适的参数才能正常工作。包括上电延时,用来等待时钟信号稳定POWER_UP_DELAY 延时,空操作到预充电的NOP_TO_PRE_DELAY 延时,tRCD,tRP,tMRD,tRFC,MRS,EMRS 等。由于本控制器使用了verilog 的parameter 来定义。使得参数可以任意修改,来应用在多种DDR2 器件上面。DDR2 大部分的不同器件的参数是一样的,有时只是,不同厂家的参数稍有不同而已。从而使得模块的灵活性增强。参数的设置如下:

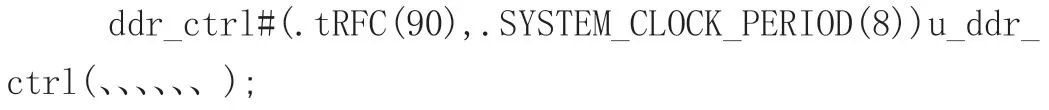

以上参数都是参考DDR2 芯片手册设定的,本例参考MT46V16M16 的器件手册设置的。在使用过程当中如果想将tRFC改为90ns 而系统时钟改为125MHz,其他不变时,那么只需这样例化即可:

这样根据具体的DDR2 的器件,来例化一个可用的PHY 层控制器。

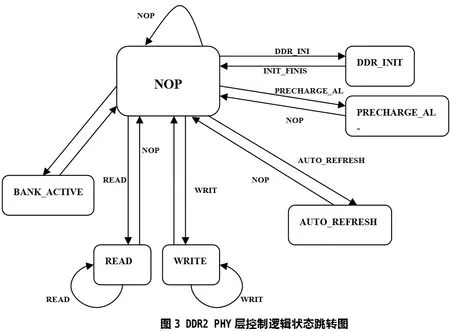

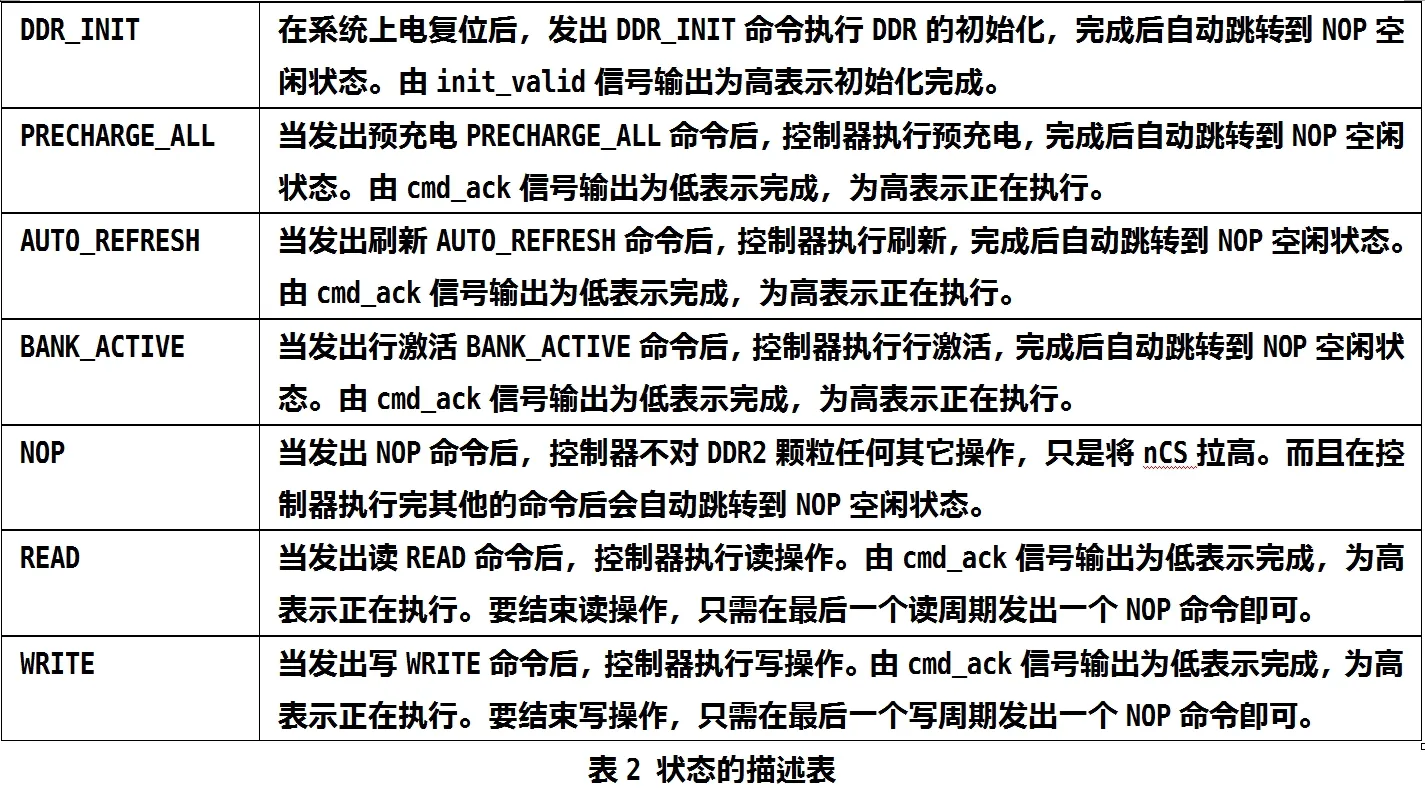

DDR2 PHY 层控制器是由一个状态机来控制运行的,通过当前的命令和当前的状态来决定下一步的操作。而且为了提高时钟频率和满足时序要求,控制器中用了流水线。当在连续读或连续写的时候,流水线内部逻辑的处理速度达到时钟频率。但是单次操作时效率会有所降低,所以因尽量多使用连续的读写操作来达到较高的数据吞吐速率。下图介绍了DDR2 PHY 层控制器的状态跳转图3,表2 为各状态的描述表。

如图3 所示,这里主要介绍NOP,AUTO_REFRESH,READ 和WRITE。NOP 是控制器的空闲状态。在没有其他操作的时候,应该给出NOP 命令使控制器跳入空闲状态。好处是在NOP 状态下,DDR2 颗粒的nCS 为高,没有选中DDR2 颗粒,这样可以降低部分功耗。在READ 和WRITE 时,控制器输入或输出的数据长度,由READ和WRITE 命令给定的时钟周期个数决定。例如READ 命令给出的2个时钟周期,那么就会执行2个读命令,WRITE 命令同理。唯一的区别是在READ 命令中,由于使用了流水线,所以读出的数据有效必须由data_valid 信号来指示。即在发出READ 命令后,当data_valid 信号为高时表示控制器的输出数据线的数据是有效的,可以进行采样。AUTO_REFRESH 为刷新命令,最好跟据具体的应用情况来安排AUTO_REFRESH 命令的发出周期和发起时间。但是在某些应用中甚至可以不用AUTO_REFRESH 命令。比如在一些视频图像数据缓冲的应用中,数据只是在DDR2 中临时存储,但很快就会被取走,写入和取走的间隔小于64ms。在这样的应用中,就可以不用AUTO_REFRESH 命令。这样不但简化了DDR2 的操作,也使得DDR2 的数据吞吐的可用带宽提高。

下面介绍DDR2 PHY 层控制器的读写时序。仿真是在modelsim6.0 下进行的行为仿真。DDR2 用的是Micron SDRAM DDR2 的BFM(MT46V16M16),此BFM 带有状态命令打印,可以实时的在命令行里看到BFM 的状态,比较方便。在进行读写时,提前要激活BANK。图省略了BANK 的激活。

3 结论

本文介绍的DDR2 PHY 层控制器,在Cyclone II 系列的FPGA 上使用,占用的资源情况和性能如下表3:

可以看出它的资源占用率是比较少的,而且工作频率也较高。而Altear 的DDR and DDR2 SDRAM Controller 9.0 版本的IP CORE 在Cyclone II 系列上使用频率为167MHz。在实际的项目应用中,操作简便,性能良好。应用在不同的DDR2 器件上只需修改参数即可应用。加快了项目的进度。

[1] Altera.Cyclone III Device Handbook,2010.

[2] Altera.Quartus II 12.0 手册,2012.

[3] XILINX.针对Spartan-3 FPGA 的DDR22 SDRAM 存储器接口,2011.

[4] Micron.Double Data.Rate SDRAM,2010