Ka频段低杂散上变频器设计及实现

杨晓雷 苗利军

(中国电子科技集团公司第五十四研究所河北石家庄 050081)

1 引言

上变频器用于实现中频信号到射频信号的频谱搬移,以利于信号的空间传输。Ka 频段(26.5~40 GHz)和其他频段相比,具有可用带宽宽、通信容量大、设备体积小等特点。在毫米波通信系统中,低杂散Ka 频段上变频器作为其中的关键部件,越来越受到人们的重视。文章对Ka 频段低杂散上变频器的设计和工程实现进行了研究。介绍的Ka 频段低杂散上变频器采用3 次变频方案,将UHF 频段中频信号上变频至Ka 频段。通过优化方案设计,采用高性能混频器、滤波器等方法,在信号射频输出带内获得较低的杂散和较为理想的幅频特性。测试表明,该上变频器性能优良,工作状态稳定,符合设计指标的要求。

2 方案选择及电路组成

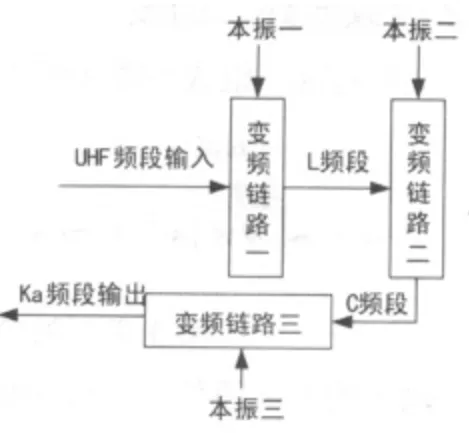

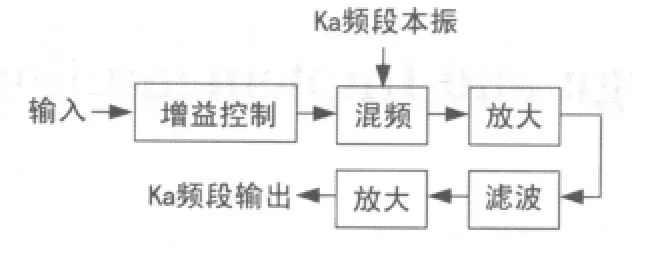

Ka 频段上变频器主要设计技术指标如下:①增益:≥20 dB;②带内平坦度:≤3 dB;③杂散抑制:≥50 dBc。此上变频器设计的关键是各级中频选择及电平分配。从频率变换的过程来看,变频器可以分为一次变频、二次变频和多次变频等形式。根据本设备技术指标及频率接口的要求,并考虑混频器等器件的技术指标,设计选用3 次变频方案。Ka 频段上变频器由变频链路一、变频链路二、变频链路三组成,如图1所示。

图1 Ka频段上变频器电路组成

变频链路一完成UHF 频段中频输入至L 频段一中输出的频谱搬移;变频链路二完成L 频段一中信号至C 频段二中信号的频谱搬移;变频链路三完成C 频段二中信号至Ka 频段射频信号的频谱搬移。其中,变频链路一重点在于低杂散设计;变频链路二重点在于带通滤波器设计;变频链路三重点在于增益控制电路、射频滤波器及Ka 频段本振源的设计。

3 关键电路设计

3.1 变频链路一的设计

变频链路一原理如图2 所示。

图2 变频链路一电路组成

输入的UHF 频段中频信号经过混频后输出L 频段的一中频信号,经滤波、放大后输出。低杂散输出是变频链路一设计的难点,设计采用-5 dBm 本振驱动电平、-0.5 dB 转换增益的高线性、双平衡、有源混频器LT5521 来满足低杂散要求。该混频器采用双平衡式设计,使本振到输出的泄漏很低,有助于抑制偶次谐波的产生并提高本振-射频输出的隔离度,从而减轻了输出滤波器对本振抑制的压力。为避免各本振之间的串扰对输出信号质量的影响,必须对本振信号进行屏蔽、隔离和滤波。杂散信号主要有:①本振信号及其谐波泄漏;②输入信号及其谐波与本振信号及其谐波混频得到的产物。

根据设计的特点,兼顾带外杂散指标,设计时将混频器输入电平降到-10 dBm 混频,可以保证带内杂散优于-60 dBc。为避免通道本振成为其它通道的杂散,必须用滤波器滤除。当本振电平为-5 dBm 时,混频器本振-射频的隔离度为35.5 dB,混频后本振电平为-40.5 dBm,当输入-10 dBm 信号时,混频后信号和本振电平差为30 dB。设计选用LC 滤波器,兼顾带内平坦度指标,滤波器对本振抑制优于20 dBc,最终变频链路一对本振的抑制达到50 dBc 以上。最后,变频链路一的杂散抑制优于50 dBc,幅度平坦度优于1 dB。

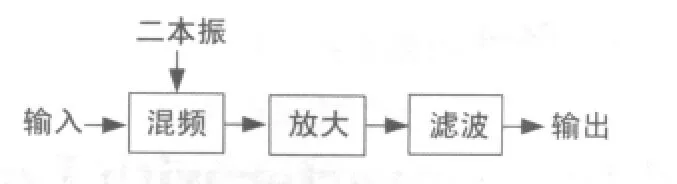

3.2 变频链路二的设计

变频链路二组成框图如图3 所示。

图3 变频链路二电路组成

输入的L 频段信号经混频输出C 频段信号,经放大、滤波后输出。对于该链路,设计时必须分腔设计,避免本振串扰形成带内杂散。

变频链路二的设计重点在于带通滤波器的设计。C 频段带通滤波器既要保证带内平坦度,又要保证带外抑制。设计时,选用Rogers4350B 板材,其介电常数为3.48,厚0.508 mm。在工艺保证的同时,对滤波器准确设计是滤波器成功的关键,带通滤波器选用切比雪夫原型设计,采用7 阶终端短路式微带滤波器。首先用Ansoft Designer 电路设计软件对滤波器进行了初步设计,然后通过Ansoft HFSS 三维电磁场仿真软件对其进行精确仿真,最后根据仿真结果在电路中对设计参数进行优化,最终得到满意的仿真结果:插损最大3 dB,带内平坦度小于0.5 dB,带外抑制60 dBc。实测时,滤波器插损约3.2 dB,带内平坦度小于0.5 dB,带外抑制约55 dBc。

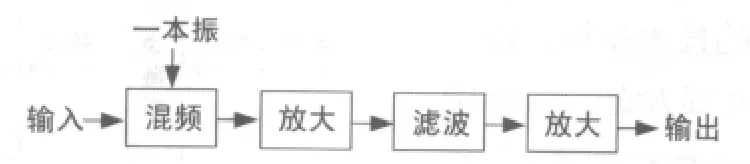

3.3 变频链路三的设计

变频链路三原理框图如图4 所示。

图4 变频链路三电路组成

输入的C 频段信号经过增益控制电路后,在混频器中与Ka 频段本振信号混频、放大、滤波后输出所需的Ka 频段信号。变频链路三的重点在于增益控制电路、射频滤波器、Ka 频段本振源的设计。理论上,增益控制电路设置在上变频器输出端比较合适,但增益控制电路在Ka 波段实现非常困难。增益控制电路在上变频器设计中主要考虑以下几个方面:①最大增益由输入最小电平和输出最大电平决定;②最小可控衰减量由上变频器最大输入电平和最大增益决定;③最大可控衰减量由输出最小电平决定;④增益控制电路衰减过大时不能对噪声系数影响太大,否则会影响输出信号的信噪比;⑤增益控制电路衰减过大时不能对杂散抑制指标影响太大。综合考虑,设计在C 波段用数控衰减器实现上变频器的增益控制。

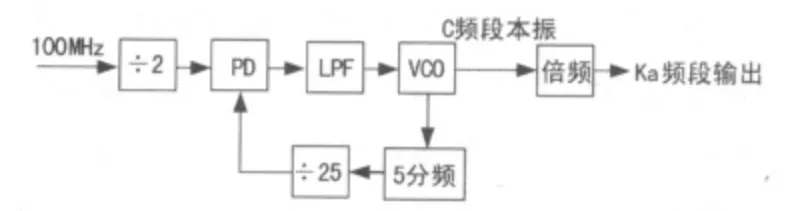

射频滤波器通带用来滤除带外无用信号。采用5 节平行耦合线结构,采用微带薄膜工艺在0.63 mm 厚陶瓷基片上实现具体电路。根据指标要求研制了该滤波器,其带内损耗小于4 dB,带内幅频特性0.5 dB,对本振频率的抑制达到5 dBc 以上。设计中,Ka 频段本振采用锁相单环和倍频来实现,工作原理框图如图5 所示。

图5 Ka 频段本振原理框图

相位噪声计算如下:鉴相频率50 MHz,此时鉴相器的本底相噪指标为-156 dBc/Hz@10 kHz,输出频率的倍频次数为125,则输出信号相噪指标为-156+20lg125≈-114 dBc/Hz,后又经过4 倍频器相噪恶化12 dB,由环路及其部件引入的噪声影响一般变差3 dB,最终输出理论相噪指标可达到-99 dBc/Hz@10 kHz。

4 关键技术

4.1 微组装技术

采用微组装工艺实现有源电路MMIC 与无源电路的混合集成,可以有效的减小体积,达到小型化的目的,但同时对设计人员、工艺人员的要求也进一步提高,宽带电路对微组装的工艺细节更加敏感,特别是比较高的Ka 频段。

在Ka 频段,金丝互连结构的高频效应主要影响到增益平坦度、回波损耗等指标,对于宽带射频电路更是如此。金丝焊接的性能受如下因素影响:①金丝的条数、粗细、长度、拱高;②金丝与金丝间的间距;③金丝距离微带线的高度。金丝互连时金丝的拱高应尽量低,同时也应尽量降低微波芯片焊盘与传输线之间的高度。金丝的拱高对微波电气性能存在的影响有几个方面:①拱度过高带来的局部高阻抗会导致与微波芯片的连接失配,进而导致驻波比变差;②拱度过高还会出现较强的高频效应,使微波电路出现自激,导致微波电路无法正常工作。

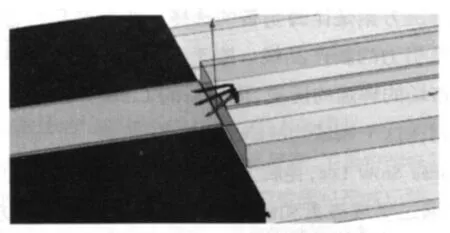

通过仿真,得到如下结论:①在单根键合金丝、同跨距的情况下,拱高越平、越低对微波传输特性的影响越小。但平直键合金丝受到温度冲击或震动时容易发生断裂,所以键合金丝须保持适当的拱高;②在同拱高的情况下,跨距越短对微波传输特性影响越小;③双金丝的驻波比、插入损耗性能优于单金丝;三根金丝的性能稍有提高,但金丝根数越多性能提高越不明显;④金丝发散式排列时,能够获得更好的微波传输特性。为此,设计在试验和实际电路的组装中都采用了发散式排列三金丝互连结构,如图6 所示。

图6 发散分布互连三金丝结构

微波管芯的接地状况对增益、插入损耗、变频损耗等有较大影响,接地不好会导致芯片自激、谐振,进而引起电路的串扰。微波芯片良好的接地需要用优质导电胶均匀、无气泡的将基片或可伐材料粘接在腔体上,任何气泡都会带来意外的分布电容加载,使得微波传输特性发生变化,从而导致不连续性,在微波传输线上出现较强的反射,轻则降低微波有源器件的增益,重则带来不稳定性和振荡,导致微波电路自激。所以微组装工艺必须保证电路接地良好。

4.2 宽带增益平坦度技术

对于宽带上变频器的增益平坦度而言,影响的因素有很多:①无源器件在工作频段内不平坦,例如:滤波器通带边缘的衰减要比通带中心大些,微带线拐角在高频时的反射会大一些;②微波混频器、微波放大器等MMIC 器件在工作频段内插入损耗或增益的不平坦;③各种吸收点,比如微组装出现的高频寄生效应、腔体设计的不合理、滤波电路中电感的谐振等原因造成的谐振等;④混频器本振端输入不同频率的增益平坦度;⑤微波器件之间阻抗不匹配或匹配不好。

为了实现较好的宽带增益特性:①应通过设计避免吸收点造成的影响,控制好微组装工艺细节对宽带射频信号传输的影响,包括金丝键合的寄生参数、同轴-微带转接头的驻波特性、以及螺旋电感和单层电容的谐振等;②混频器、放大器等MMIC 芯片本身插入损耗或增益的不平坦基本上都是线性的,必要时可以设计幅度均衡器进行补偿;③在设计小型化滤波器等器件时要给通带留一定的余量,在满足带外抑制的前提下尽量扩展滤波器的带宽,使滤波器的应用频带内具有比较好的平坦度。

另外,各微波器件之间阻抗不匹配导致的幅度不平坦性,一般情况下可以通过以下措施解决:①对微波器件驻波比达不到指标要求的,通过外围电路的设计加以改善,必要时可以加3 dB 以上的衰减器改善驻波比;②在微波频段,各器件的级联变得很困难,任何小的阻抗失配都会对平坦度造成很大影响,通过调整各级电路的匹配状态,增加电路中各级的隔离度等方法,达到各器件的良好匹配;③仔细筛选器件,确保在工作频段内具有良好的幅度特性和阻抗特性;④仿真设计的滤波器等电路,必须保证良好的驻波比及平坦度指标,避免由于匹配不好造成滤波器波形的变化;⑤中频带通滤波器设计为平顶带宽,避免中频滤波器边缘下降对射频通带平坦度的影响。

5 上变频器性能指标

最后,测得的整个Ka 频段上变频器性能指标如下:①增益:≥20 dB;②增益平坦度:≤2 dB;③杂散抑制:≥50 dBc;④增益控制范围:30 dB 步进0.5 dB;⑤相位噪声:优于-99 dBc/Hz@10 kHz,测试结果表明Ka 频段上变频器指标优良。

6 结束语

介绍了低杂散Ka 频段上变频器的设计,对其中的关键电路进行了较为详细的描述,对杂散产生及其抑制进行了分析。试验测试结果表明,设计为低杂散上变频器提供了一种适宜工程实现的方法。

[1]张凯,延波,徐锐敏.Ka 频段上变频模块的设计[J].电讯技术,2007,47(5):100-103.

[2]苗利军,张东,孙宝平.幅相一致低杂散多通道上变频器设计[J].无线电工程,2009,39(12):46-48.

[3]孙琳琳,赵昕,郑翠翠.一体化Ka 波段上变频组件[J].电子工程师,2008,34(12):21-24.

[4]薛良金.毫米波工程基础[M].哈尔滨:哈尔滨工业大学出版社,2004.

[5]贾世旺.EHF 频段上变频器设计及实现[J].无线电通信技术,2010,36(3):37-39.

[6]ROHDE.U L,NEWKIRK.D P.无线应用射频微波电路设计[M].刘光祜,张玉兴译.北京:电子工业出版社,2004.