封装基板引工艺线电镀金工艺设计

张良静*,吴梅珠,高艳丽,郭永刚

(江南计算技术研究所,江苏 无锡 214083)

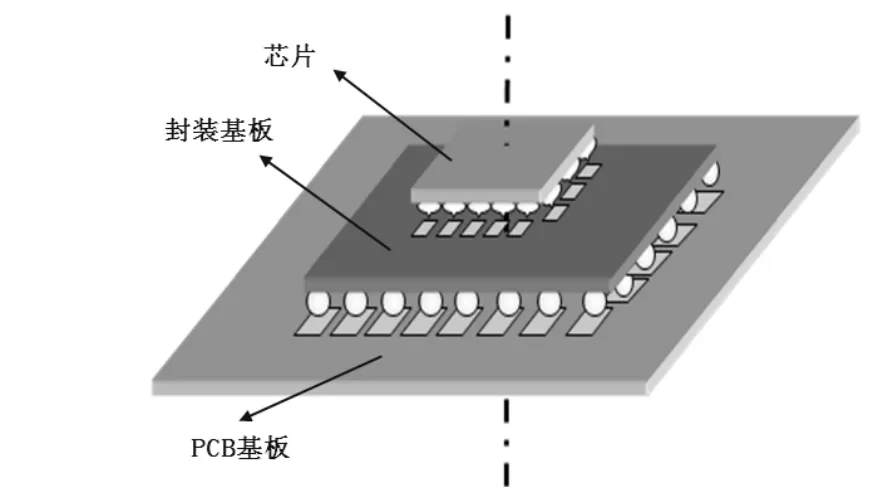

封装基板(也称载板)是用于承载电子元器件的印制电路板,可为芯片提供电连接、保护、支撑、散热、组装等功效,以实现多引脚化,缩小封装产品体积, 改善电性能及散热性,超高密度或多芯片模块化的目的。如图1所示,先将裸芯片(Die)安装到封装基板上,再安装到常规密度的大尺寸PCB 基板上。

IC 芯片互联通常采用键合(Bonding)方式进行,其中一种方法需要将金线打在芯片与封装基板键合点(绑定盘)上形成电路连接,一般要求对封装基板的键合点进行电镀金处理。而封装基板与PCB 板的互联通常采用球栅阵列(BGA)方式进行,有时也要求对基板背面布置的二维球栅阵列进行电镀薄金处理。

电镀金时需要将镀金焊盘连成一个网络形成电流回路,因此必须设计电镀工艺线将所有焊盘连接并引出至导电夹头[1],电镀完毕,必须断开工艺线。无论采用何种方式断开,均会有一部分工艺线残留,因此需要设计尽量少的镀金引线并采用合适的方法将工艺线去除。本文分别对封装基板内埋键合点和球栅阵列电镀金工艺线的设计及工艺实现流程进行了研究,并分析了其工艺难点。

1 工艺线设计

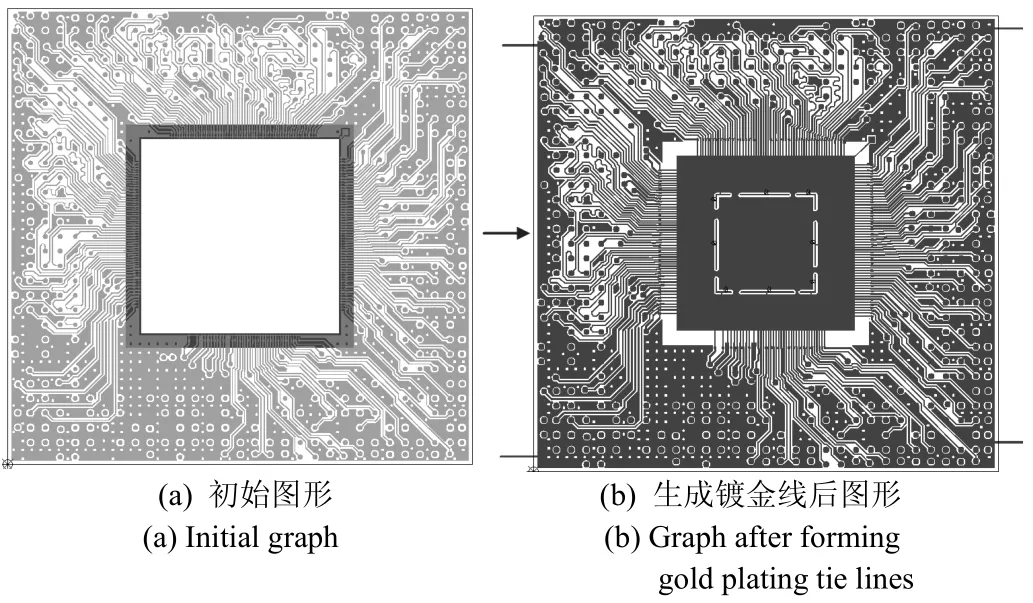

图2a为基板底层球栅阵列的初始CAM(计算机辅助制造)数据,此类阵列排布的焊盘镀金线可以通过CAM 工具Genesis2000 中的BGA Tie Line Generation功能自动生成,如图2b所示,建立镀金阵列(Array),在有效图形边框外加一闭合框,使所有引线全部连通成一个网络。

图3a为基板埋孔外层初始CAM 数据,由图可见内埋的键合点全部位于有效图形内部边框线周围,通过在废料区铺设铜皮并将工艺线全部引向铜皮使所有键合点连通成一个网络,再从外围铜皮4 个角各引一条线至有效图形外的辅助框上,如图3b所示。

2 工艺流程

2.1 球栅阵列镀金流程

图4所示为封装基板球栅阵列镀金制造流程。

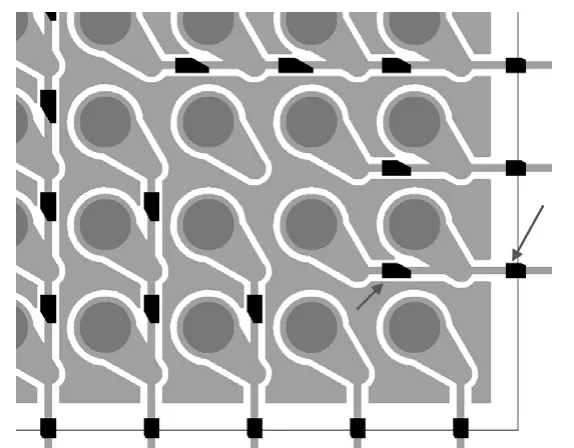

首先通过图形转移蚀刻工艺形成外层图形及镀金工艺线图形,接着用网印的阻焊膜覆盖不需焊接的线路和过孔盘,起到保护和防焊作用,同时在阻焊层上设计断线图形,断线图形的位置与外层表面镀金工艺线需要断开的位置相对应[2],如图5所示,这样阻焊显影时需要断开的工艺线上方的阻焊膜将被显掉,为后续蚀刻掉这一位置的工艺线做准备。

为防止露出的工艺线在后续镀金过程中被镀上金,需要采用耐镀金干膜将刚刚阻焊露出的镀金工艺线先保护起来,即用耐镀金干膜将断线图形完全覆盖住,将需要镀金的焊盘露出进行镀金处理,设计镀金图形菲林时将镀金焊盘处设计成遮光区,其余位置包括 断线图形处设计成透光区,这样曝光显影后再镀金时,镀金焊盘表面镀覆了金,工艺线有干膜保护没有镀上金,而金具有抗蚀性。褪除耐镀金干膜后,再进行碱性蚀刻时,镀金工艺线断线图形部分被蚀刻掉,不会影响已镀金焊盘及其他覆盖阻焊的线路层。

图4 封装基板球栅阵列镀金制造流程Figure 4 Manufacturing process of gold plating on BGA package substrate

2.2 内埋键合点镀金流程

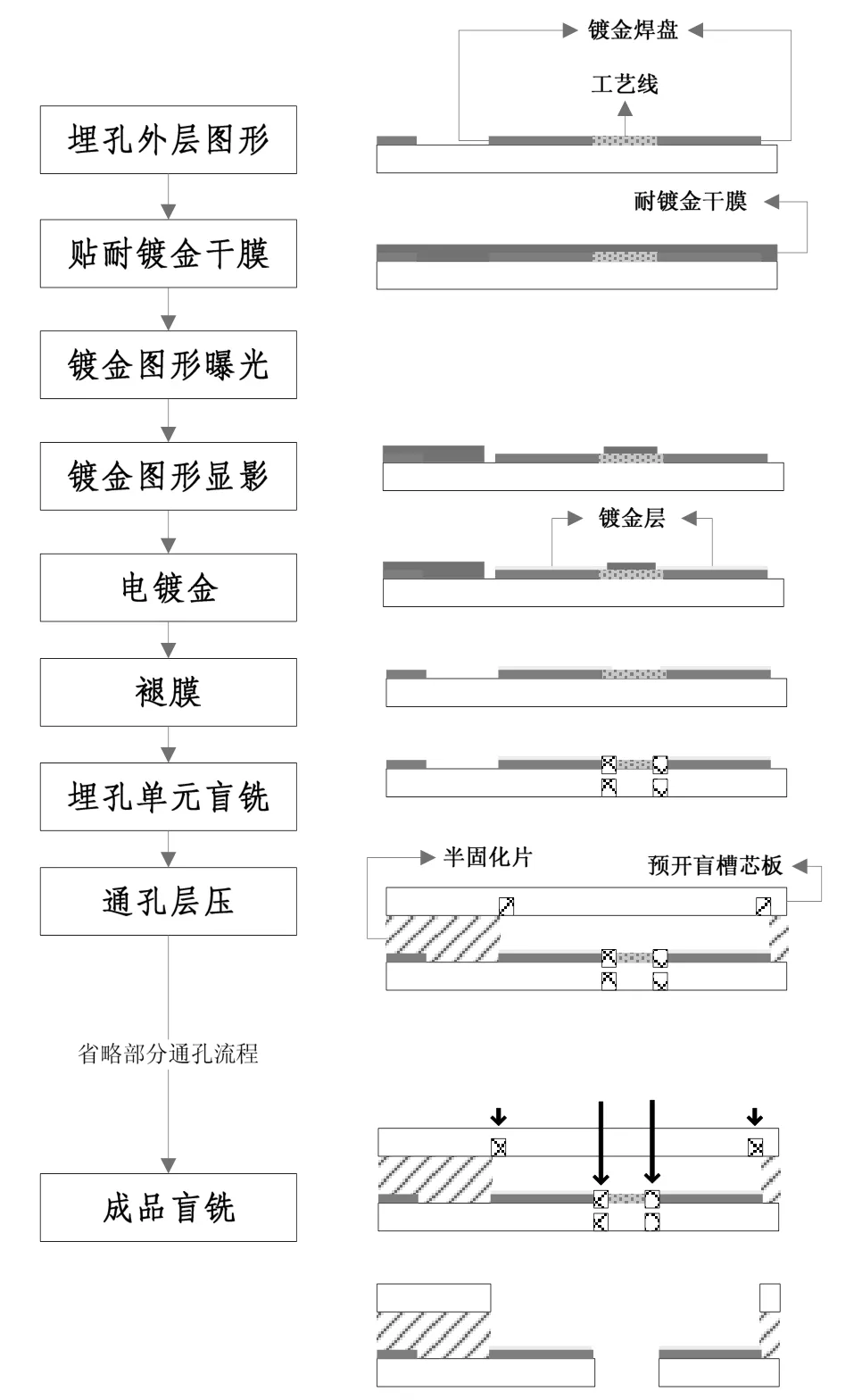

图6所示为封装基板内埋式键合点镀金制造流程。

图6 内埋键合点镀金制造流程Figure 6 Process of gold plating on embedded bonding pads

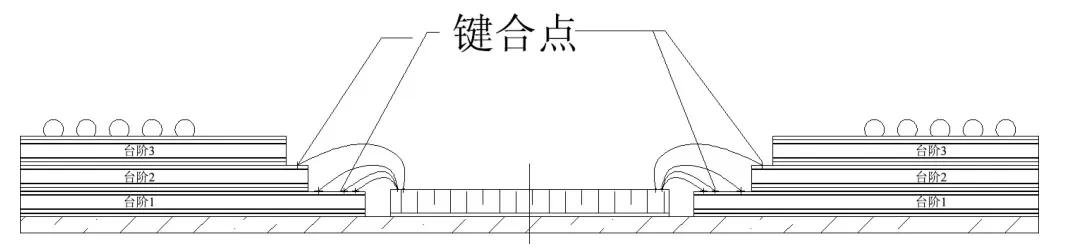

内埋键合点镀金工艺与球栅阵列镀金工艺的差异在于要求将镀金的键合点镀金后经压合而埋置于基板内部,需将键合点上部挖空形成台阶。具体为:首先通过图形转移蚀刻工艺形成埋孔外层图形及镀金工艺线图形,接着采用常规镀金工艺,即贴耐镀金干膜 并通过曝光、显影,使需要镀金的焊盘露出,需要键合的区域在电镀金后再褪除耐镀金干膜,此时需从埋孔单元顶、底层分别盲铣,从顶层向底层盲铣是为了铣开与焊盘相连的镀金工艺线,从底层向顶层盲铣则是为成品盲铣铣通槽做准备,然后预先开盲槽的芯板与埋孔单元配套层压,此时键合点已经被埋入基板内部, 通过成品盲铣将上方的芯板揭开即形成台阶,露出键合区域。

图6所示为仅有一个台阶时的制造流程示意图,基板存在多阶台阶时(如图7)的制造流程与此类似,仅需增加在不同位置的盲铣。

3 工艺难点

采用碱性蚀刻工艺去除球栅阵列镀金工艺线的难点在于控制每次图形曝光对位精度,因此阻焊断线图形设计时要考虑到曝光设备的能力,一般要求阻焊开窗边缘距外层图形(Coverage)≥25 μm。

采用盲铣工艺去除内埋键合焊盘镀金工艺线的难点在于盲铣的深度公差控制,一般需要控制盲铣深度为0.10~0.15 mm。

4 结语

本文根据2 种封装基板镀金区域的特点,设计出专用的镀金工艺线及相应的镀金工艺,可满足封装基板不同镀金设计和制造需求。

[1]韩建波,张鹏.带电插拔的金手指设计[J].电子工艺技术,2003,24 (2): 71-72.

[2]淳华科技(昆山)有限公司.软式印刷电路板电镀金引线断线刻蚀设计方法: CN,101841977 [P].2010-09-22.