动态轨道衡数据采集与传输系统的SoPC设计

刘文彬,张文爱

(太原理工大学 信息工程学院,山西 太原030024)

动态轨道衡是一种安装在铁路上的对通过的列车实现不停车动态检测的称量设备。整个轨道衡系统中,数据采集与传输部分位于系统最前端,它的采样速率、传输稳定性等指标直接决定了系统的性能和工作效率。因此,要提高动态轨道衡的性能与称量速度,首先应从数据采集与传输系统着手。

传统动态轨道衡数据采集与传输系统多使用单片机、ARM等器件设计,一旦制作完成,修改和升级将十分困难。但由于轨道衡使用领域广泛且应用环境多变,因此传统设计大多只适用某一领域,可升级性和通用性较差。与传统方法不同,SoPC设计用FPGA芯片作为核心,通过IP复用技术将一系列IP核组成可编程片上系统,为动态轨道衡数据处理系统带来了灵活、可裁剪等新特性,为适应不同领域的应用需求提供了简单易行的解决方案。

本文根据SoPC设计方法与IP复用技术的思想[1],提出了由高精度高速模/数转换器(ADC)AD7714、以太网控制器ENC28J60、IP核和FPGA芯片构成的新型动态轨道衡数据采集与传输系统的SoPC设计方案及实现方法。该系统充分体现了SoPC设计的优势,具有开发时间短、灵活高效、易于升级等特点。

1 系统概述

在动态轨道衡数据处理领域,已有许多采用FPGA器件的设计,但这些设计大部分只将其用于数据采集控制,在数据传输部分(如以太网传输)仍使用单片机进行控制。这样并未构成完整的SoPC设计,不仅增加了系统的体积,还限制了系统的整体运行速度。在需要根据不同使用环境对系统进行调整时十分困难,无法充分体现使用FPGA器件进行SoPC设计的优势与灵活性。

本文根据动态轨道衡的应用需求,设计了一款完全基于SoPC方案的FPGA数据采集与传输控制系统。系统设计采用Altera公司的Quartus II集成开发环境和EP1C12芯片开发平台,通过使用已有IP核与自主设计IP核相结合的方法完成开发。设计使用IP复用技术将整个系统集成至一片FPGA芯片,不仅极大地节约了系统开发时间与成本,同时由于FPGA芯片的现场可编程特性,通过软件编程即可改变系统的硬件功能,使系统的更改与升级工作变得十分简便,赋予了系统灵活高效、易于升级的特点,对应用广泛、使用环境多样的动态轨道衡十分有利。另外,FPGA器件优秀的并行处理能力与低功耗特性使其优势更加突出。

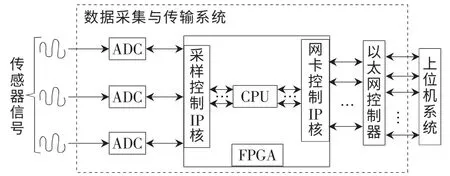

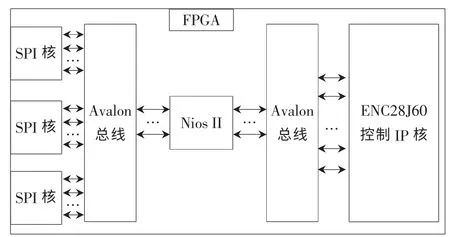

系统总体结构如图1所示,可分为数据采集、以太网传输和SoPC控制核心3部分。数据采集部分包含3片ADC对8路信号同时采样,FPGA芯片突出的并行处理能力很好地协调了各芯片的协同工作。SoPC控制核心系统内部由多个IP核构成,处理器核心CPU采用Nios II软核处理器,采样转换控制IP使用开发环境提供的SPI控制核,以太网芯片控制IP使用自主设计的以太网控制器ENC28J60专用控制IP核。

图1 数据采集与传输系统结构框图

2 功能电路与SoPC控制核心开发

2.1 数据采集电路与控制模块

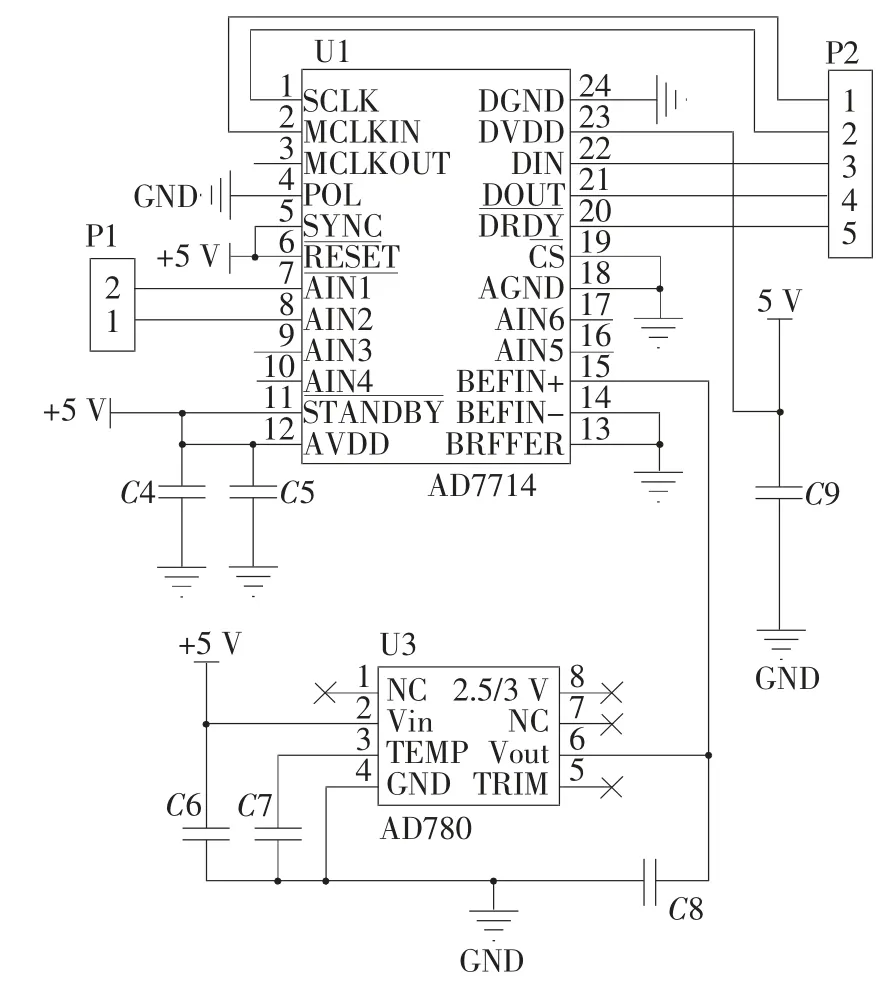

ADC选用ADI公司的AD7714,该芯片最高可实现24 bit无误码转换,同时具有SPI兼容的三线接口,控制简单。它的模拟输入端可以配置为5路准差分输入或3路全差分输入。通过实验发现,准差分输入时信号干扰较大,所以采用全差分输入来抑制共模干扰。对8路传感器信号进行转换需要3片AD7714芯片。AD7714的电路原理如图2所示,传感器信号由P1接口输入,AD7714三线SPI接口、主时钟输入端及DRDY引脚由P2引出并与控制模块相连。

图2 AD7714电路原理图

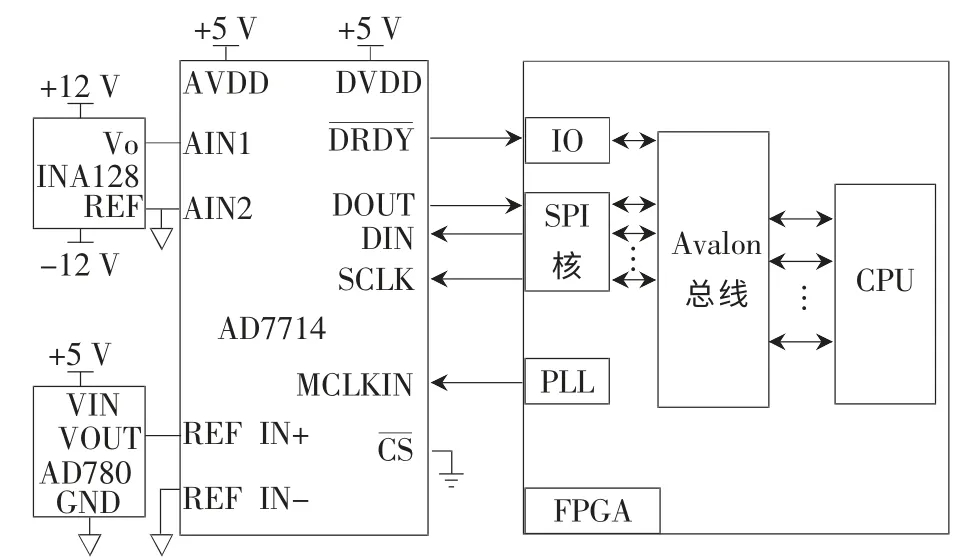

对数据采样的控制采用了开发环境提供的SPI控制IP核。数据采样电路与控制模块的连接如图3所示。INA128将毫伏级传感器信号放大至A/D转换量程范围内[2],AD780提供A/D转换所需的2.5 V基准电压[3]。AD7714主时钟MCLK由FPGA芯片内部的锁相环PLL(Phase Lock Loop)产生,设置SPI核的时钟频率为5 kHz,寄存器位宽为8 bit,空闲时钟相位为0。AD7714数据转换状态由引脚指示,当为0时说明数据寄存器有更新,即产生了新的采样数据。因此在控制模块中添加一个通用IO引脚来监视的状态变化[4],当有新数据产生时,由软件程序控制读取采样数据。

图3 数据采集电路与控制模块

2.2 以太网数据传输电路与控制模块

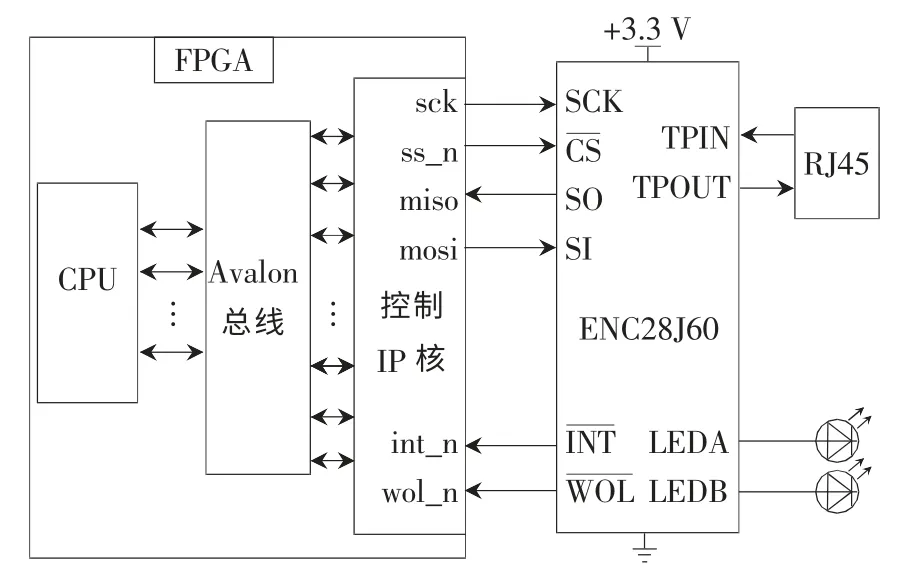

数据传输由以太网通信实现,设计采用以太网控制器ENC28J60。ENC28J60是Microchip Technology公司推出的带有标准串行外设接口SPI(Serial Peripheral Interface)的独立以太网控制器,任何配备SPI接口的控制器都可以使用该芯片作为以太网接口[5]。设计采用现成的ENC28J60网络模块进行开发。

现有的设计都是用SPI核加通用I/O口的方式对ENC28J60进行控制,并没有专用的控制IP核。这样的设计方法在不同的系统中需要较大的改动,无法体现IP复用的设计理念。因此本设计开发了基于Avalon总线标准的专用控制IP核。Avalon总线是Altera公司提供的一个开放的总线标准,基于其标准的设计完全免费,并且其接口标准与Wishbone等常用的片上总线相似,只需极少的改动便可在不同的系统下移植和使用,充分体现了IP复用的设计理念[6]。

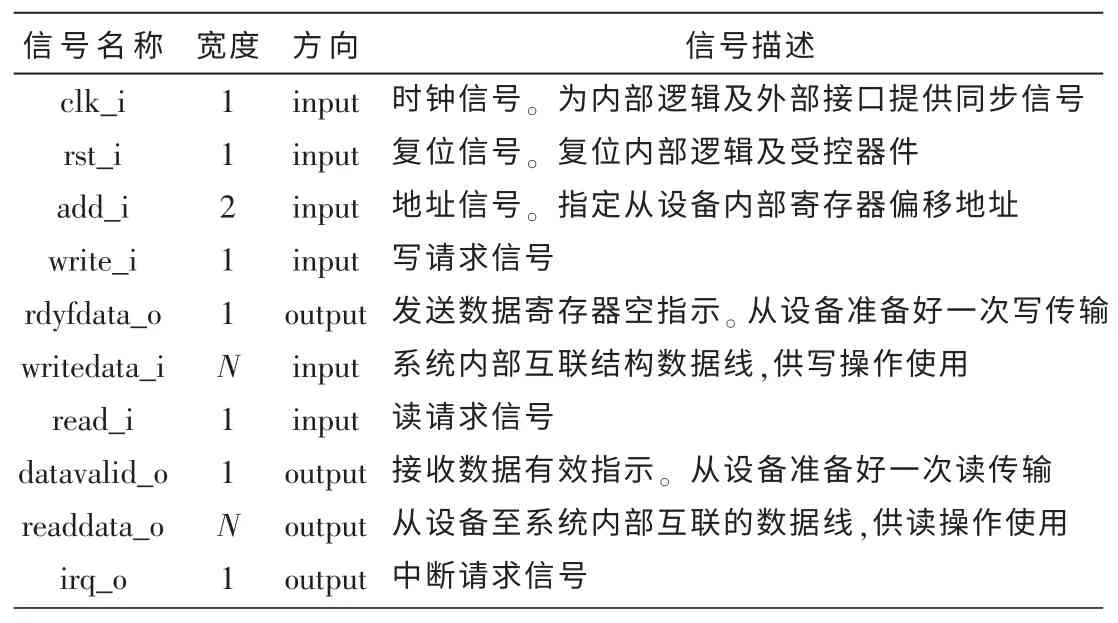

2.2.1 IP核接口设计

IP核接口信号包含两组,一组是与网卡芯片之间的接口,另一组是Avalon从接口信号。IP核与ENC28J60之间的接口是固定的,有SPI接口信号sck、ss_n、mosi、miso和中断输入接口int_n、wol_n。对 于Avalon总 线 信号,一个Avalon从外设中可以包含任意的信号类型,在这里根据IP核的需求而定[7]。设计所用到的Avalon从接口信号及描述如表1所示,表中N为程序中用类属参数定义的数据线宽度,方便修改以适应不同的应用。

表1 Avalon从接口信号

2.2.2 IP核内部逻辑设计

专用IP核内部由寄存器逻辑和任务逻辑构成。寄存器逻辑包含状态寄存器EJSTAT、控制寄存器EJCTRL、接收数据寄存器RXDATA和发送数据寄存器TXDATA。状态寄存器中的各位表示IP核的状态,包括接收溢出错误标志、发送溢出错误标志、接收/发送寄存器空标志以及ENC28J60芯片中断标志,通过控制寄存器相应位置1可以使能各标志中断功能。接收和发送数据寄存器是有效数据的暂存空间。

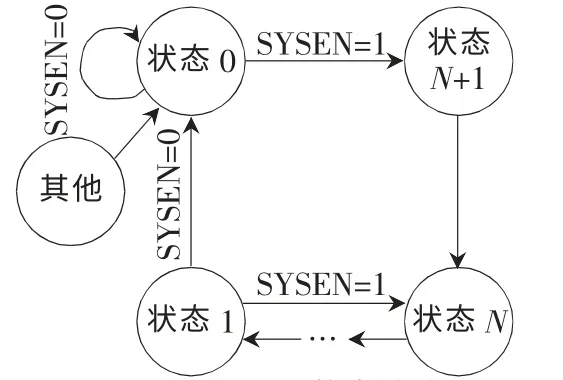

任务逻辑由输入输出逻辑、寄存器操作逻辑以及有限状态机FSM(Finite State Machine)3部分组成。其中有限状态机是任务逻辑的核心,负责完成SPI数据的输入/输出、状态寄存器相应位清零或置位操作。FSM共有N+1个状态,状态转移如图4所示。sysen是控制寄存器中系统使能控制位,高电平有效,表示进入系统操作,否则系统不工作。

图4 FSM状态转移图

状态0为系统的初始状态,此状态下令SPI时钟输出使能端无效,再判断系统是否使能,由判断结果决定进入下一状态或停留在该状态。当SYSEN=1,系统进入状态N+1,说明即将开始数据操作,该状态使能SPI时钟sck与从机选择信号ss_n输出,为数据操作做准备。状态N~状态1为有效数据移位操作状态,在这N个状态中完成相应的数据移入和移出操作。在完成N位数据操作之后,如果系统使能位依然有效,则系统进入下一个数据操作循环,否则系统回到状态0。

以上接口设计和内部逻辑在Quartus II环境下使用VHDL语言编程实现。编译报告显示程序正确无误,共用220个逻辑单元,占逻辑单元总数的2%。最终以太网数据传输模块结构如图5所示。

图5 以太网传输模块

2.3 SoPC控制核心

构建SoPC控制核心的工作使用SoPC Builder组件完成。SoPC Builder是一个自动化SoPC硬件系统开发工具,它可以使设计者在很短的时间内定义一个完整的硬件系统[5]。它提供了简单方便的用户图形界面,设计人员只需在该环境下添加所需的模块,再通过添加片上总线将各个模块组合起来即可构成完整的SoPC系统。

SoPC控制核心开发第一步是为系统添加CPU,设计选用Altera公司的Nios II嵌入式软核,与其他常见的嵌入式软核相比,Nios II具有更高的主频且占用较少的逻辑资源;然后,在SoPC Builder环境下添加SPI核和自主设计的网卡控制IP核;最后,通过Avalon片上总线将各控制模块与Nios II软核连接起来,就构成了数据采集与传输系统的SoPC控制核心,其内部结构如图6所示。

图6 SoPC控制核心内部结构图

3 操作系统移植与应用程序设计

Altera提供了Nios II软件集成开发环境Nios II IDE,所有处理器软件开发任务(如编辑、调试等)都在该环境下完成。

设计选用嵌入式实时操作系统μC/OS-II,它的结构简洁精练,可读性很强,同时又具备了实时操作系统的全部功能[8]。Nios II IDE开发环境中提供了μC/OS-II工程,通过添加工程即可方便地实现操作系统移植。

3.1 应用程序设计

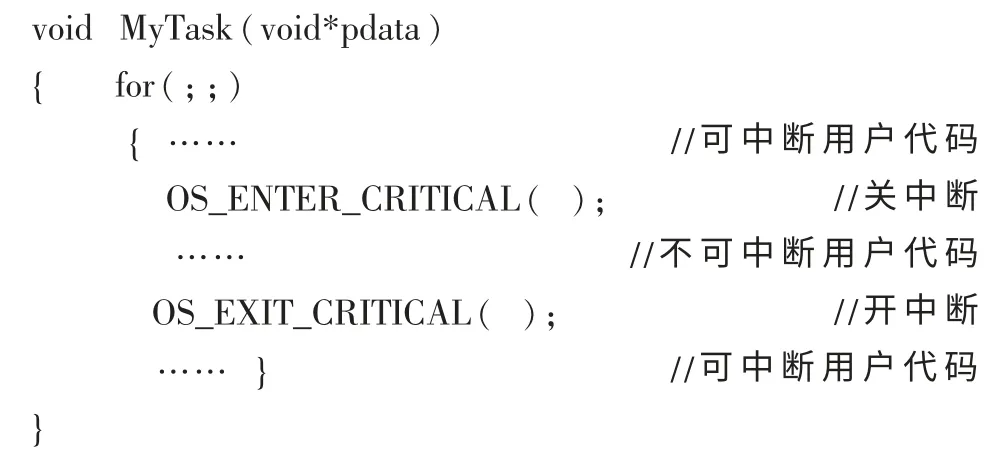

针对不同的功能进行程序设计,从操作系统的角度来讲,就是针对要实现的功能在系统中添加任务,由内核对各个任务进行管理和调度。μC/OS-II中用户任务代码的一般结构如下:

本设计中需要添加的用户任务包括A/D采样与转换控制程序和以太网传输控制程序。用户任务由可中断和不可中断的代码组成,宏定义OS_ENTER_CRITICAL()和OS_EXIT_CRITICAL()控制何时响应中断和何时屏蔽中断[8],可根据需要在用户任务中添加多个不可中断代码段,以实现不同的任务需求。

3.1.1 A/D采样与转换控制程序

A/D采样与转换控制采用了Altera提供的SPI核,与IP核一起提供操作函数alt_avalon_spi_command()。设计直接调用该函数,把它添加至用户代码部分,通过设置不同的参数完成A/D采样控制。

AD7714的所有操作都从写通信寄存器开始,写入通信寄存器的数据决定下一次操作是读或写操作,以及对哪个寄存器进行操作。通信寄存器写操作程序如下:

其中,alt_avalon_spi_command()的参数的含义依次是:SPI_BASE和1用于选择SPI从设备;参数1和writedata分别表示写入数据长度和数据地址;参数0和NULL表示不进行读出操作(如果需要进行读操作,就在这两个参数位置上填写读出数据长度和读出数据存储地址);最后一个参数0表示操作后释放从设备。

写通信寄存器操作完成后即可进行对其他寄存器的操作,如读数据寄存器等,同样使用alt_avalon_spi_command()函数,操作完成后芯片返回到等待对通信寄存器写操作的状态。

3.1.2 以太网传输控制程序

自主设计IP核的软件使用C语言编写完成,程序包括两部分,一是定义IP核内部寄存器映像的C头文件enc28j60_ctrl_ip.h,为操作底层硬件提供符号化常量;另一部分是硬件的驱动程序enc28j60_ctrl_ip.c,提供对硬件底层操作的基本程序。

驱动程序主要是通过对寄存器的操作来实现不同的功能,因此用到Altera提供的寄存器存取函数IOWR()和IORD(),例如对发送数据寄存器TXDATA写操作函数IOWR(enc28j60_ctrl_ip_base,3,data),其中enc28j60_ctrl_ip_base是IP核的基地址,3是发送数据寄存器偏移地址,data是要写入的数据。

以太网控制IP核驱动程序需要结合TCP/IP协议栈才能进行以太网通信操作[9]。设计选用Interniche公司的NicheStack嵌入式TCP/IP协议栈,它具有体积小、易移植等优点[10]。与操作系统的移植相似,Nios II IDE开发环境中提供了NicheStack示例工程,通过添加工程即可实现协议栈移植。

3.2 系统操作流程

系统的主要操作流程如图7所示。当系统上电复位完成后,控制核心先对各芯片进行配置,AD7714芯片的配置从写通信寄存器开始,包括增益设置、信号极性和通道设置等;然后对网卡芯片ENC28J60进行配置,也就是对网卡芯片进行初始化设置,包括接收/发送缓冲器设置、MAC初始化设置和PHY初始化设置等;芯片配置完成之后,系统进入循环接收采样数据状态,系统轮询AD7714的DRDY引脚,当其为低电平时说明产生新的采样数据,则系统读取数据;数据读取完成之后,送至ENC28J60通过以太网发送;数据发送完成之后,系统继续轮询引脚,如此循环。

图7 系统操作流程

通过下载至EP1C12开发板并连接AD7714数据采集板和ENC28J60网络模块对系统进行了实际测试。控制核心工作在50 MHz时钟频率下,AD7714主时钟频率为2.5 MHz,结果显示系统运行良好,数据采集与传输过程稳定。本设计改变了传统动态轨道衡数据采集与传输系统的设计方法,完全采用SoPC设计方法与IP复用技术。数据传输部分使用自主开发的专用IP核,该IP核在软件仿真测试和实际运行测试中都表现良好。整个系统具有灵活方便、易于升级的优点,可以应用于不同的环境。

目前系统的数据处理仍需在上位机完成。下一步将利用FPGA芯片优秀的并行处理能力,把数据处理部分以IP核的形式集成至控制核心,使数据处理IP核经过调整可适应不同的要求,或者设计成针对不同应用的IP核,这样整个系统通过软件编程下载即可实现完全不同的功能,应用前景十分广阔。

[1]KEATING M,BRICAUD P.Reuse methodology manual[M].Berlin:Springer,2002.

[2]Texas Instruments.INA128 data sheet[Z].2005.

[3]Analog Devices.AD780 data sheet[Z].2004.

[4]张文爱,姜敏,赵磊.基于FPGA的动态轨道衡数据采集系统[J].同济大学学报,2010,38(10):1525-1528.

[5]Microchip Technology.ENC28J60 data sheet[Z].2008.

[6]李兰英.Nios II嵌入式软核SoPC设计原理及应用[M].北京: 北京航空航天大学出版社,2006.

[7]Altera Corporation.Avalon interface specifications[Z].2011.

[8]任哲.嵌入式实时操作系统μC/OS-II原理及应用[M].北京:北京航空航天大学出版社,2009.

[9]FALL K R,STEVENS W R.TCP/IP illustrated volume 1:the protocols(2nd edition)[M].Addison-Wesley Educational Publishers Inc,2011.

[10]Altera Corporation.Ethernet and the NicheStack TCP/IP Stack-Nios II edition[Z].2011.