全数字跟踪接收机的设计与实现

施胜浦

(中科院对地观测与数字地球科学中心 北京 101512)

随着软件无线电技术和全数字接收机技术的迅速发展[1],以及现场可编程门阵列FPGA规模的不断壮大,用FPGA实现中频数字跟踪接收机已经成为必然的趋势。本文设计的中频跟踪接收机中包括了A/D变换,数字正交混频以及数字滤波等模块。主要的功能模块分为中频接收模块和误差信号提取模块。

经过测试,系统能够完成单脉冲跟踪体质天线的自动跟踪任务,实现了对中频调幅信号的采样,下变频,解调等功能。系统结构简单,体积小,成本低,有良好的通用性。

1 总体设计

自动跟踪接收系统是遥感卫星地球站的一个组成部分,它接收来自天线的卫星数据信号(和信号)和角度误差信号(差信号)经变频,滤波,放大,检波,解调后向伺服系统提供所需要的角度误差信号,控制天线的方位轴,俯仰轴和方位轴向角度误差小的方向转动,实现对目标的跟踪。

其中中频接收本分完成差信号的幅度检波输出视频信号和信号强度的提取,误差信号提取模块完成角度误差信号的解调,斜率补偿、相位补偿和时分信号的输出。

2 数字中频接收机设计

数字中频接收机包括中频采样、A/D变换、数字AGC、数字下变频、AM检波等。原理框图如图1所示。

图1 数字中频跟踪接收机原理图Fig.1 Digital IF track receiver diagram

中频信号经过一个大动态压控放大器、中频低噪声限幅放大器和一个抗混叠带通滤波器进入A/D采样,采样后的数据进入FPGA计算,输出AGC信号和基带信号进入下一级。数据在FPGA中完成数字下变,CIC抽取滤波,FIR低通滤波,AM检波,数字AGC等计算。

2.1 中频采样和A/D变换

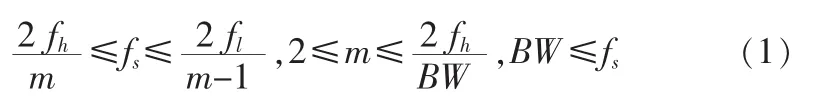

本文提到的中频数字跟踪接收机是70 MHz中频信号输入,信号带宽为12 MHz。输入信号经抗混叠滤波器后,进行A/D采样。采用欠采样的方法来求的适合的采样率[2]。根据通带采样定理,采样率必须满足一下条件:

其中,fs是采样频率,fh、fl分别是信号的上、下限频率,BW=fh-fl是信号带宽,m为正整数,可去的值分别为:2~6。

可见,最低采样率可以取到25.3~25.6之间,但是采样率太低会给滤波器的设计带来难度。最后根据Heisenberg不定性原理来估计采样率与分辨率的关系,以及采样率与分辨率对信噪比,ADC动态范围的影响,计算最佳采样率 (正交采样)[3]选择采样频率fsopt=56 MHz,分辨率为16位。

2.2 数字下变频的实现

用56 MHz的采样频率对70 MHz的信号进行采样,带通采样相当于将信号以56 MHz的间隔进行频谱搬移,所以采样后的信号,只需要下变频14 MHz就可以得到基带信号。采样后的调幅信号与数字本振频率为14 MHz的正余弦信号进行数字混频,产生同相和正交两路基带信号。同相分量中含有基带分量和二次谐波分量,只要通过低通滤波器就可以得到基带分量。正交分量中只包含二次谐波分量,通过低通滤波器可已完全滤除。为了节约系统资源,所以设计NCO只需要产生同相分量。选择固定系数法来产生正弦信号和余弦信号,避免由于相位截短带来的误差。正交本振详细取值如下:

cos(0)=1; cos(0.5π)=0; cos(π)=-1; cos(1.5π)=0;

sin(0)=0; sin(0.5π)=1; sin(π)=0; sin(1.5π)=-1。

本振信号的幅度值只有{0,1,-1},用Verilog编程实现直接与ADC输出相乘实现混频,这种方法实现数字本振信号精度非常高。

数字下变频部分设计的运算都集中在数字滤波部分,为减少运算首先对I、Q信号进行CIC抽取。CIC滤波器是一种基于零极点相抵消的FIR滤波器[4]。本文设计是一个5级级联32倍抽取CIC滤波器,包括5级积分器,10倍抽取器和5级梳状滤波器。它们分别用累加器、序列变换和减法器用Verilog编程实现。

最后通过一个32阶的FIR低通滤波器:通带截止频率为0.6 MHz,阻带起始频率为1.2 MHz。用 MATLAB的Smuilink的数字信号处理工具计算滤波器系数[6]。比较抽取前后的滤波器以及资源占用情况。很明显抽取后的FIR低通滤波器要优于抽取前的,如果要在高采样率下达到抽取后的效果,就需要滤波器有个高的阶数,从而占用更多的资源。

图2 不同采样率下相同阶数FIR滤波器对比图Fig.2 Different sampling rates of the same order of FIR filter comparison diagram

2.3 包络检波

2.4 数字AGC设计

为保证中频接收机中ADC的动态范围和精度,要求AGC的动态范围大,即从可变增益放大器的输出中提取幅度并反馈控制其增益,使输出信号电平基本保持恒定且不溢出。可控增益范围和时间常数是AGC的两个重要指标。由于低轨卫星的发展和天线的单脉冲跟踪体质要求跟踪接收机的动态范围要在70 dB以上,模拟AGC很难达到如此高的要求。本文中要求跟踪接收机采用两级AGC,动态范围在100 dB以上[7],时间常数在100 ms一下可调。设计如图3所示。

图3 数字AGC框图Fig.3 Digital AGC Block diagram

图3是一种数字AGC的方框图,它采用了模拟和数字增益两级A GC控制。接收到的中频信号经电压控制的可控放大器放大进入A/D采样,采样后输入数字信号处理器,经过AGC1系统产生中频放大器控制电压,AGC1的作用是使输入信号的峰-峰值限制在ADC的最大允许电压之内,防止输入采样的ADC溢出。数字放大器的增益由软件AGC2控制,使输出的信号电平恒定。

设AGC1的阈值电压设为E,信号输入值设为x(n)·|x(n)|>E 时,放大倍数 Gn偏大,需减小放大倍数,当|x(n)|<E时,放大倍数 Gn偏小,需增大放大倍数。 如果|x(n)|>E时,则Gn增益在上升时间内应该下降,即降低增益应:ΔG=20(log|x(n)|-logE)dB 因此每一个样点增益应下降 20 (log|x (n)|-logE)/N,其中N与AGC的时间常数有关,N=上升时间(或释放时间)×抽样频率。假设AGC1的总增益控制量为a,单位为dB, 电压变化范围为 b 则有单位为V,则AGC1电压在每一个样点应增加,将(2)式整理,令变量,这是与AGC的时间常数。AGC2的算法与AGC1相似。下图给出了AGC2的算法实现框图如图4所示。

图4 数字AGC原理图Fig.4 Digital AGC diagram

门限判决模块的作用是限制加减计数器控制信号的波动,防止环路振荡。其内部设有2个门限,2个门限之间的范围即为AGC输出信号的波动范围。为了防止AGC发生振荡,该范围应该在满足解调要求的动态范围条件下足够宽,而不是1个恒定不变的电平值。该模块首先对来自包络检波模块的信号进行截位处理,以便与16位门限进行比较,判决过程与外部AGC相似。根据指标要求,数字AGC控制范围为30 dB,系统调整步进量为0.1 dB,所以查找表地址设计为64位即可满足要求。环路增益步进量控制信号是滤波器输出信号电平的非线性函数。假设估计的输入信号电平过低或过高,计数器的步进量按标度给出,以降低AGC的增益调整时间,在这个时间内使信号调整到门限判决模块的两门限之间。步进量设置为非线性,是为了防止当信号接近最佳工作点时发生环路振荡。当信号电平接近最佳电平范围时,增益调整的步进量减小,以确保整个环路的稳定性。

加减计数器模块的作用是根据输入信号与最佳的接收信号之间的差值,对输入信号进行反向补偿。

3 误差信号提取模块设计

误差信号提模块接收跟踪接收机的AGC信号,和视频信号。首先将视频信号解调成方位、俯仰误差信号,将误差电压补偿后,再将AGC和角度误差信号进行编码送给伺服系统。此外误差信号提模块还向馈源输送一个时分开关信号。具体框图如图5所示。

图5 自动跟踪模块原理图Fig.5 Autotrack module diagram

时分解调部分是利用时分信号将视频信号解调出方位误差电压和俯仰误差电压。两路误差信号再进行相位补偿,也就是抵消和差信号相位差或和差馈源中心波束不重合导致的相位误差。最后在进行进行斜率调整,也就是灵敏度调整。系统将两个补偿值存在寄存器中,以便跟踪不同频率目标时调用。

4 硬件设计

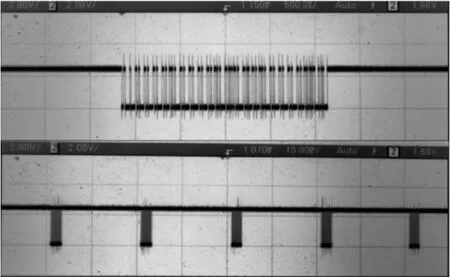

本设计包括数字中频模块、自动跟踪模块、电源保护、接口电路等。其中VGA采用AD8362,中频低噪声放大器采用AD6630、抗混叠滤波器采用.mini-circuits公司的LC型无源带通滤波器,带宽为12 MHz。ADC采用MAX15988、FPGA采用Xilinx公司的Spartan II并采用Verilog语言在ISE 13.0环境下编程。整个系统采用地址总线和数据总线相连,配有高低位的EEPROM、NVRAM和SRAM。电源保护电路采用MAX695。系统的自动跟踪部分增加了模拟中频接收机接口,分别用ADC12062和MAX186将模拟视频信号和模拟AGC信号直接接入自动跟踪模块。输出接口采用DB9接口RS-232和RS-422输出。本文中的设计已经成功的运用在地面站的跟踪系统中,并且性能稳定。下图为输出到伺服系统的编码信号。

图6 输出伺服编码Fig.6 Output servo code

5 结 论

基于软件无线电的全数字跟踪接收机设计采用FPGA为主要器件,实现了系统要求的功能,满足了系统指标。数字信号不存在温漂、增益变化和直流电压偏置,很少需要校准。较模拟跟踪接收机动态范围大,精度高,误差小,而且结构简单、体积小。采用FPGA设计较集成IC灵活性高,成本低。该跟踪接收机适应性强,控制方便,用途非常广泛。

[1]Rohde U L,Whitaker J C.Communications Receivers DSP,Software Radios,and Design (Third Edition)[M].北京:人民邮电出版社,2003.

[2]汪敏,肖斌.基于FPGA的数字中频系统设计[J].通信技术,2011,01(44):29-31.WANG Min,XAO Bin.Design of digital IF system based on FPGA[J].Communications Technology,2011,1(44):29-31.

[3]Pellon L E.A double nyquist digital product detector for quadrature sampling[J].IEEE Transactions on Assp,1992,40(7):1670-1680.

[4]谢白玉,杨士中,张承畅.基于FPGA的CIC滤波器的设计[J].计算机仿真,2009,26(8):323-325.XIE Bai-yu,YANG Shi-zhong,ZHANG Cheng-chang.Design of cascade integrator comb filter based on FPGA[J].Computer Simulation,2009,26(8):323-325.

[5]U.Meyer-Baese著,刘凌 译.数字信号处理的FPGA实现[M].3版.北京:清华大学出版社,2011.

[6]张月红,王马华,朱霞.基于FPGA的FIR数字滤波器的优化设计[J].现代电子技术,2011,34(14):44-46.ZHANG Yue-hong,WANG Ma-hua,ZHU Xia.Optimal design of FIR digital filter based on FPGA[J].Modern Electronics Technique,2011,34(14):44-46.