600MHz CMOS 锁相环频率综合器设计

纪 娜, 何国荣

(杨凌职业技术学院电子信息工程系,陕西杨凌712100)

0 引言

在现代通信系统中,锁相环已经变得无处不在,其广泛用于时钟恢复电路,频率(相位)调制解调电路,频率综合器电路等。尤其是如今通信电路,计算机工作频率[1]越来越高,为消除内部时钟和外部参考时钟的不同步,如为发射器和接收器提供时钟同步,以及产生更高的时钟频率,具有锁相回路结构的频率综合器和时钟同步电路变得日益不可缺少。

利用CMOS工艺设计锁相环电路,加入分频电路,用于频率综合器。电路采用电荷泵锁相环结构,可通过调整MOS管尺寸,来调整电荷泵电流,同时电荷泵结构对外部供电电源波动不敏感,改善了整个环路性能。另外系统片内集成了环路滤波器,减少了系统噪声。

1 锁相环模型

一个典型的电荷泵结构锁相环[2]包括鉴相器、电荷泵、环路滤波、压控振荡器、分频器(可选)这几个模块,线性化的锁相环模型[3]如图1所示。

鉴相器输出可表示为:ud=Kdθe,其中Kd为相位鉴相器增益,θe为相位鉴相器输入信号相位差。

由于电荷泵存在泄漏电流Ileak,会导致相位偏移θε=2π其中,IP为电荷泵输出电流,由此得出电荷泵传输函数:

图1 线性化锁相环模型

设环路滤波器传输函数为F(s),对于不同结构和阶数的环路滤波器有不同的传递函数。

压控振荡器输出信号角频率ω2(t)=ω0+K0uf(t),其中ω0为压控振荡器的中心角频率,K0为压控振荡器的增益,uf(t)为压控振荡器的输入控制电压。这里需要得到输出相位θ2(t)模型的传递函数,由于,θ2(t)=,拉普拉斯变换得压控振荡器传递函数即压控振荡器充当了积分器的作用。

分频器用于将压控振荡器产生信号频率 N分频,同时也可以理解为将压控振荡器产生信号相位除以N,因此分频器在模型中作用就相当于一个增益为1/N的增益模块。

2 电路设计

设计的锁相环基本模块包括图1所示的5个模块:鉴相器,电荷泵,环路滤波,压控振荡器,分频器。

2.1 鉴频鉴相器(PFD)

鉴相器功能是检测两个输入信号相位差,同时产生与相位差大小相关的输出信号。一般常用鉴相器有异或门(XOR),模拟乘法器(Multiplier),鉴频鉴相器(PFD)。设计采用鉴频鉴相器,鉴频鉴相器检测输入参考电压和经环路反馈回来的反馈信号的相位差和频率差,如果这两个信号存在相位差或频率差,鉴频鉴相器会输出“Up”或“Down”信号,以此调节压控振荡器的输出。设计中,由于存在电荷泵的设计,这里的鉴频鉴相器又叫电荷泵鉴频鉴相器(CPPFD)。“Up”信号会通过电荷泵增加环路滤波器电容上电荷量,以此增加压控振荡器的输入控制电压,压控振荡器振荡频率升高;“Down”信号会通过电荷泵减少环路滤波器电容上电荷量,以此减小压控振荡器的输入控制电压,压控振荡器振荡频率降低。压控振荡器输出频率又通过反馈信号影响鉴相器工作,以此构成一个闭环控制系统。

鉴频鉴相器较其他鉴频鉴相器,比如异或门鉴频鉴相器[4](XORPFD),更适合此次整个设计系统的架构。另外,鉴频鉴相器还有占用芯片面积小的优点。

图2 PFD原理图

图3 PFD电路仿真图

PFD原理图如图2所示。PFD原理图设计鉴频鉴相器主要有两个带清零端(高电平有效)的D触发器[5]构成,输入分别为参考输入信号和系统环路反馈信号,输出为“UP”和“Down”信号。此电路输出有4个状态[6]:(1)UP=0,Down=0;(2)UP=1,Down=0;(3)UP=0,Down=1;(4)UP=1,Down=1。其中状态(4)不能维持,因为两个同时为“1”的输出,经过与门,再输入到两个D触发器的清零端,两个输出即变化为“0”。所以上述的状态(1),(2),(3)构成有限状态机,输入频率较高的D触发器输出的高电平维持时间大于输入频率较高的D触发器输出。

PFD电路仿真图如图3所示。电路仿真取Vin相位滞后于参考(反馈)信号Vref,“Down”输出脉冲为两个输入信号相位差,此信号施加于后级电路,使后级电路产生反馈信号“等待”Vin,以缩小二者相位差。反之,“UP”信号作用于后级电路,使后级电路产生反馈信号“追赶”Vin,同样缩小二者相位差。

2.2 电荷泵(Charge-Pump)和环路滤波器(Loop-Filter)

由鉴频鉴相器输出的双路“UP”,“Down”信号[7],需要转变成单端的电压(电流)信号去驱动后级的的环路滤波器。一般采用两种方法实现,一种是三态(tri-state)输出,实现输出的高阻态,低电平,高电平输出。这种电路最大问题是电源电压波动对输出高电平的影响;这里采用第二种方法,电荷泵实现。“Up”信号通过一级反相器电路反相后控制P型MOS管M7的通断。M3,M4,M5,M6,M8构成电流镜电路[4]为电荷泵提供参考电流。电荷泵主要是根据鉴频鉴相器输出的“UP”,“Down”信号,调整后级环路滤波器电容上电荷大小,当输入信号相位领先反馈信号时,“UP”信号高电平维持时间长于“Down”信号,M7导通,电荷泵通过M7给C1充电,增加滤波器电容上电荷,滤波器输出电压增大,驱动后级压控振荡器输出频率增加。反之,减少滤波器电容上电荷,后级压控振荡器输出频率降低。具体实现电路如图4所示。

环路滤波器输出控制压控振荡器所需的电压,对整个锁相环系统起着重要作用,对系统对信号的锁定时间有着直接联系。另外,如果环路滤波器参数选取不正确,系统会对电路小的扰动十分敏感[8]。为补偿前级和后级的信号相位损失,同时由文中第二部分的理论分析可知:后级压控振荡器对系统引入一个极点,本级滤波器也会引入一个极点,使得系统稳定性减低,此处环路滤波器设计成电阻和电容串联形式,增加系统稳定性。为防止电流注入电容引起较大的电压跳跃,同时为有助于减小锁定时间,还需一个与此并联的电容C2,C2取值一般为C1的1/10[9]。当相位差缓慢变化时,电荷泵输出电流线性地对C2,C2充电,起到求均值作用。当相位差变化迅速时,电荷泵只是驱动电阻R,(因为C2容值较小,用来阻止电荷泵电流跳变引起的后级电路的跳变)没有起到求均值作用,可快速影响后级的压控振荡器。但在设计中,若按此值系统会出现不稳定,同时系统锁定时间较长。设计中,两个电容值比较接近。另外电容值的选取还与系统设置的阻尼系数有关系。

图4 电荷泵和环路滤波器原理图

2.3 电流饥饿型压控振荡器(VCO)

压控振荡器产生锁相环系统的输出,设计采用电流饥饿型压控振荡器[10],相比于其他类型的振荡器,电流饥饿型结构最大优点是电路结构无需集成无源器件电容从而节省了面积。M4,M5用作反相器,M3,M6用作电流源,M3,M6构成的电流源控制着流过M4,M5的电流大小,即反相器处于电流饥饿状态。M1,M2端漏电流相等,大小由输入控制电压决定,流过M1,M2的电流在每一级的电流源中被镜像。电路中每级反相器传输延时正比于流过反相器的电流大小,因此可以通过外部控制电压有效的调整反相器传输延时。同时压控振荡器的振荡频率与各级反相器的输入输出总电容直接相关,设计时通过调整晶体管尺寸得到合适的正当频率。类似于多级反相器构成的环形振荡器,电流饥饿型压控振荡器,也需要奇数个反相器电路前后,首尾相连,才能振荡,设计中一共用了5级反相器。压控振荡器输出经过M7,M8构成反相器缓冲输出,调整波形。

N级(奇数)反相器串联振荡频率:FOSC=1/NT;

其中 T=CtVDD/ID为反相器寄生电容充放电所用总时间,Ct为反相器等效输入输出总电容。

图5 压控振荡器原理图

图6 输出频率与控制电压关系

输出频率与控制电压关系如图6所示,输出频率在控制电压约为1V到3V范围内随控制电压线性变化,即此范围内的VCO增益K0为恒定值,其调谐范围为200MHz~700MHz。

2.4 分频器(Divider)

D触发器反相输入端与数据输入端D相连,此时D触发器功能和T触发器输入端接高电平相同,输出即为输入频率的2倍。以此构成方法,后级继续级联,即可形成2,4,8…分频输出。设计中通过4级D触发器的级联构成16分频输出电路。

图7 十六分频电路原理图

图8 分频电路仿真图

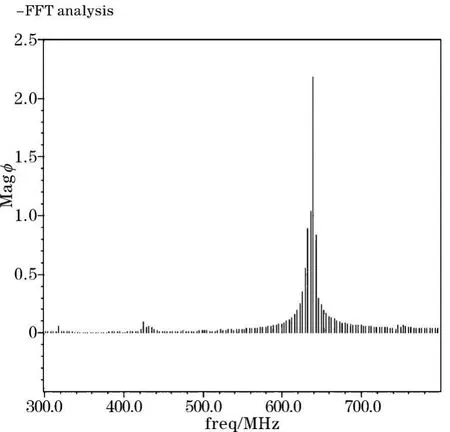

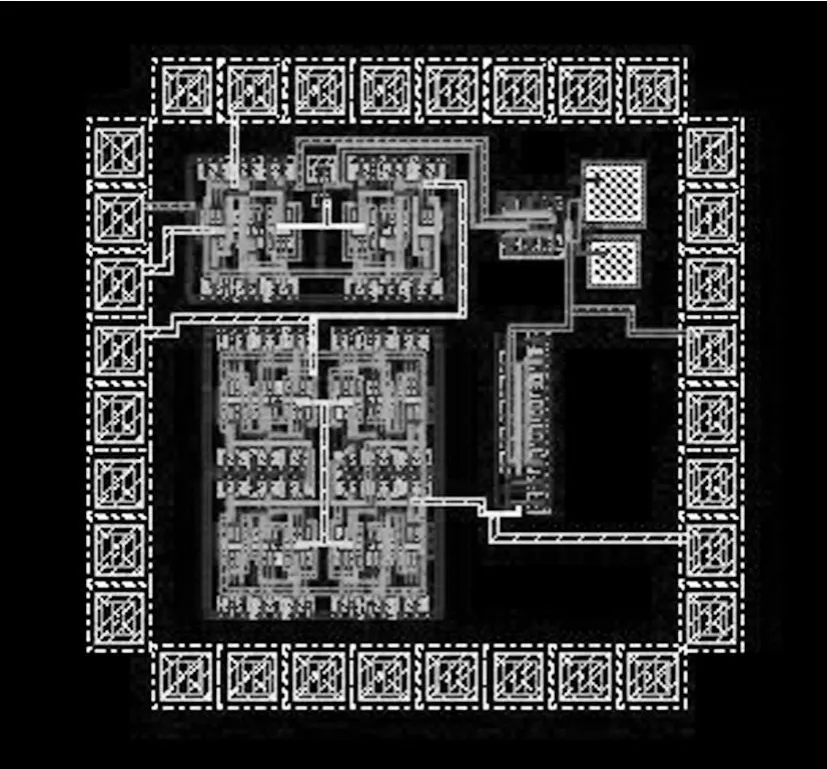

3 锁相环系统仿真

整个锁相环电路设计采用AMI 0.6μ m工艺,仿真工具为Cadence的Spectre,仿真温度设为27℃。电路供电电源电压5V,输入信号40MHz方波。环路滤波器输出仿真如图9,从仿真结果可以看出环路滤波器输出开始阶段出现一段振荡现象,大约 1μ S左右,电路锁定,输出稳定。图10为对VCO输出信号做512点FFT频谱分析,从仿真结果可以看出输入40MHz的信号,与压控振荡器输出16分频比较,锁定状态下,压控振荡器稳定输出640MHz。图11为整个系统的版图设计,版图面积0.26mm×0.26mm。

图9 环路滤波器输出仿真图

图10 640MHzPLL系统输出频谱图

图11 系统版图设计

4 结束语

设计并仿真了600MHz输出的锁相环倍频系统,结果显示系统工作稳定。设计中并没有一味追求先进工艺,在较为普通的工艺条件下,结合系统特性,提出电荷泵结构的锁相环系统,通过合适的电路设计和折衷,同样可以达到较高的性能。当然系统还有较多需要完善的,诸如噪声特性,带宽等。另外还没有经过流片后的测试。

[1] I Young,J Greason,K Wong.PLL clock generator with 5 to 10MHz of lock range for microprocessors[J].IEEE J.Solid-State Circuits,1992,27:1599-1607.

[2] Gardner F M.Charge-pump phase-lock loops[J].IEEE Trans Commun,1980,28(11):1849.

[3] Crawford J A.Frequency synthesizer design handbook[Z].Artech House,Inc.1994.

[4] Behzad Razavi.陈贵灿,程军译.Design of Analog CMOS Integrated Circuits[M].西安:西安交通大学出版社,2003.

[5] Yubtzuan Chen,Chih Ho Tu,Jein WI.A CMOS Phase Frequency Detector with A High Speed Low Power D Type Master Slave Flip-flop[J].45th Midwest Symposium on Circuits and Systems,2002,3:389-392.

[6] Roland E Best.锁相环设计、仿真与应用[M].北京:清华大学出版社,2003.

[7] B Razavi.Monolithic Phase-Locked Loops and Clock Recovery Circuits[J].IEEE Press,1996:1-39.

[8] J F Parker,Daniel Ray.A 1.6 GHzCMOS PLL with on Chip Loop Filter[J].IEEE Journal of Solid State Circuits,1998,33(3):337-343.

[9] Toyama M,Dosho S,Yanagisawa N.A design of a compact 2GHz-PLLwith a new adaptive active loop filter circuit[J].IEEE Symp VLSI Circuits Dig Tech Papers,2003:18.

[10] Jacob Baker.刘艳艳,张为译.CMOS电路设计与仿真[M].北京:人民邮电出版社,2008.