基于千兆以太网的高清电子警察取证系统设计*

何 伟,赵 海,张 玲

(重庆大学通信工程学院,重庆400030)

0 引言

随着CCD制造、图像处理、网络传输等技术的不断发展,数字图像采集系统已广泛应用于交通取证、安防监控等领域。由于传统低分辨率图像质量较差,画面较模糊、细节不够明显常导致违章证据不够充分而给交通民警执法带来争议。高清摄像头记录的交通违章车辆图片清晰直观、违章事实清楚、证据性强,能有效解决这一问题。同时也给图像处理速度和网络传输速率提出了较高的要求,因此,设计了一种基于千兆以太网的高清电子警察取证系统。与传统电子警察取证系统相比具有图片清晰直观、传输快速准确、系统集成度高等优点。

1 高清电子警察取证系统方案

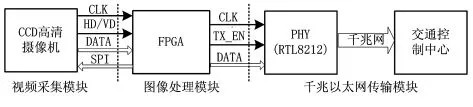

电子警察取证系统主要由视频采集模块、图像处理模块、千兆以太网传输模块三部分组成,系统组成如图1所示。其中高清视频采集模块由ICX274与AD9923A组成;图像处理模块由FPGA实现;千兆物理层芯片采用RTL8212芯片。

图1 系统硬件结构框图Fig 1 Block diagram of system hardware structure

FPGA通过SPI口配置视频采集模块AD9923A的寄存器得到CCD驱动时序,使CCD正常采集图像,经A/D转换后把数据送给图像处理模块;FPGA将采集到的图像进行格式转换、校正、帧打包以及媒体访问协议的实现后将数据送给千兆以太网传输模块;传输模块将数据通过千兆物理层芯片发送到交通控制中心。

2 视频采集模块设计[1,2]

2.1 高清摄像机电路设计

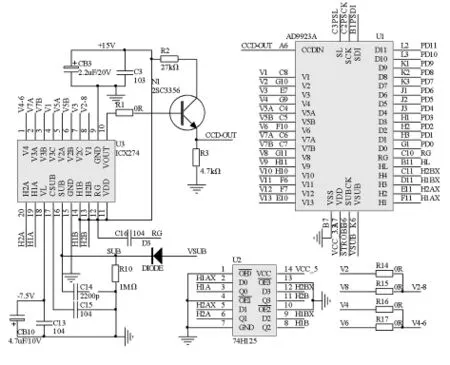

ICX274是SONY公司设计生产的一种200万像素、每秒全像素输出15帧图像的高清CCD图像传感器,常用于安防和交通监控等领域。AD9923A是带有时序控制器、相关双采样、增益放大等功能的模数转换芯片,除了具有精准的模数转换功能之外,还可为CCD提供驱动信号。AD9923A与ICX274组成的高清数字摄像机电路原理图如图2所示。

图2 基于ICX274与AD9923A电路原理图Fig 2 Circuit principle diagram based on ICX274 and AD9923A

图2中,H1A,H1B,H2A,H2B为水平转移控制信号,用来控制各像素点的水平转移。由于CCD水平转移控制信号要求5V的高电平,而AD9923A输出高电平值只有3.3 V,所以,经过升压芯片74F125升压之后连接到ICX274的水平转移管脚。V1,V2,V3,V4,V5A,V5B,V6,V7A,V7B,V8直接连接到ICX274垂直转移管脚,以驱动ICX274的垂直转移时序。VSUB为电子曝光控制信号,RG为电荷清零信号。

ICX274在RG,VSUB,水平转移以及垂直转移信号控制下,依次输出各像素点的电荷,经AD9923A进行相关双采样、增益放大、模数转换后将生成的12bit的数字信号送给数字图像处理单元。

2.2 AD9923A寄存器控制

FPGA通过SPI接口配置AD9923A相关寄存器以实现ICX274时序要求,AD9923A寄存器由12位地址和28位数据组成。当控制信号有效时,时钟信号的上升沿将写入一位数据,每个寄存器要求一次连续写入完整的40位数据,否则,寄存器数据不会更新。

AD9923A与垂直转移时序相关的控制寄存器有:VPAT寄存器组,VSEQ寄存器组,Field寄存器组。VPAT序列由特定的CCD时序决定,在VPAT序列前面加上起始极性、重复次数等就构成了VSEQ序列。根据VPAT序列、VSEQ序列选择不同数目的寄存器组,通过配置相关寄存器组的值,产生所需要的垂直转移信号。系统配置成2个VPAT寄存器组,2个VSEQ寄存器组1个Field寄存器组。

与水平驱动时序控制相关的控制寄存器包括:H1POSLOC,H1NEGLOC,H1H2POL,H3POSLOC,H3NEGLOC,H3H4POL, HLPOSLOC, HLNEGLOC, HLPOL。 其 中H1POSLOC,H3POSLOC,HLPOSLOC 为H1A,H2A,HL 上升沿跳变点位置,H1NEGLOC,H3NEGLOC,HLNEGLOC 为H1A,H2A,HL下降沿跳变点位置,而 H1H2POL,H3H4POL,HLPOL为H1A,H2A,HL信号的起始极性。

3 图像处理模块设计

视频采集模块得到Bayer格式图像只有亮度信息,不利于取证系统的应用,采用FPGA进行图像格式转换和显示校正,使系统能够提供清晰的真彩图像。

3.1 Bayer格式到 RGB 格式转换[3]

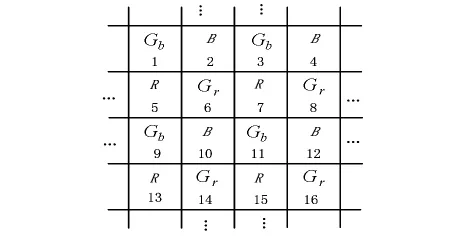

ICX274为Bayer滤色器的彩色面阵CCD,Bayer模式是每一个像素点只包含RGB颜色空间中一种分量,其像素排列方式如图3所示。在Bayer格式图像的每一个像素点中插入另外2种颜色分量,就可以实现黑白图像到彩色图像的转换。采用FPGA实现一种Bayer线性插值算法,实现黑白图像到彩色图像的快速转换。

图3 Bayer色彩滤波模型Fig 3 Bayer color filtering model

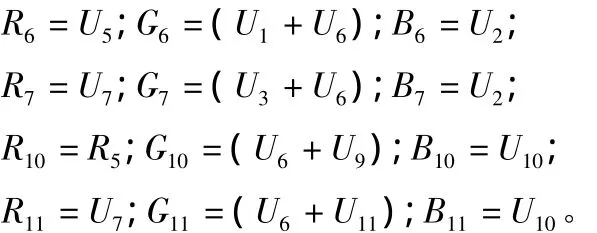

用U1,U2,U3,…,U16表示图3 中各点经模数转换后得到的电压值,并假设6,7,10,11像素点经转换后RGB值分别为R6,G6,B6,R7,G7,B7,R10,G10,B10,R11,G11,B11,Bayer信号到RGB信号转换算法为

3.2 Gamma校正

为了达到较高的显示质量、获得较好的人眼感观效果,显示系统输出与输入应呈线性关系。但常用显示设备的发光器件是阴极射线管(CRT),其输入输出以γ为指数的函数关系:Iv=Cl×,这就造成图像显示失真。因此,需要对原始输入进行预补偿处理,使得显示设备输出与原始输入之间建立线性关系。为原始输入提供一个1/γ的非线性补偿:Iin=。其中,Io为原始输入值,Iin为预补偿后的值。把补偿之后的值Iin送到CRT显示,可得到输出值Iv为:Iv=经这种处理后,显示硬件设备的γ失真相抵消。

经过格式转换后,输出24 bit真彩色图像。计算出从0到255的Gamma校正值,分别得到R,G,B的Gamma校正表。每张表的大小为2 048 bit。将这三张表存储在FPGA的内部RAM中,通过查表的方式实现Gamma校正。

4 千兆以太网传输系统设计[4,5]

经过图像处理模块之后,每秒钟数据量非常大,传统的百兆网络远远不能满足要求,所以,系统采用千兆以太网传输。

4.1 千兆以太网体系结构

千兆以太网对应OSI七层模型中的数据链路层和物理层。数据链路层包括逻辑链路控制(LLC)子层和媒体访问控制(MAC)子层,其中MAC层主要完成数据封装、解封装以及媒体访问管理两大功能;物理层实现数据的收发。为了减少硬件设计上芯片数量、简化连接关系,采用FPGA实现MAC层协议,使用RTL8212实现物理层数据收发。

4.1.1 MAC 层以太网的帧格式

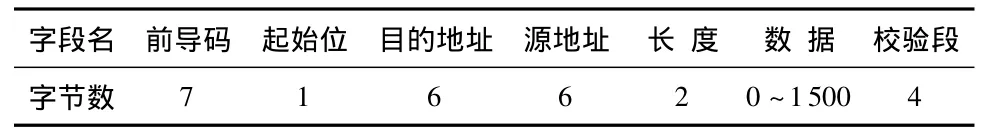

以太网站点发送数据是按以太网帧格式在总线上传输的,将标准的帧格式做一个简化处理,以降低系统复杂度。简化的以太网MAC帧结构如表1所示。

表1 简化的MAC帧格式Tab 1 Simplified MAC frame format

前导码为7字节0x55,使网络两端的物理层达到稳定同步状态;起始位为固定值0xD5,表示帧的开始;目的地址用于识别需要接收帧的站点;源地址用于识别发送帧的站点;长度表示数据的长度;数据表示需要在以太网中发送的数据;校验位由802.3规定的校验公式决定,作用范围从目的地址到数据段。

4.1.2 媒体访问管理

千兆以太网有半双工和全双工2种工作方式,MAC针对不同的工作方式有不同的处理方式。在半双工模式下媒体访问管理模块主要实现CSMA/CD协议,它包含了两方面含义:

1)载波侦听:在MAC子层向物理层传输数据之前,首先对网络进行载波侦听,如果侦听到载波,说明有数据正在传输,本地数据必须在载波消失后还要等待一个时间间隙后才开始发送数据。

2)冲突检测:当2个及以上站点同时向网络发送数据就会有产生冲突。MAC检测到冲突后,站点便向网络发送拥塞序列。如果在发送前导码期间检测到冲突,则将前导码和起始位发送完之后再发送32位的拥塞序列。如果冲突发生在前导码发送完成之后,则站点立即发送32位的拥塞序列。

全双工模式下允许发送站点和接收站点采用点对点的连接,不需要载波侦听和冲突检测,只需要完成数据的封装。

4.2 MAC子层协议的FPGA实现

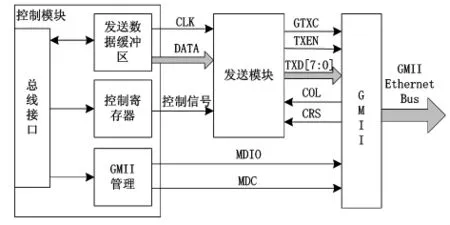

由于系统只需要将采集到的数据发送到交通控制中心,而不接收其他站点数据,所以,MAC子层协议硬件模块由控制模块与发送模块2部分组成。MAC子层实现硬件结构如图4所示。

图4 MAC控制器硬件结构框图Fig 4 Block diagram MAC controller hardware structure

4.2.1 控制模块

控制模块包含总线接口、控制寄存器、发送数据缓冲区、GMII管理4个部分。总线接口部分实现与其他3个模块之间的数据交换;发送数据缓冲区是图像数据与发送模块之间的数据通道,采用FPGA中的FIFO作为缓冲区,通过判断FIFO中存储数据的状态来确定何时开始发送数据;控制寄存器模块主要用于功能参数的设置和状态信息的存储;GMII管理模块实现对物理层的管理。

4.2.2 发送模块

发送模块用于MAC层数据打包和CSMA/CD协议的实现,发送控制状态机是发送模块的核心,使各个功能子模块按照一定的时序协同工作。分为8个状态来完成数据的发送,其状态转移图如图5所示。

1)IDLE:复位状态,系统复位后进入IDLE状态,当数据缓冲区存储了规定的数据后,系统就进入DEFE状态。

2)DEFE:延迟状态,在此状态下,如果没有侦听到载波CS就进入IPG状态,当侦听到载波信号时则放弃本次帧的发送。

3)lPG:帧间隙状态,在半双工模式下达到设定的间隙时间且没有载波信号出现进入PRE状态,在全双工模式下,当计数器计数到设定的帧间隙时间时,进入PRE状态。

4)PRE:前导码状态,当进入PRE后,开始发送前导码。在此期间如果未检测到冲突发生,则进入SDF状态。如果出现冲突,发送完前导码后进入JAM状态。

5)SDF:起始位状态,进入SDF状态后,开始发送起始字符,在此期间如果未检测到冲突发生,则进入DATA状态。如果出现冲突,发送完起始符后进入JAM状态。

6)DATA:数据状态,在Data状态开始发送缓冲区FIFO中的数据,在发送帧过程中未出现冲突,进入CRC状态,如果出现冲突,则进入JAM状态。

7)CRC:帧校验状态,在发送帧校验码后进入DEFE状态,如果出现冲突,则进入发送阻塞码状态JAM。

8)JAM:阻塞状态,发送完四字节的阻塞序列后进入到延时状态DEFE。

5 测试结果

实际测试结果如表2所示。

表2 测试结果Tab 2 Test results

实验表明:设计的千兆以太网系统传输距离远、稳定性高、利用率接近100%。

6 结论

设计的基于千兆以太网电子警察取证系统,有效地解决了高清图像采集、处理与数据的快速传输。经过实际测试,系统每秒可以稳定采集、处理、传输15帧200万像素的图像数据,完全满足电子警察取证系统对图像质量和高传输速率的要求。对于其他的监控系统或传输系统,都有一定的参考价值。

[1]Analog Devices Inc.CCD signal processor with v-driver and precision timing generator:AD9923A[Z].Analog Devices Inc,2006.

[2]莫斯特,吴志红.200万像素数字摄像机设计及关键技术研究[J].光电工程,2009,36(5):117-121.

[3]杨 华,佟首峰.基于FPGA到Bayer到RGB图像格式转换设计[J].现代电子技术,2010,33(2):123-124.

[4]吴俊杰.IEEE802.3以太网MAC控制器的设计[D].南京:东南大学,2008.

[5]郭 俊.以太网媒体访问控制(MAC)及其FPGA实现研究[J].现代电子技术,2008(10):88-90.