基于FPGA的AD转换控制器设计

辛凤艳 孙晓晔

1.河北省科学院应用数学研究所,石家庄 050081;2.石家庄开发区冀科双实科技有限公司

基于FPGA的AD转换控制器设计

辛凤艳1孙晓晔2

1.河北省科学院应用数学研究所,石家庄 050081;2.石家庄开发区冀科双实科技有限公司

采用FPGA 器件EP1C12实现了对A/D转换芯片AD7822的实时采样控制,并将采集的数据暂存到SRAM中以备后续处理。整个设计在QuartusⅡ环境下,采用Verilog HDL语言描述,给出了硬件电路连接、硬件内部逻辑设计以及测试波形,可用于模拟信号的高速实时采集。

FPGA;Verilog HDL;A/D 转换;采样控制

FPGA;Verilog HDL;A/D convertion;Sampling control

引 言

随着现代电子技术的应用和发展,越来越多的电子应用由模拟系统向数字系统转变,而A/D转换器作为模拟系统和数字系统的界面,承担着将模拟信号转变为数字信号的任务,在一些多路信号采集系统和实时数字信号处理系统中,A/D转换的多路扩展、高精度、低成本、实时性显得越来越重要。在一般的信号采集系统中,往往由单片机对A/D转换器进行控制,增加了CPU的负担,降低了CPU的工作效率,大大影响信号采集的实时性。

FPGA的高集成度和高速的特性,使之相对于单片机,更适合于对A/D转换的高速控制,而且还可以把采样数据实时存储。基于此,设计了一种基于FPGA的A/D转换控制器,利用 FPGA 直接控制AD7822芯片对模拟信号进行采样,采集速度可达1MB/s,然后将转换好的8位二进制数据迅速存储到SRAM中,从而提高了采样的实时性、减轻了主CPU的运行负担。

1 AD7822介绍

AD7822是Analog Devices公司推出的一种8-bit A/D转换器。单极性输入,采样分辨率8Bit,并行输出;内含取样保持电路,以及可选择使用内部或外部参考电压源,具有转换后自动Power-Down的模式,电流消耗可降低至5μA以下。转换时间最大为420ns,SNR可达48dB,INL及DNL都在±0.75 LSB以墻。可应用在数据采样、DSP系统及移动通信等场合。

1.1 AD7822的引脚功能VIN1:模拟信号输入端;Vref:参考电压输入输出端,可使用片上参考电压,也可外接参考电压;

CS:片选端,低电平有效;

DB0-DB7:并行数据输出端,一般处于高阻态,当RD和CS变低有效时,数据才被放到数据总线上;

CONVST:逻辑输入信号,在该信号的下降沿(至少保持20ns低电平)启动8-bit模数转换,进入hold模式,转换开始后120ns再次进入track模式。转换结束时检测CONVST信号的状态,若为低,则芯片将power down。

EOC:逻辑输出。该信号表明转换什么时候完成,可在转换完成时用于微控制器的中断信号或将数据锁存到门阵列。

PD:逻辑输入,将该信号拉低可使AD7822处于Power-Down模式,当PD变成高电平时ADC上电。

RD:逻辑输入信号,该信号用于使输出缓冲器退出高阻状态,并驱动数据到数据总线上。只有RD和CS都为逻辑低时数据总线方可使用。

VDD:电源输入端,3V+10%或5V+10%;AGND:模拟地;

DGND:数字地。

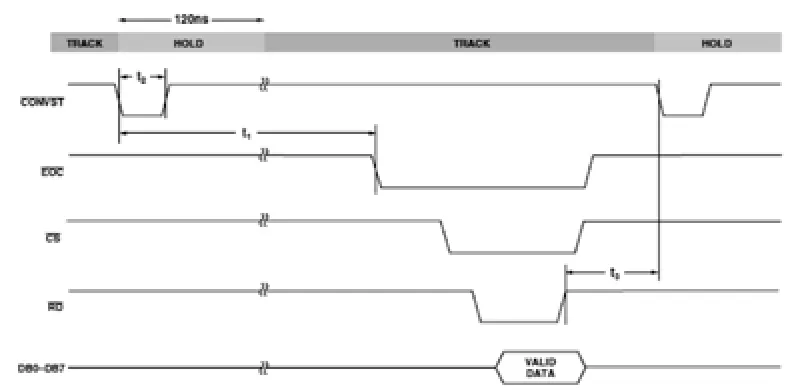

1.2 AD7822的操作模式及转换时序

AD7822有两种可能的操作模式:高速采样模式和自动Power-Down模式。在高速采样模式下,两次转换之间AD7822不会power-down,因此可以达到较高的吞吐率;而在自动Power-Down模式下,转换结束后AD7822会自动power down,这对于功耗敏感的应用比较有利。设计中采用高速采样模式,基本时序如图1所示。

图1 高速采样模式的时序

1.3 AD7822与FPGA的硬件电路图

图2 AD7822与FPGA的电路连接图

如图2所示,在本系统中,AD7822的VDD采用3V电源供电,这样数据总线可以直接与FPGA(FPGA引脚的逻辑电平为3V)连接,无需电平转换。参考电压源Vref为+2.5V,由AD780产生。偏置电压输入引脚Vmid悬空,即Vmid 缺省为1V。这种情况下,AD7822可以处理的模拟信号范围为0~2V,即模拟输入信号经运放处理,转换到0~2V范围内之后,再输入AD7822的VIN1引脚。本文利用Tektronix公司的AWG5012B任意波形发生器产生0~2V的波形信号作为信号源。为避免AD7822因外界干扰进入非法状态或Power down,将AD7822的控制引脚CONVST和PD上拉。

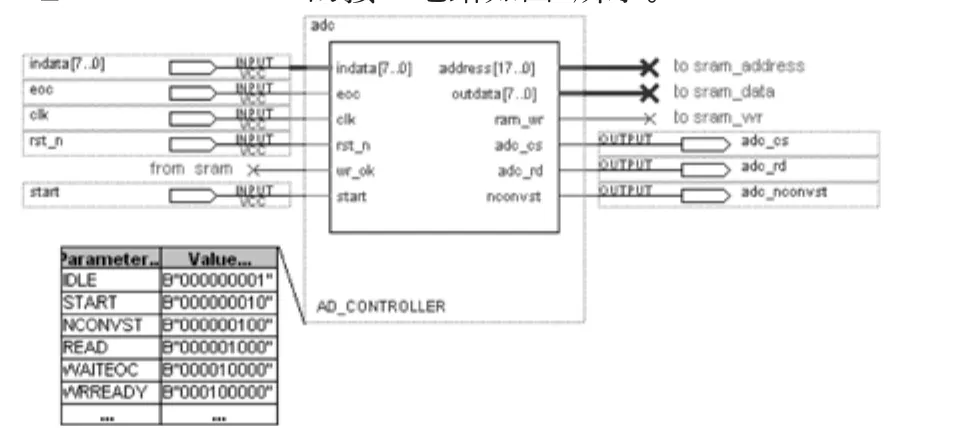

2 AD7822控制器的设计

本设计采用FPGA芯片EP1C12来对AD7822进行采样控制,并将转换得到的数据存储到SRAM中去。用FPGA设计的采样控制器AD_CONTROLLER的接口电路如图3所示。

图3 采样控制器AD_CONTROLLER接口电路图

AD_CONTROLLER的输入时钟clk取50 MHz,在该时钟的作用下,利用有限状态机,控制nconvst、adc_cs、adc_rd信号的状态,从而完成A/D转换及转换结果的存储。start为AD_ CONTROLLER的启动信号,外接按键,当按键PB0按下(start为0)时,AD_CONTROLLER开始工作。indata[7.0]为AD7822的转换结果,当转换完成时,eoc由高电平变为低电平并持续70~110ns,因此,状态机的控制时钟必须小于70ns,否则可能检测不到eoc信号,这里取20ns。要连续采集数据就要不断地用时钟信号触发AD7822的CONVST脚,而FPGA根据AD7822送来的EOC信号不断地读取并将结果送往SRAM存储。A/D转换过程的状态迁移图如下:

图4 状态迁移图

IDLE状态:空闲状态,如果收到来自外部启动A/D转换的信号,则进入START状态。

START状态:控制A/D开始转换,将nconvst置低电平,nconvst为低电平至少保持20ns,才能启动A/D转换。

NCONVST状态:A/D转换保持阶段,nconvst为低电平1个时钟(20ns)之后恢复高电平。

READ状态: convert_end变为低电平(表示A/D转换完成)后,将adc_cs和adc_rd控制信号拉低,读取A/D转换结果。

WAITEOC状态:等待convert_end变高,才将adc_cs和adc_rd拉高,以满足adc_rd为低电平最少保持30ns的时序要求。

WRREADY状态:建立地址和数据信号,准备写SRAM。

WR状态:产生片选和写脉冲。

WAITFOR状态:用于延时。在该状态,用变量j记录时钟数,与参数FMAX共同控制采样频率,保证1us采样一次(参数FMAX取18,即延时18个时钟,该值从调试过程中得到)。

注意:判断A/D转换是否完成取决于信号eoc的状态,但是在图4中,都是通过信号convert_end来判断的。这是由于直接用clk的上升沿对eoc判断决定某些操作是否运行时,会因为clk和eoc两个信号的跳变沿相隔太近而令状态机不能正常工作,因此利用clk的下降沿建立convert_end信号与eoc同步,相位相差180°,然后用clk的上升沿和convert_end信号来判断操作是否进行。

3 仿真

本文利用Tektronix公司的AWG5012B任意波形发生器产生0~2V的波形信号作为信号源,通过BNC接口输出直接与AD7822的模拟信号输入引脚连接,通过Quartus II软件集成的Signal Tap II 嵌入式逻辑分析仪软件对该A/D转换控制模块进行仿真,波形如图5所示,输入信号为50KHz的正弦波。

图5 50KHz的正弦波波形采集仿真

通过波形可观察到,该模块的设计达到了预期目的,可以实现对模拟信号的1us实时采样和模数转换。

4 结语

采用FPGA作为控制器,针对AD7822完成了模拟信号的实时采集与转换处理,充分利用了FPGA高速高效的优势。经仿真,验证该设计运行正常,可以满足信号1us实时采集的需求,并且可以很方便地扩展为更多路的数据采集,能根据不同的应用进行扩展,大大增强了系统应用的灵活性。

[1]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008

[2]户国强,房建东,郭春兰.基于FPGA的A/D转换采样控制模块的设计[J].微计算机信息,2008(7):229~230

[3]黄容兰,万德焕.基于FPGA 的A/D 转换采集控制模块设计[J].数据采集与处理,2009(10):237~240

[4]韦存刚,金星.基于FPGA的多路数据采集和控制模块设计[J].微计算机信息,2008(6):231~232.

[5]AD7822 datasheet [EB/OL]. Analog Devices, Inc, 2001

[6]Cyclone Device Handbook [EB/OL]. Altera Corporation, 2008

[7]AD780 datasheet [EB/OL]. Analog Devices, Inc, 2004

A Design of the A/D Convertion Control Module Based on FPGA

Xin Fengyan1Sun Xiaoye21.Applied Mathematics Institute, HeBei Academy of Science, Shijiazhuang 050081; 2.Shijiazhuang Development Zone Jikeshuangshi Science & Technology Co, Ltd

FPGA device EP1C12 controls AD7822 to collect analog signal and convert into digital signal, then saves the data to SRAM. The whole design is under the Quartus Ⅱ platform, described in the Verilog HDL. The hardware circuit, internal logic design and waveforms are given. It can be used for high-speed real-time acquisition of analog signal.

TP30

A

10.3969/j.issn.1001-8972.2012.05.040