基于Nios II的SOPC系统设计分析

孟 芳,于立佳,张文志

(中国电子科技集团公司第五十四研究所,河北石家庄 050081)

0 引言

SOPC是一种灵活、高效的片上系统解决方案,它将处理器、存储器和I/O口等系统设计所需要的功能模块集成到一个现场可编程逻辑(FPGA)器件上,从而构成一个可编程的片上系统。SOPC技术的实现方式分为基于嵌入式硬核的SOPC系统和基于嵌入式软核的SOPC系统。其中嵌入式软核以其低成本、高灵活性和易于升级等优点获得了诸多设计者的青睐。A1tera公司推出的Nios II就是最具代表性的嵌入式软核处理器。基于Nios II软核的片上可编程系统,配以丰富的集成外设功能特性,用户可以构成各种不同的智能系统,广泛应用于通信、家电和控制等众多领域。

1 系统设计

1.1 系统开发流程

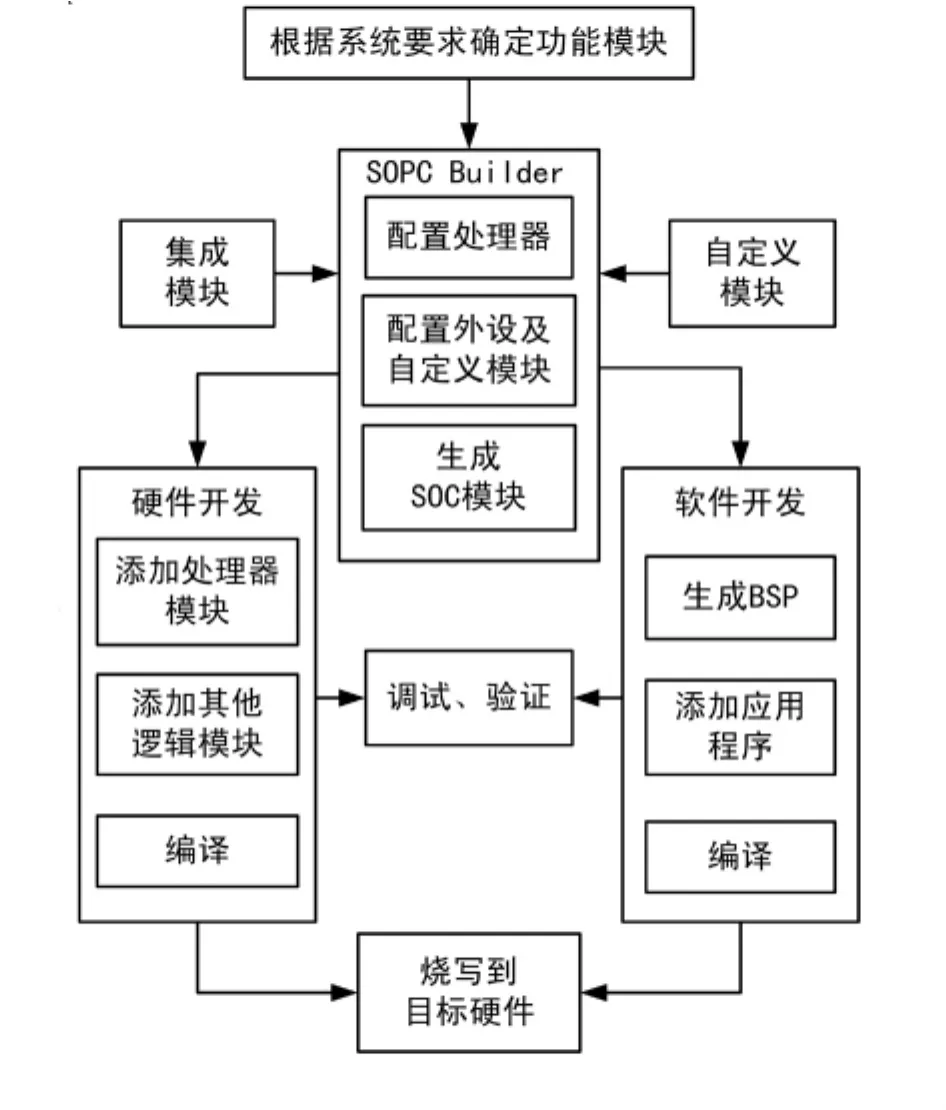

基于Nios II的SOPC系统设计首先要根据系统要求确定功能模块,然后分别进行硬件设计和软件设计,如图1所示。

图1 基于Nios II的SOPC系统开发流程

硬件设计由用户通过SOPC Builder工具软件定制系统硬件,通常采用HDL语言增加其他逻辑模块,通过Quartus II工具软件生成目标代码。软件设计首先根据定制的硬件信息生成与目标硬件相匹配的板级支持包(BSP),通常采用C语言增加应用程序,通过GNU工具链完成编译、连接生成目标文件。然后将软硬件设计结果分别下载到FPGA,进行调试验证。

1.2 设计实例

笔者基于A1tera公司的Cyclone II系列芯片EP2C35完成SOPC系统设计,实现模拟用户单元功能。模拟用户单元是交换机中最常用的接口单元,完成模拟电话、模拟传真等设备的接入,实现3种编解码处理,并具有回波抵消、业务适配及端到端信令处理功能。模拟用户单元组成框图如图2所示,主要包括:FPGA、时钟电路、同步数据随机存储器(SDRAM)、异步串口(UART)电路、模拟用户接口电路、闪存(FLASH)、编解码模块、背板接口电路和电源模块。其中核心部分为FPGA片上系统,下面详细介绍其软硬件设计过程。

图2 模拟用户单元组成框图

1.2.1 硬件设计

硬件设计通过Quartus II 9.1工具软件完成。首先根据系统功能确定片上系统组件:Nios II软核处理器、片内定时器、锁相环、片内存储器RAM、异步串口UART、SDRAM接口、FLASH接口、Avalon三态桥以及CPU接口。

打开Quartus II 9.1软件,建立新工程,启动SOPC Builder工具软件,添加 CPU组件 Nios II Processor,选择 Nios II/f型,时钟为 50 MHz,添加定时器组件,定时周期设为5 ms,为方便调试,添加片内存储器RAM组件、异步串口组件,添加SDRAM接口组件,根据外部SDRAM芯片访问要求设定地址、数据宽度以及访问时序,由于SDRAM的时钟需要固定相位偏移,添加锁相环组件,设定固定偏移相位,添加FLASH接口组件,根据外接FLASH芯片访问要求设定地址、数据宽度以及访问时序,由于FLASH接口必须通过Avalon三态桥连接到总线,添加Avalon三态桥组件,并连接FLASH接口。另外,由于交换矩阵、业务适配及编解码模块需要16位CPU接口,背板接口电路需要8位CPU接口,因此添加自定义组件 CPU接口,选择添加新组件New Component选项,在 Templates菜单栏选择Add Typical Avalon-MM Tristate Slave选项,修改信号定义、类型、宽度及方向等,并设定访问时序,生成自定义组件CPU_16bit和CPU_8bit,添加自定义组件,默认情况下,CPU接口与FLASH接口共享地址和数据总线,为了方便调试,将CPU接口与FLASH接口地址、数据总线分开,增加Avalon三态桥组件与CPU接口连接,至此完成各组件定义。

根据组件定义配置CPU启动和异常处理地址。选择System菜单下Auto-Assign Base Address选项以避免各组件的访问地址冲突,然后生成处理器模块SOC,在工程中添加SOC模块,并将其他常规设计的FPGA内部逻辑模块与之相连,进行编译生成目标文件通过调试接口下载到FPGA进行调试。

1.2.2 软件设计

软件设计采用Nios II 9.1工具软件基于MicroC/OS-II多任务实时操作系统实现。首先获得目标硬件的BSP,SOPC Builder生成硬件CPU模块SOC的同时也生成了 SOC.sopcinf文件,利用SOC.sopcinf可以生成与目标硬件相匹配的BSP文件。打开Nios II 9.1工具软件,新建一个工程,根据Nios II Application and BSP Templates向导选择相应的SOC.sopcinf文件,设定工程、BSP的名称及位置,完成新工程的建立。而后设置BSP属性中Editor选项的各个条目,生成一个用户定制的BSP文件,该BSP与SOPC Builder生成的硬件处理器模块SOC相匹配,其中system.h文件体现了各组件的特性及访问地址。在新工程中添加用户应用程序,MicroC/OS-II多任务实时操作系统提供了任务创建和消息队列创建、处理函数,通过这些函数可以很方便地创建多个任务,并通过消息队列完成任务间通信。软件主程序首先定义任务栈大小,确定任务优先级,完成任务创建、任务编写,然后调用OSStart()系统函数启动任务。用户应用程序添加完毕后编译整个工程即可生成.elf文件,通过选择Debug as Nios II Hardware选项将编译生成的文件下载到FPGA进行软件程序调试。

2 关键技术及优势分析

2.1 关键技术

基于Nios II的SOPC系统关键技术包括以下几个方面:Nios II CPU的内核体系结构、系统总线结构、外围设备设计、操作系统和系统性能优化方法。

2.1.1 Nios II CPU的内核体系结构

Nios II CPU是采用流水线技术和哈佛结构的通用精简指令集计算机(RISC)处理器。其功能单元包括寄存器文件、算术逻辑单元、用户逻辑接口、异常控制器、中断控制器、指令Cache、数据Cache、指令和数据的紧耦合存储器及调试模块。其中算术逻辑单元用来完成数据处理任务,用户逻辑接口可连接用户定制逻辑电路和Nios II内核,由于该处理器采用哈佛结构,因此其数据总线和指令总线分开,紧耦合存储器不仅能改善系统性能,而且可以保证装载和存储指令或数据时间的准确,中断控制器和异常控制器分别用于处理外部硬件中断事件和内核异常事件,Nios II的寄存器文件包括32个通用寄存器和6个控制寄存器,并允许将来添加浮点寄存器,为调试方便,Nios II还集成了一个调试模块。

Nios II CPU支持3种可配置的类型:Nios II/e(经济型)、Nios II/s(标准型)和 Nios II/f(快速型)。其中,Nios II/e消耗的FPGA资源最少,但性能最低;Nios II/f性能最高,但消耗资源最多;Nios II/s介于2者之间。

2.1.2 系统总线结构

在系统总线方面,Nios II采用Avalon交换式总线结构。Avalon总线是Altera公司为SOPC系统开发的一种专用内部连线技术,是一种用于处理器和外设之间的理想的内联总线。它需要极小的FPGA资源,提供完全的同步操作。Avalon总线规范为外设的端口与总线模块之间的数据传输提供了互连模式,它定义了一种可配置的互连策略,允许设计者只保留支持特定的数据传输模式所需要的信号。这种互连策略使设计者在不了解主端口或从端口细节的情况下,可以将任意主设备和从外设互连。Avalon总线同时提供多主机体系结构,可提高系统带宽,消除带宽瓶颈,从而实现无与伦比的系统吞吐量。

2.1.3 外围设备设计

Nios II系统提供一些常用的标准外围设备库。主要包括并行输入输出接口、通用异步收发器、定时器、SDRAM控制器、FLASH控制器以及以太网接口等。设计者能够利用SOPC Builder开发工具来添加所需外设,并配置映像地址、主/从关系和中断优先顺序等。另外,用户还可以添加自定义外设,完成用户需要的特殊功能。

2.1.4 操作系统

Nios II集成开发环境可支持多种嵌入式实时操作系统,包括 MicroC/OS-II、Nucle-us Plus、MicroCLinux、eCOS和KROS等。其中基于抢占式的实时多任务操作系统MicroC/OS-II具有可固化、可剪裁、高稳定性和可靠性的特点,可以提供任务调度以及接口驱动,非常容易使用。Altera提供对MicroC/OS-II的完整支持,使得软件工程师可以快速地为Nios II处理器系统创建一个可裁减的实时操作系统(RTOS)配置。

2.1.5 系统性能优化方法

基于Nios II的软核处理器可以通过定制用户指令、定义基于Avalon总线的用户外设、硬件加速编译器C2H和优化系统编译选项的方法来提高系统性能。定制用户指令可以把一个复杂的标准指令序列简化为一条用硬件实现的单个指令,以减少系统中关键算法的耗时,增强实时处理能力。定义基于Avalon总线的用户外设可以将占用CPU资源较多的处理转化为硬件实现提高系统性能。C2H加速编译器是指可以将C代码中的某些函数通过C2H指令由硬件电路实现,它帮助设计者以最少的资源消耗达到提高性能的目的。另外,通过更改系统参数、优化编译选项,同样能够提高Nios II系统性能。

2.2 优势分析

基于Nios II的SOPC系统与传统的处理器相比,具有以下优势:

(1)易于实现

基于Nios II的SOPC系统提供自动化系统开发工具。它采用一种基于表格的录入系统,具有直观的图形用户界面,系统列出定义的单元模块,并为每个元件提供了一个向导,利用该向导能很容易地定义单元模块功能。

(2)易于升级

传统的处理器的配置是固定不变的,无法适应最新技术的发展,而Nios II嵌入式处理器是基于硬件描述语言构建的,可配置的程度很高,如果用户系统需要进行升级,传统处理器可能需要更换芯片,重新构建硬件系统,而基于Nios II的SOPC系统只需修改FPGA片内的CPU结构配置,简单方便。

(3)节约成本

在系统设计中,除了 CPU模块,一般还需要FPGA完成一些用户逻辑,如果采用SOPC系统即可充分利用FPGA资源,省掉CPU芯片,节约了成本也减小了体积。

(4)缩短开发周期

传统的系统设计需要先建立硬件平台,在硬件平台之上进行软件开发,而Nios II开发环境支持指令集仿真器,允许用户在建好目标硬件平台之前就开始开发程序,可以像真实的目标硬件平台一样开发程序,这样软硬件设计同时进行,缩短开发周期。而且在Nios II硬件系统生成的同时,也生成相应的BSP,即对应于目标硬件系统的底层驱动,这样免去开发底层驱动的麻烦,节省大量的开发时间和精力。

(5)方便调试

传统的CPU模块除了需要专门的开发软件,还需要仿真器并安装相应的软件才能进行调试,而基于Nios II的SOPC系统只需一台装有Nios II集成开发环境的计算机,即可完成软硬件系统的开发调试,非常方便。

3 系统测试结果分析

采用基于SOPC系统设计的模拟用户单元进行系统测试,以验证基于Nios II的SOPC系统功能与性能。将2块模拟用户单元板插入交换机,加电,模拟用户单元正常启动,查询插板信息可以看到2块模拟用户板,将每块模拟板各接出1部模拟话机,在对应的话路注册电话号码,互相拨打,通话正常,设置不同的编解码方式,重新拨打,通话正常,表明基于Nios II的SOPC系统功能正常。

采用斯博伦公司的呼叫模拟测试仪Abacus 100对2块模拟用户板进行16路到16路的呼叫测试,测试时间4 h,呼叫次数为55304次,呼叫完成率100%。通过测试仪的测试以及在工程中的应用表明基于Nios II的SOPC系统工作稳定、可靠。

4 结束语

SOPC技术使开发者能够在软硬件系统的综合与构建2个方面发挥自己的创造力和想象力,从而多角度、多因素和多结构层面对自己的设计进行优化。它更广泛和深入地利用计算机这一科研开发的主流技术,使设计者最大限度地优化系统的性能。基于NiosII的SOPC系统设计简单灵活,开发周期短,成本低,系统维护升级方便,是许多中、低速系统设计不错的选择,今后必将在各个领域得到更广泛的应用。

[1]杨宗德,张兵.uC/OS-II标准教程[M].北京:人民邮电出版社,2009.

[2]侯建军,郭勇.SOPC技术基础教程[M].北京:清华大学出版社,2008.

[3]罗力凡,常春藤.基于VHDL的FPGA开发快速入门·技巧·实例[M].北京:人民邮电出版社,2009.

[4]李兰英.NiosII嵌入式软核 SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[5]杨国林.基于NiosII处理器的SOPC应用平台的研究与应用[D].山东大学硕士学位论文,2008.

[6]杨春玲,张辉.现代可编程逻辑器件及SOPC应用设计[M].哈尔滨:哈尔滨工业大学出版社,2005.