时钟网格与时钟树设计方法对比研究

李春伟

(北京华大九天软件有限公司 北京 100102)

目前芯片性能受片上偏差[1]影响,主要原因为在同一die上atom的数目和位置差异;晶体管channel的长度和宽度差异;氧化层厚度差异;随着工艺日益发展,这种差异对芯片产生的影响越来越明显和严重,传统的OCV derate设计方法也需要越来越严格以确保设计芯片的性能,但是这种严格的约束可能需要损失部分芯片性能作为代价,对于时钟处理方法,传统的时钟树设计方法受OCV影响严重,基于此时钟网格设计的优点就凸显了出来。文中对时钟树设计方法与时钟网格设计方法进行了对比分析验证。

1 时钟网格与时钟树设计方法概述

时钟树综合是ASIC后端设计中的一个重要环节。随着工艺尺寸的不断减小,时钟树综合也给后端设计提出了很多新的问题。特别是进入65 nm及后的40 nm工艺下,时序收敛更加成为了后端设计的主要瓶颈,引起了很多后端设计的关注。时钟树设计中时钟偏移成为限制系统时钟频率的主要因素。

传统的时钟树综合技术是在时钟结构中插入反向器和缓冲器树来达到时钟到达时间的设计要求,这种方法在EDA工具流程中能够被很好的支持和实现,也被广泛采用;时钟网格技术是通过在时钟结构中应用更加相似类型的驱动器实现更低的时钟偏移方法,它的设计方法相对比较复杂,下面将进行详细的对比分析。

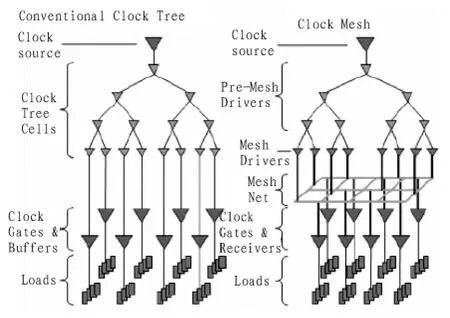

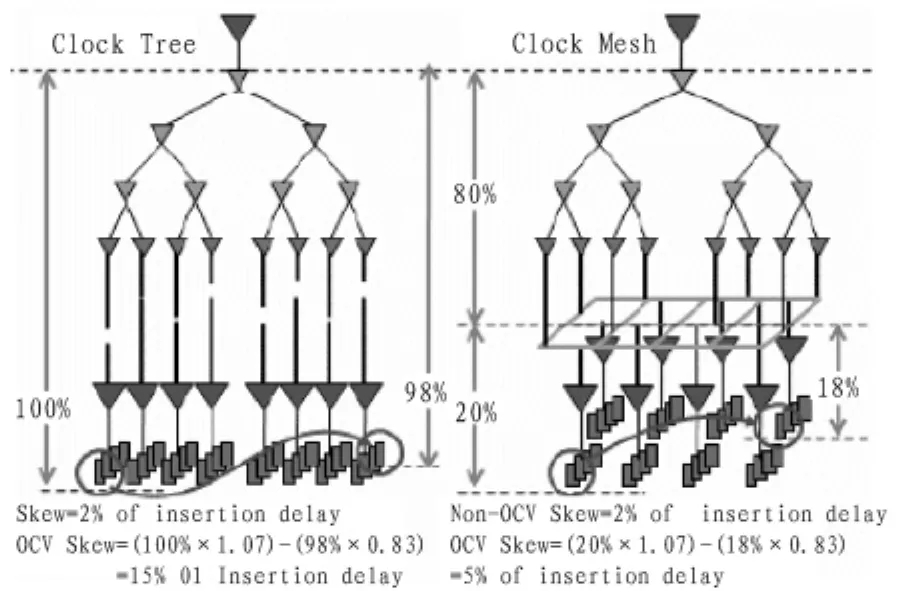

图1为传统时钟树设计与时钟网格设计对比图。

图1 设计结构图Fig.1 Design figure of structure

传统时钟树[2-4]含有时钟源,时钟树单元,门控单元,以及缓冲单元和负载单元;时钟网格结构则包含时钟源,pre-mesh驱动单元,mesh驱动单元,mesh-net,门控以及mesh接收和负载单元。

两种设计方法主要的区别在于时钟网格结构具有meshnet,并且作为多驱动net连接mesh驱动单元,设计结构需要连接一组驱动单元来驱动大规模的RC mesh网络。Mesh-net的主要作用在于平滑不同mesh驱动单元到达它的有效时间,从而为降低时钟偏移时间奠定了良好的基础。

与传统时钟树结构相比,时钟网格[5]设计具有低skew[6],抗OCV影响效果明显的优点,主要应用于高性能芯片产品中,其缺点是功耗比较大,所以设计mesh的挑战就在于如何在降低功耗的基础上获得最低的skew结果,另外时钟网格结构设计起来比较复杂,需要占用更多的布线资源。

时钟网格设计的另一个关键点在于设计结果的仿真分析,与时钟树结构相比其需要利用仿真工具进行仿真结果分析。

2 时钟网格抗OCV分析

第一节已介绍芯片设计中OCV的影响原因分析,下面从时序分析的角度详细阐述对建立时间及保持时间的影响。

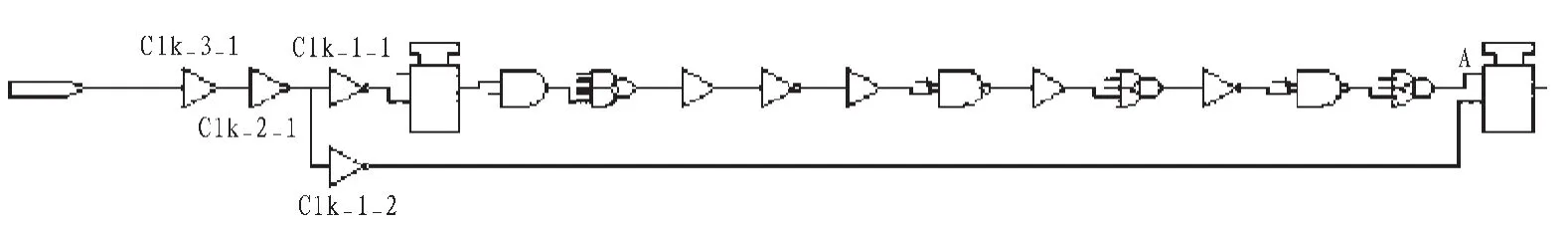

2.1 建立时间

当计算触发器的到达时间(A点),如图2所示,如果时序分析时,不考虑OCV的影响,时钟路径上的时钟驱动器(Clk_1_2)与数据路径上的驱动器(Clk_1_1)在晶片上的距离很远时,就会发生一个潜在的制造性问题,将有可能造成(Clk_1_2)比(Clk_1_1)还早一点到的状况,而这种状况在STA分析时会被忽略,从而造成芯片的潜在性能问题。

图2 建立时间Fig.2 Setup time

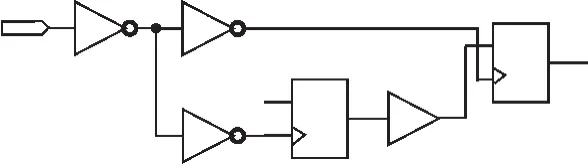

2.2 保持时间

如图3所示,在两个触发器中有一条很短的逻辑路径,与建立时间相似,在分析保持时间时,只考虑到负载与寄生参数,而没有考虑OCV影响,同样会产生时序问题。

图3 保持时间Fig.3 Hold time

从图1可以看出,对于传统时钟树设计方法,从时钟源到负载单元只有很少部分的路径可以共享,而对于时钟网格结构,对于所有的负载单元,从时钟源到mesh net全部是共享路径,只有从mesh net经过门控单元和接收单元到负载单元的路径会受到OCV的影响,而共享部分路径几乎是不受影响的。

依据设计工艺与设计经验,OCV系数从为5%-10%,假设典型值设为7%,对于setup检查,launch路径增加insert delay的 7%,capture路径减少 insert delay的 7%,skew值都假设为insert delay的2%,对于时钟网格结构,一般来讲这个值是很悲观的,在这种情况下,参考图4分析结果,传统时钟树设计受OCV影响为时钟网格受OCV影响的4倍。并且随着设计工艺的不断减小,这种影响会更加显著。

图4 OCV影响对比图Fig.4 OCV contrast figure of influence

3 设计实例分析

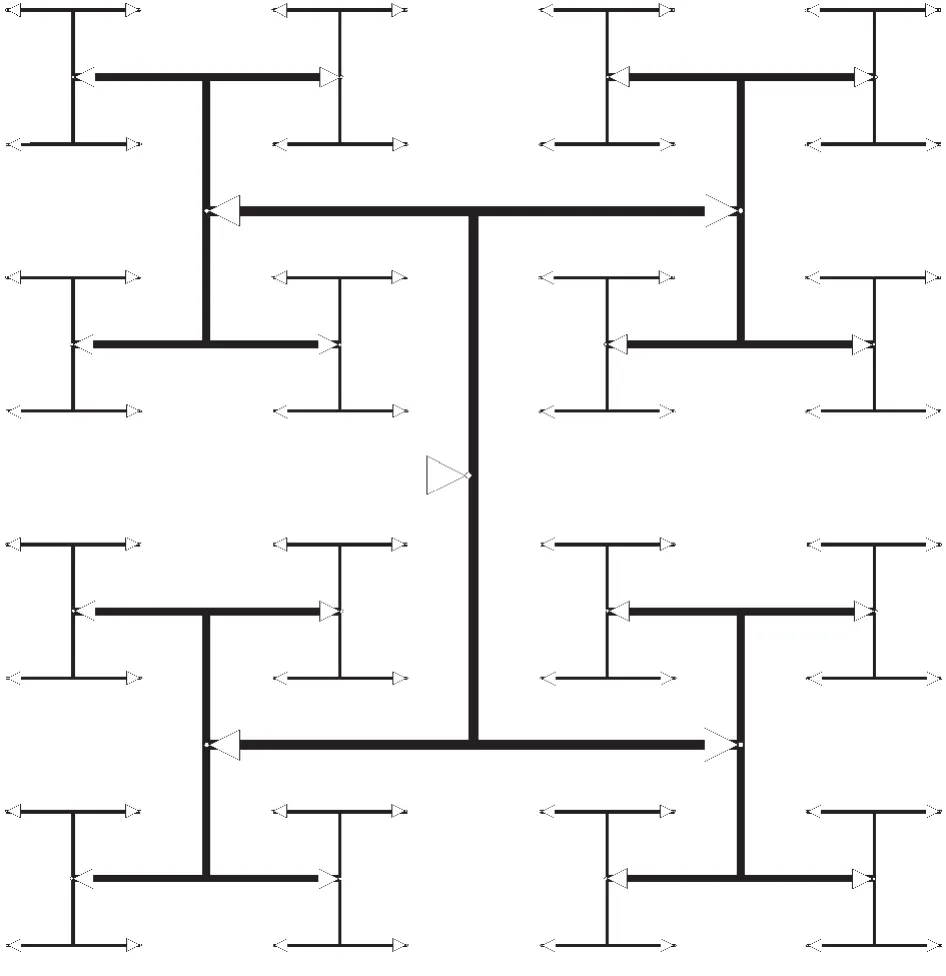

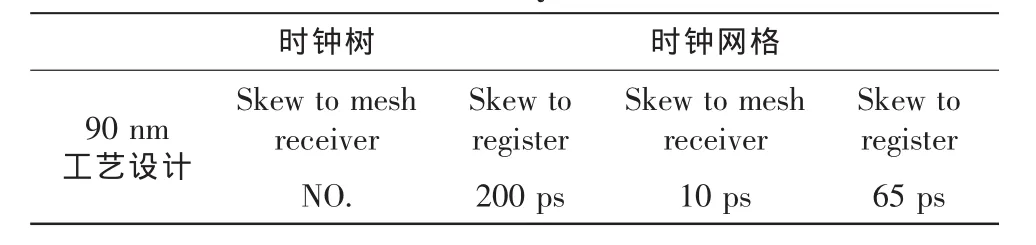

对一90 nm工艺电路进行了时钟网格与时钟树设计方法对比,表1为比较结果,验证了以上分析的正确性。本设计采用两层时钟网格设计,图5为结构示意图。

图5 多级时钟网格结构图Fig.5 Multi-level clock mesh figure of structure

表1 结果分析对比Tab.1 Result analysis and contrast

4 结 论

随着深亚米工艺的不断发展,OCV对芯片性能的影响日益显著,时钟网格设计相对于传统时钟树设计方法,不仅有skew值小,同时更重要的是其抗OCV的影响效果显著。实例分析验证了理论分析的正确性,即时钟网格设计同时保证了芯片设计的性能和稳定性。

[1]Zuchowski P S,Habitz P A,Hayes J D.Process and environmental variation impacts on ASIC timing[C]//Proceedings of the 2004 IEEE/ACM International Conference on Computeraided Design,2004:1-3.

[2]周广,何明华.ASIC后端设计中的时钟树综合[J].现代电子技术,2011(8):2-3.

ZHOU Guang,HE Ming-hua.Clock tree synthesis in ASIC backend design[J].Modern Electronic Technology,2011(8):2-3.

[3]Friedman E G.Clock distribution networks in synchronous digital integrated circuits[J].Proceeding of the IEEE,2001(5):1-3.

[4]千路,林平分.ASIC后端设计中的时钟偏移以及时钟树综合[J].半导体技术,2008(6):1-3.

QIAN Lu,LIN Ping-fen.Clock skew and clock tree synthesis in ASIC backend design[J].Semiconductor Technology,2008(6):1-3.

[5]Wilke G R,Murgai R.Design and analysis of “Tree+Local Meshes”clock architecture[C]//8th International Symposium on Quality Electronic Design,2007:2-4.

[6]Cheung M,Tsou A,CHIU T.Synthesized clock mesh with very small skew[R].Cadence Technology,2007:2-4.