基于DWL概念的嵌入式存储器内建自修复方法★

刘勇锋,姚竹亭,顾秀江,王洁,秦新红

(中北大学 机械工程与自动化学院,山西省太原市 030051)

0 引言

所谓存储器修复技术是指通过在存储器中预置的冗余存储单元,对出现故障的存储单元进行替换的方法。由于冗余单元的划分形式各不相同,可以把嵌入式存储器的修复策略分为3类:基于冗余字的修复、基于冗余列的修复和基于冗余行的修复。在文献中提出了对冗余列分段的软修复方法、二维冗余修复方法、基于冗余字的修复方法,以及同类型的冗余字作为冗余单元替换故障字等等很多方法,但是在实际的开发应用中发现这些设计方法都有各自的优点,但是这些优点都是在不同程度上牺牲了修复率、功耗,以及修复类型,所以针对上述各个问题,本文提出了改进的基于 DWL 修复策略(Divided Word-Line Structure,DWL),这种修复策略是任何冗余单元可以替代检测到的故障单元。

1 存储器内建自修复原理

任何一个完整的存储器内部都由两个部分构成其主要的系统——内建测试(BIST,Built-In Self-Test)和内建冗余分析(BIRA,Built-In Redundancy Analysis)两个部分,而这两部是在整个系统中,在不同的工作模式下工作:测试/修复模式和正常工作模式。当在测试/修复模式下,系统上电启动,BIST模块开始对等待测试的存储器进行测试,在检测到故障后,检测模块会把故障信号Fail给内建冗余模块发送,同时将故障地址送入BIRA模块,BIST模块暂停检测。BIRA模块接收到Fail信号后,对具体故障地址分析,对其地址判断是否已经保存在BIRA内部存储,如果未存储,则在BIRA内部存储器的最末端保留该地址,并进行冗余分配,修复完成之后启动BIST继续进行测试;如果已经把该故障地址保存,则继续进行BIST。在正常工作模式下,BIST电路处于不工作状态,要访问的地址直接被送到BIRA模块中,由BIRA模块判断是否是故障地址,如果是则进行地址重映射,调用冗余存储单元,如果不是则直接访问正常存储单元。

2 SRAM内建自修复电路设计

2.1 改进内建修复电路的策略

本文针对静态随机读写存储器(static random access memory,SRAM)内建自修复电路的研究,一般SRAM的存储单元阵列是采用6管结构,其结构模型如图1所示。

图1 SRAM的存储单元结构图

行冗余、列冗余和块冗余是最常用的冗余单元类型。基于冗余单位修复策略就是对存储器中故障单元所在的整行、列或块被一个冗余行、列或块所代替。虽然对冗余资源的配置有很多算法,但是在故障修复效率的提高上,还是主要依靠冗余配置分析算法和冗余资源的类型、数量、修复策略。

在电路设计自修复的过程中,对电路的故障的修复率、算法的复杂度、性能的影响等指标基本上不会有太多考虑。就拿二维冗余结构修复存储器来说,最优的配置分析问题是一个NP完全性问题已被证明。在采用二维冗余修复方案的行块和列块结构,尽管故障的修复率提高了,但是它的算法的复杂度比较大,使得系统的稳定性和可靠性降低。在研究中发现,如果采用一维冗余结构修复算法进行故障修复的话,实现起来比较简单而且直接、对系统的稳定性影响不太大,然而在面对整行的或整列的修复,这种方案的故障修复率明显较低。为此,要寻找到了一种新型的冗余,所以提出了基于冗余行块的修复策略,尽管它能够很好地解决修复电路的面积开销问题,但它的故障修复率仍然不高。

对上述问题的研究后,改进冗余行块的修复策略的做法是可行的,改进后不仅弥补了在一维冗余修复策略中出现的修复率低的缺点,同时也继承了一维冗余修复策略大的优点。改进了的DWL修复策略,可以替代检测到的任何故障单元。如果在检测到的故障单元,而在行组(row bank)中没有可利用的冗余行块时,行组地址会自动加1,用同样的方式去判断行组里是否能找到可利用的冗余块,如果有则被用来修复故障单元,如果没有,行组地址还会继续自动加1,直到在行组块中找不到任何可利用的冗余块,再在容错系统的报告中显示存储器无法修复。改进的基于DWL的替代方法硬件部分包括4根行组选线(rbs0~rbs3)和16根行选线(W0~W15),32根位选线,还有就是,其中有两个冗余行,换句话说就是8个冗余行块,如图2所示,在下面的6个故障行块中,故障部分(主存中的阴影部分)都成功被冗余行块所替代。显然,改进后的DWL修复策略的替代方法使得故障修复率大大提升。

比如,用户访问存储器时,内建自修复模块会对输入地址首先判断该存储单元是否为故障单元,如果是则该地址直接被输入到CAM中,而相应被冗余块所替代的故障单元的也就是由冗余块输出,所以,修复后的存储使得用户访问是冗余存储区的读写操作。

图2 故障行块被冗余行块所替代

2.2 静态存储器(SRAM)内建自修复电路结构

任何一个存储器的自修复系统设计在其内部都包括内建自修复模块和内建自测试两部分的内容。其实,修复模块是在自建测试电路的基础上建立的,当然,存储器要做到自修复必须加入一些冗余行,这样就使得主存储器与冗余存储区之间构成了DWL结构的硬件组成,从而完成了总体存储器的自修复系统电路的设计,同时这个电路具有了在线测试和离线修复存储器的功能。若用户访问存储器时,内建自修复模块会对输入地址首先判断该存储单元是否为故障单元,如果是则该地址直接被输入到CAM中,而相应被冗余块所替代的故障单元的也就是由冗余块输出,所以,修复后的存储使得用户访问是冗余存储区的读写操作,从可靠性的角度来说是一种很不错的方法。

图3中主要控制信号的含义描述如下:

(1) 在测试/修复模式下,ADDR表示MBIST检测到的故障单元地址。在用户模式下,ADDR表示用户访问主存储器的存储单元的地址。

(2)在用户访问模式下,对于HIT信号,作为一个判断的访问地址是否为故障地址,当HIT=1时,访问的地址ADDR是故障地址,如果用户要对该故障单元进行读写操作,那么用户最后访问的是替代了的冗余块,而不是故障单元,与此同时,NF_ROW和NF_BANK会被设置为高阻态,CAM模块输出的故障单元的重映射冗余单元地址是S_BANK和S_ADDR。在测试/修复模式下,HIT=1时,表示故障存储单元对应的ROW_ADDR和ROW_BANK已经检测出来其存在故障,此时F_ROW和F_BANK置为高阻态,以及CAM模块不分配任何冗余单元;HIT=0时,表示该故障单元是首次被检测到,则需要CAM模块通过分配一个冗余存储单元重映射该故障单元。

图3 SRAM存储器的MBISR系统结构

(3)片选信号CS,是当用户访问存储器时,它决定用户访问的是主存储器还是冗余块。当CS=0时,用户访问主存储器,反之,就访问冗余存储区。CS的电平值总是与HIT的电平值相反。

(4) MBIST控制器的输出信号是TEST_STOP,当TEST_STOP=1时表示内建自测试过程结束,随之自启动MBISR的模块,同时会设置REPAIR_START=1。

(5)当存储器被成功修复之后,RP_FINISH=1,同时会设置RP_FAIL=1。

其中按内容寻址存储器(content address memory,CAM)和故障位图是在一个模块中设计实现的。故障位图是采用16×4的二维数组设计的,在设计中数组的个数正好要等于主存储器的块数。当故障比较器的输出结果为高电平时,则可以判定输入存储单元是故障单元,此故障单元的行组地址和行地址分别被转换成十进制数,与之相对应的数组内容就会被标记为1。在修复过程中MBIRA模块检查故障位图中的每个数组单元的值,如果数组等于1,则根据修复策略而分配一个冗余单元来修复这个故障单元。

2.3 实验结果分析

2.3.1 实验平台

对于本文所述的设计方法,在以Xilinx的Vetex2的FPGA为硬件的平台上,通过软件仿真的方式验证存储器内建自修复的功能特性。首先,采用FPGA的硬件描述语言VHDL编码,之后采用Xilinx ISE集成的综合工具XST和布局布线工具进行综合与布局布线。本文仿真工具采用的是ModelSim SE6.0a,静态时序分析工具采用的是 Xilinx 的 Timing Analyzer。

2.3.2 仿真结果分析

通过对16×32bite的SRAM内建自修复系统电路的实验,验证了改进的基于一维DWL修复策略的可行性和较高的故障修复率,本文中所有仿真结果的数据采用的都是十六进制表示。

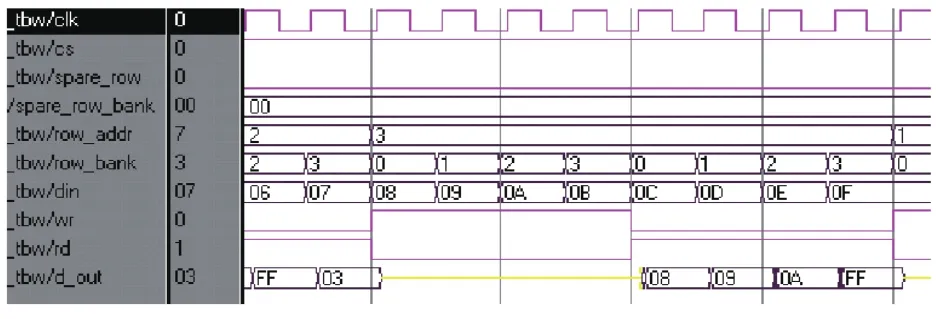

(1)基于编码方式的SRAM随机存储器的时序仿真结果,使用的存储器是可读可写的SRAM随机存储器,其中包括16×32bite主存储器以及两行冗余存储区两部分;与之相对应的地址宽度分别是6位和3位,其中主存储器的行组地址ROW_BANK宽度为2位,行地址ROW_ADDR宽度为4位,冗余存储区冗余行组地址SPARE_ROW_BANK宽度为2位,冗余行地址SPARE_ROW宽度为1位。SRAM随机存储器的I/O信号分别各有5个。MBISR模块输出控制存储器的信号是由片选信号CS控制,在片选信号CS=1,主存储器可以被随机访问,片选信号CS=1时,被访问的是冗余存储区。编码方式的仿真结果由图4所示。

图4 基于编码方式的SRAM的时序仿真结果

WR和RD信号是对SRAM存储器的IO控制信号,都是高有效。通过仿真结果可以看到访问存储器的地址包括两部分:行地址(row_addr)和行组地址(row_bank)。

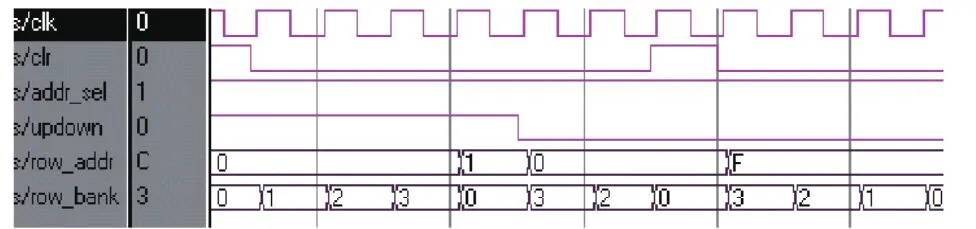

(2)地址生成器的时序仿真

图5所示的是基于可逆二进制计数器设计的地址生成器的时序仿真结果。地址序列的变化规则是按照二进制的递增或递减的形式变化的,即从“00000000B”到“11111111B”或者是从“11111111B”到“00000000B”。高4位代表行地址,低2位代表行组地址。

图5 地址生成器的时序仿真图

选择信号ADDR_SEL=1时,地址序列发生变化,反之保持不变。当ADDR_SEL=1,UPDOWN=1(UPDOWN=0)控制地址的变化移动方向。ADDR_SEL和UPDOWN是由MBIST控制器控制输出到地址生成器的信号。从仿真结果可以得出信号ROW_ADDR代表访问存储器的行地址选线和信号ROW_BANK代表行组地址选线,由此可知,此地址发生器能正确生成需要的地址。

(3) 地址生成器和MBIST控制器连接后的时序仿真

图6所示的是MBIST控制器控制着R/W存储器的控制信号、地址生成器输出访问存储器地址以及整个测试电路的同步时序。MBIST控制器中的↑(r0,w1,r1)和↕(w0)部分march元素连接地址生成器的仿真结果。

图6 MBIST控制器和地址生成器连接后的部分时序仿真

从仿真结果可以看到MBIST控制器能够正确地控制地址生成器的时序和March C+算法中的march元素,以完成存储器的检测。

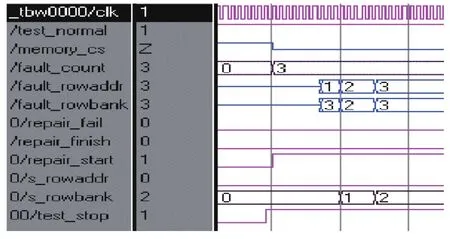

(4)存储器自修复系统电路修复结果的时序仿真

当MBIST检测到故障单元时,会立即把故障地址写入到故障位图。同时MBIST模块在完成测试后,会将test_stop信号输出置为1,同时repair_start自动置1表示MBISR模块的启动。

图7 存储器的内建自修复仿真波形

从仿真波形图7得出,故障信号fault_count输出值为3(MBIST检测到有3个故障发生)。经过MBIRA分析,判断检测到的故障存储器是否可修复,当确定可修复时,信号repair_fail将置0。在故障修复过程中,故障图中记录的故障存储单元的地址是fault_bankaddr和fault_rowaddr。冗余单元的地址信号s_rowbank(两位)和s_rowaddr(1位)是CAM完成把判断检测到的故障单元的地址重映射到冗余单元的地址。从仿真结果可以看出,本文的改进DWL的修复算法能够很好地完成存储器的自修复。

(5)用户访问修复后存储器的仿真

通过改进存储器的故障检测和修复,就是提高存储器的可靠性以及电路性,从而使用户能正常访问此存储器。图8所示的是用户访问存储器阵列后的时序仿真结果。

图8 访问修复后存储器的仿真波形

当用户访问到故障单元时,CAM模块就会自动被“击中”,信号hit变为高(信号hit为高时表示访问的是故障单元)、片选信号memory_cs被置‘0’,而且访问故障单元(地址信号fault_rowaddr和fault_rowbank表示故障单元地址)被转换到访问冗余单元。但当用户的访问地址被判断为无故障单元地址时,hit被置为低且片选信号memory_cs被置‘1’,直接访问主存储器。从图8可以看出完成自修复后,该故障存储器能被正常访问,即对故障单元“13”、“22”、“33”的操作结果(即“07H”、“02H”、“07H”)完全正确,从而提高了该故障存储器的可靠性和稳定性。用户对其它无故障存储单元地址(“nf_rowaddr”和“nf_rowbank”)的访问为正常存取操作主存储器。从仿真结果可以看出对存储器的部分存储单元(包括故障单元)写入访问数据(n_din)时,读出结果(d_out)完全正确。

以下对实验结果进行分析:

(1)MBIST模块和CAM模块的面积开销评估

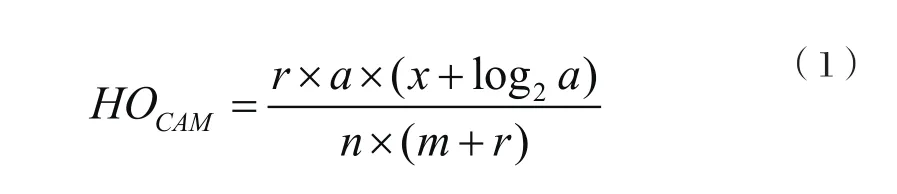

通过对电路的面积开销、故障覆盖率、对存储器的性能影响、故障修复率等的分析,才能做出一个比较全面的评价。在对MBIST模块的面积开销是根据实验平台所采用的集成的综合工具XST统计实现MBIST电路所使用的等效与非门的个数和实现存储器电路使用的等效与非门个数之比。其中的CAM模块是基于SRAM存储器设计的,目前一个标准的SRAM单元需要用6个晶体管,通过CAM模块与主存储器的容量之比就可以得到CAM模块的面积开销,计算公式为:

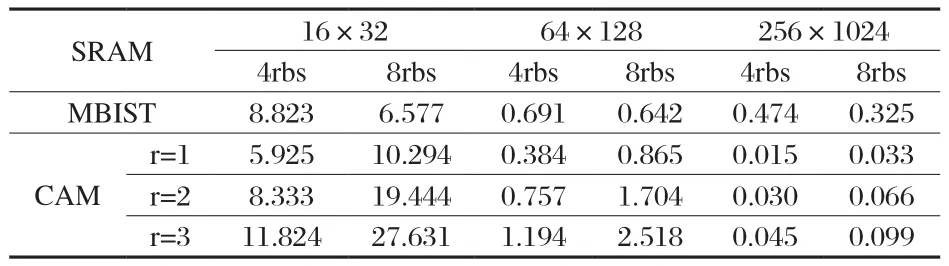

式(1)中的m,n是主存储器的行数和列数,x是主存储器的行地址的宽度,a是整个存储器的行组个数,r是冗余存储区的冗余行数。MBIST电路和MBISR中的CAM模块的面积开销(HO单位:%)如表1所示(其中rbs表示整个存储器行组选线个数或行组的个数)。

表1 MBIST和CAM模块的面积开销

从仿真结果分析可知:

第一,要设计大容量的SRAM可以通过设计MBIST电路和基于一维DWL的改进的自修复算法来实现。

第二,存储器的行组数与存储器的面积开销是成正比的,所以增加行组书就增加了存储器的面积开销,但是会提高故障修复率。所以本测试的方法,在大容量的SRAM存储器中仿真效果会更加明显。

(2)不同容量大小存储器的各项重要指标比较

通过测试电路的最大工作频率、测试电路的最大组合路径延迟、最小周期、4输入LUT数目、SLICE寄存器数目、测试电路的综合SLICE数目等重要指标才能对不懂容量的存储器的BIST电路作出更准确的比较。表2给出了设计的SRAM存储器自测试电路的最大工作频率可达到282.366 MHz。当然,存储器的容量会影响到测试电路占有的SLICE数量与最大组合路径延迟存,主要表现为储器容量增加,存储器的内建自测试电路也会增加,同时最大组合路径延迟也增加,但不会影响最小周期以及最大工作频率。

表2 不同容量大小的MBIST的各项技术指标

在实验中,被注入故障的存储单元大约有0.58%,经过修复后电路能够正常工作,实验结果表明了改进的修复策略已经修复了所有的故障存储单元,使得存储器提高了电路的可靠性。在自修复的过程中,中断修复进程的访问不会对存储器的性能产生多少影响。

3 结论

本文主要研究了SRAM存储器的改进的DWL 修复策略,在存储器设计中,内建自修复结构是降低测试、制造成本、提高成品率的有效方法。但是在这个设计方案中没有考虑地址重构的延时问题,因此,在将来的内建自修复结构中时延的设计考虑是一个新的突破口。

[1]Zorian Y,Shoukourian S.Embedded memory test and repair: infrastructure IP for SoC yield[J].IEEE Design&Test of Computer,May 2003,20(3):58-66.

[2]雷绍充,邵志标,梁峰.VLSI测试方法学和可测性设计[M].北京:电子工业出版社,2005:253-254,191-192.

[3]陆思安,何乐年,沈海斌.嵌入式存储器内建自测试的原理及实现[J].固体电子学研究与进展,2004,24(2):205-208.

[4]吴志伟,邹雪城,雷鑑铭,刘勇.嵌入式存储器的内建自修复设计[J].微电子学与计算机,2007(02).

[5]江建慧,朱为国.嵌入式存储器的内建自测试和内建自修复[J].同济大学学报:自然科学版,2004(08).

[6]梁华国,蒋翠云.使用双重种子压缩的混合模式自测试[J].计算机研究与发展,2004(01).

[7]陆思安,何乐年,沈海斌,严晓浪.嵌入式存储器内建自测试的原理及实现[J].固体电子学研究与进展,2004(02).

[8]檀彦卓,徐勇军,韩银和,李华伟,李晓维.面向存储器核的内建自测试[J];计算机工程与科学,2005(04).

[9]林晓伟,郑学仁,刘汉华,闾晓晨,万艳.嵌入式存储器的内建自测试算法及测试验证[J].中国集成电路,2006(02).

[10]David Janas.下一代手机设计中的嵌入式存储器[J].电子产品世界,2006(10).

[11]Y Zorian,S Shoukourian.Embedded-Memory test and repair:infrastructure IP for SoCyield[J].IEEE Design&Test of Computers,2003,20(3):58-66.

[12]Rajsuman R.Design and test of large embedded memories:an overview[J].IEEE Design&Test of Computers,2001,18(3):16-27.

[13]B Lu S K.uilt-in self-repair techniques for embedded RAMs[J].IEEE Computers andDigital Techniques,2003,150(4):201-208.

[14]J F Li,J C Yeh,R.F Huang,et al,A built-in self-repair design for RAMs with2-D redundancy[J].IEEE Transaction on VLSI Systems,2005,13(6):742-745.

[15]Goor van de,A J,Hamdioui,Fault models and tests for two-port memory[J].Proceedings 16th IEEE VLSI Test Symposium,Washington DC USA,1998:401-410.

[16]Hamdioui S,Al-Ars Z,van de Goor,et al,Testing static and dynamic faultsin random access memories[J].Proceedings 20th IEEE VLSI Test Symposium,2002.(VTS2002),Monterey California USA,2002:395-400.