Teradyne Ultra FLEX的测试程序调试

张 磊,张振华,杨纯辉

(1.中国电子科技集团公司第四十七研究所,沈阳 110032;2.空军驻辽宁地区军事代表室,沈阳 110034)

1 引言

随着大规模集成电路测试系统的出现,被广泛应用在芯片测试领域,实现了高效率的集成电路产品验证。Teradyne Ultra FLEX机台是当今世界较为先进的大规模集成电路测试系统,我们以ATMEL公司的AT89S52芯片为例介绍在此机台上的测试程序开发流程。

2 Ultra FLEX测试系统的硬件配置

Ultra FLEX机台数字子系统有1024个测试管脚,数据速率 800Mbps/1000Mbps,时钟频率400MHz/500MHz,边沿定位精度 ±80ps/±150ps,数据存贮深度256M,子程序存贮深度4K,向量定序存贮深度1M;PPMU每个管脚测量单元:V/I源和测量-1V~6V±50mA,每板64个精密时间测试单元,带宽1GHz;交流子系统包括BBAC高精度宽带交流源,Turbo AC高精度宽带交流源,VHFAC高频交流源,AWG6G微波信号源;直流子系统包括小功率源DC30,中功率源DC75,大功率源HEC Vs。

3 AT89S52电路特点

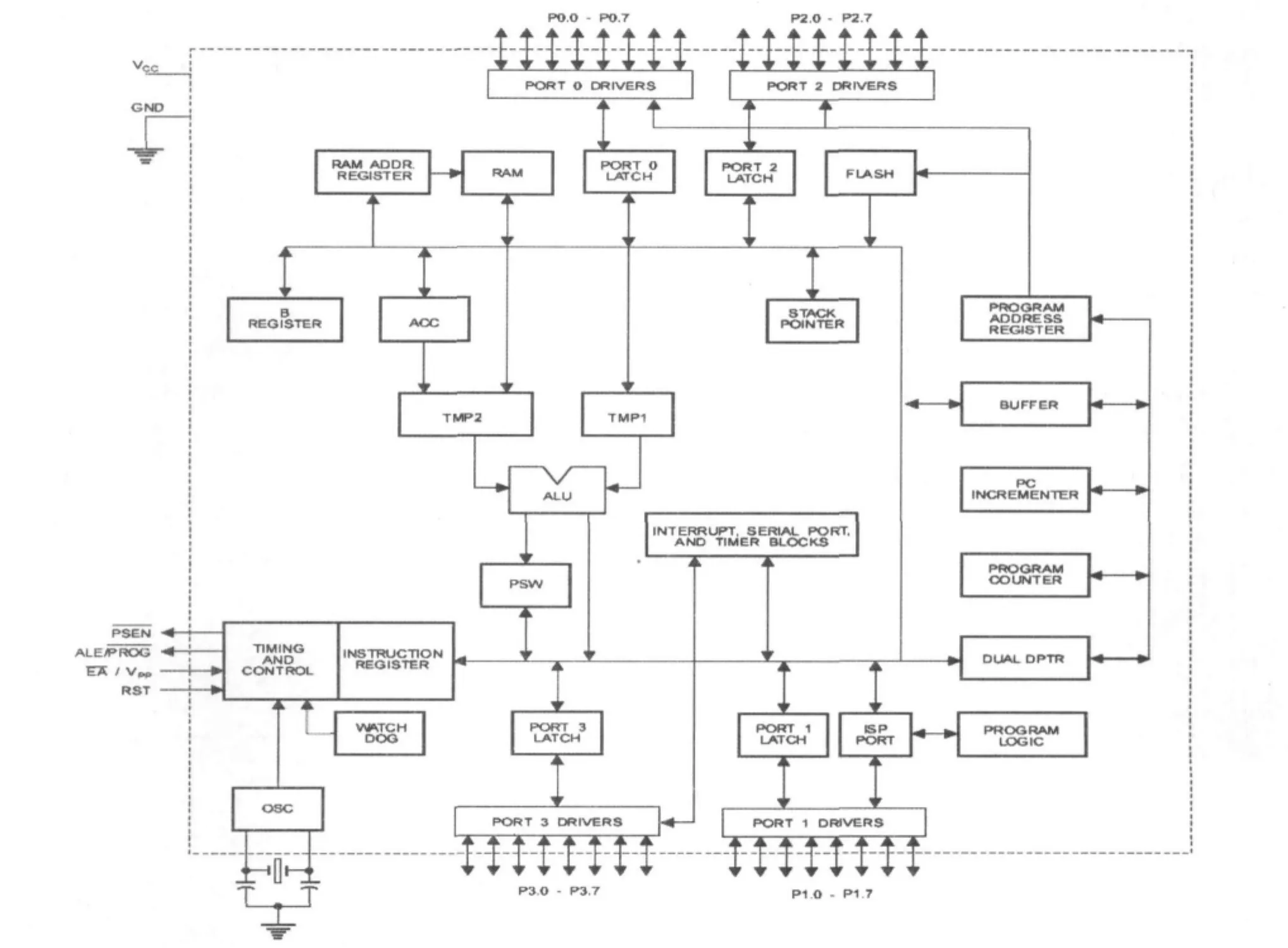

AT89S52是一种低功耗、高性能CMOS 8位微控制器,具有8K可编程Flash存储器。使用Atmel公司高密度非易失性存储器技术制造,与工业80C51产品指令和引脚完全兼容。片上Flash允许程序存储器在系统可编程,亦适于常规编程器。在单芯片上,拥有灵活的8位CPU和在系统可编程Flash,使得AT89S52能够为众多嵌入式控制应用系统提供灵活、超有效的解决方案。

AT89S52具有以下功能特点:8K字节 Flash,256字节RAM,32位I/O口线,看门狗定时器,2个数据指针,三个16位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。另外,AT89S52可降至0Hz全静态逻辑操作,支持两种软件可选择节电模式。空闲模式下,CPU停止工作支持,允许RAM、定时器/计数器、串口、中断继续工作。掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

图1 AT89S52功能框图

4 测试程序调试

AT89S52电路测试程序主要分为三部分进行调试:功能部分,直流部分,交流部分:

4.1 功能测试

测试AT89S52有两种方式,一种是通过测试系统执行外部指令,此时EA=0。一种是通过测试系统对芯片串行编程或并行编程,先把要执行的指令写入到内部FLASH存储器中,然后再执行内部指令并通过测试码点进行比对,此时EA=1。首先在TSB表中设置时间向量,然后在levels和DC Specs表中设置电源电压,输入电压,在表PatSets中链接测试码点文件,最后在测试系统Test Instances表中按Functional_T项进行测试。

4.2 直流测试

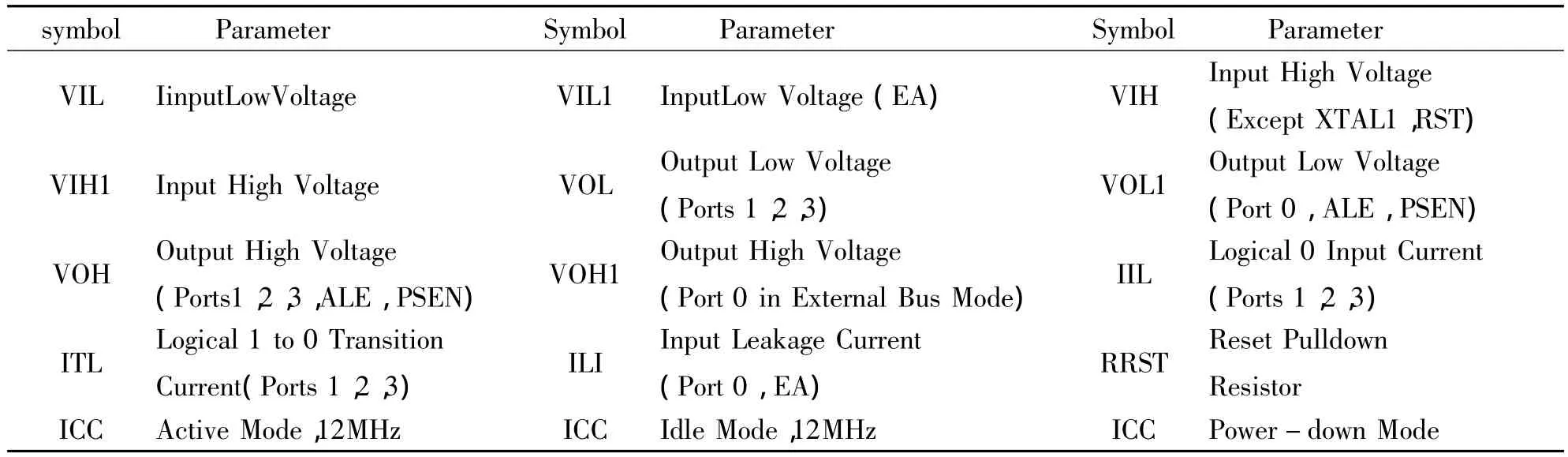

AT89S52共有16项直流参数,如表1所示。

表1 直流参数表

4.2.1 VIH、VIH1、VIL、VIL1 参数测试

这四项参数为输入电平,可以由测试系统直接给入参数手册上面规定的值即可,然后通过功能验证的方法进行测试。

4.2.2 VOL、VOL1、VOH、VOH1 参数测试

这四项参数为输出电平,可以在Test Instances表中BoardPmu_T项上进行,选择相关的测试管脚,进行参数设置,然后在选择需要的测试Pattern,完成测试。

4.2.3 IIL、ITL、ILI、RRST

前三项测试输入端电流,后一项测试复位电阻,都可以通过Test Instances表中PinPmu_T进行参数设置,然后强制电压在所选管脚上,就可以得出电流值,其中RRST参数需要换算成电阻值。

4.2.4 ICC Active Mode、Idle Mode、Power-down Mode

这三项参数为动态电源电流、空闲模式电源电流和掉电模式下电源电流。在Test Instances表中PowerSupply_T项上进行,需要注意的是Idle Mode和Power-down Mode要在码点中进行程序指令设置,P0口分别写入指令758701和758702,使状态进行匹配,即可进行测试。

4.3 交流测试

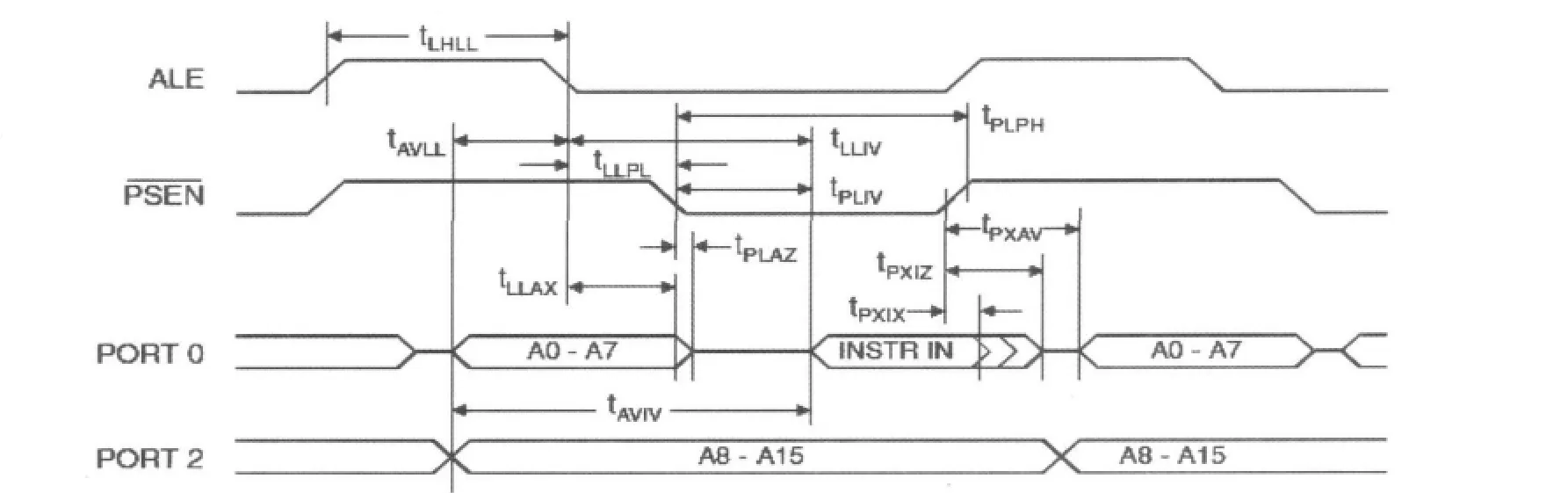

交流测试通常包括频率,数据传输延迟时间,建立保持时间等相关参数。下面以tLLPL tLLIV tAVIV tPXIZ tPLAZ五项参数进行测试,选择DC_Rise-Time_VBT项并设置好相关数值进行测试。具体波形如图2所示。

图2 交流参数图

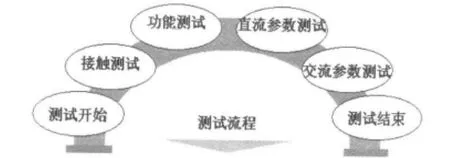

4.4 测试流程

AT89S52电路的测试流程,如图3所示。

图3 测试流程图

5 结束语

Teradyne Ultra FLEX是当今业内比较领先的集成电路测试系统,功能强大,测试精度高,覆盖面广,如何更加合理有效的使用,还需要测试人员进行不断的摸索开发,从而使测试程序更加有效的运转,提高科研及生产效率。

[1]Ultra Flex Mixed Signal Programming Student Manual[M/CD].Teradyne Inc 2009-2.

[2]《现代集成电路测试技术》编写组.现代集成电路测试技术[M].北京:化学工业出版社,2005.