COMS电路的参数提取及模型建立

冯海涛,裴志强,刘宝娟

(中国电子科技集团公司第四十七研究所,沈阳 110032)

1 引言

随着器件的特征尺寸降到深亚微米级,器件的物理特性和电学特性发生了很大的变化。由此导致的时序不收敛是深亚微米设计中最常见的问题,因此一般会对设计进行静态时序分析。进行静态时序分析需要用到包括设计中所有单元时序信息的时序工艺库,但是,一般晶圆工厂提供的时序工艺库只包括了基本单元的时序信息,对于全定制电路来说也不适用。这里就详细阐述一下使用synopsys的各种工具进行寄生参数的提取以及时序模型的建立方法。

2 时序模型建立流程

2.1 时序模型类型选择

现在使用的时序模型有K-factor模型和查找表模型两种。查找表模型相对于K-factor较为常用,因其不以线性方程的形式给出,具有非线性,具有较高的准确性。因此,为了进行更准确的静态时序分析使用查找表模型。

2.2 查找表时序模型建立流程

建立时序模型的关键主要有下面几个步骤:

·建立版图单元和逻辑单元的对应关系;

·提取线网的寄生参数文件;

·建立单元版图的时序模型。

图1给出了实现上面几个步骤比较详细的流程。

为了进行详细的时序分析,确保设计的芯片在各种条件下可以正常工作,需要对每个单元在最好、最坏和典型情况下,以不同的输出负载,不同的输入驱动能力和输入组合做各单元的SPICE模拟,获得时序参数。针对一般0.18μm的工艺库而言,就是要求出在 FF(最快,电压1.98V,温度0℃)、TT(典型,电压 1.8V,温度 25℃)和 SS(最慢,电压1.62V,温度125℃)三种情况下对应不同的输出负载,不同的输入信号渡越时间,给出路径敏化信号后测量得出的延时数据。

图1 单元时序建模流程

2.3 具体实例

下面以一个比较简单的传输管PT为例说明查找表模型建立的流程。IN是数据输入端;C是控制端,高电平有效;OUT是数据输出端。

2.3.1 版图前期准备及网表准备

在进入时序建模流程以前,必须对版图进行设计规则检查(DRC),电器规则检查(ERC)和版图原理图对照(LVS)三项验证工作。三项检查顺利通过,确定了版图和原理图无误以后,从版图导出gds网表 pt.gds,从原理图导出 cdl网表 pt.sp,为下面的完全LVS做准备。

2.3.2 完全 LVS检查

为了能够将版图中提取的寄生参数正确地反标到逻辑网表,版图和逻辑图必须通过LVS验证。LVS的实质是将逻辑网表(cdl)与版图上提取的网表(gds)相比较,通过LVS说明版图的单元、线网和逻辑图中的单元、线网能够进行准确的对应。一般LVS验证只是说明顶层单元逻辑与版图的功能是否一致,而LVS验证更进一步要求逻辑等效端口不能交换,且逻辑与物理的基本单元必须完成端口匹配。从传输管的版图和逻辑图可以发现,版图上应该标注有完整的端口文本信息,而且版图的端口应该和逻辑图一致。由于这个单元没有层次化设计,只需要运行一次晶体管级LVS就可以了。如果是层次化设计,需要分别运行单元级和黑盒级两次LVS。利用Synopsy Hercules软件,成功执行以后会在相应工作目录生成寄生参数提取程序STAR-RC运行所需要的XTR视图目录。

2.3.3 寄生参数提取

经过LVS之后,可以得到逻辑电路与物理版图之间的对应关系(XTR库),根据这一关系再结合厂家的工艺文件可以提取版图中互连线的寄生参数,这些参数包括连线自身的电阻和电容,以及连线之间的耦合电容。利用的是Synopsys的STAR-RC软件提取寄生参数。STAR-RC的调用命令是:>StarXtractgui。提取时需要把 XREF设置为“YES”,CELL_TYPE设置为SCHEMATIC,这样提取出来的层次化结构和单元实例名都是和原理图一致的,否则就会根据版图对其命名。根据原理图命名对后面的检查和计算端口电容都比较有利。执行成功后可以得到带寄生参数的HSPICE网表文件Test.spf。

2.3.4 建立单元版图的时序模型

得到带寄生参数的HSPICE网表Test.spf以后,可以利用该网表,为该单元的时序路径建立测量文件,从而建立其时序信息。每个文件根据路径敏化的要求和查找表的格式,加上不同的激励,在合理的范围以内加上不同的负载,不同的时间索引点,在典型情况下测量。

由于传输管电路比较简单,它只有一条时序路径,只需针对数据输入端是上升还是下降这两种情况进行处理。使用Synopsy的HSPICE软件进行瞬态分析。如图2所示。

图2 HSPICE仿真

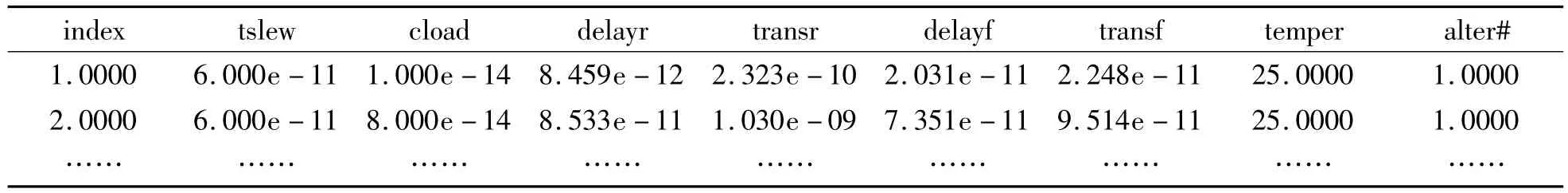

通过HSPICE仿真之后,可以得到mt文件,如表1 所示。文件中有 delayr,transr,delayf,transf四个测量值。

表1 mt文件的测量结果

有时候个别测量数据会出现负数的情况,这是因为输出所加的负载很小,而单元的驱动能力很强所致,属于正常情况。

最后把测量到的数据,按照查找表模型的要求依次填入,便可以得到对应的时序模型。

3 结束语

随着数字设计复杂度的增加,静态时序分析是非常必要的。根据比较准确的时序模型进行静态时序分析,不仅可以快速完成对设计的时序验证,而且根据时序分析结果还可以指导和改进设计。

[1]秦世才,等.模拟集成电子学[M].天津,天津科学技术出版社,1996.

[2]梁家昌,等.线性电路瞬态分析[M].北京:机械工业出版社,1987.