程控调幅多路并行信号源

苏淑靖,张凯琳,刘利生

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

0 引言

信号源是我们常用的一种通用电子仪器,它可以模拟与设备所需的实际环境相同的信号,以便与其他仪表和仪器组成自动测试系统,进行动态控制[1]。从20世纪初期发展至今,为了弥补传统信号源在功能、精度和性能等方面存在频率精度低、分辨率不高、频带窄等不足,DDS(Direct Digital Frequency Synthesis)技术应运而生。目前该技术的常用方法是利用性能优良的DDS专用器件“搭积木式”设计电路,该方法设计的信号源具有工作频率范围宽、频率转换速度快、相位连续性、正交输出、频率分辨率高等优点,在各种电子对抗技术和现代电子测量仪器中获得了广泛的应用[2]。

这种“搭积木式”电路设计方法虽然直观,但DDS专用器件价格较昂贵,输出波形有限,输出路数少,不适合要求同时输出多种波形的应用场合。且DDS专用芯片控制部分需要高速微处理器协助,使用受到一定限制。高速可编程逻辑器件的特点是容量大、速度高、成本低,因此现在的发展趋势是用可编程逻辑器件进行DDS信号源设计[3-4]。但一般的基于FPGA(Fiel d Pr ogrammable Gate Array)和DDS的信号源也存在一些问题。输出路数少,如文献[5—6]中的信号源仅为单路输出,文献[7]中也只有两路并行;而文献[8]中的信号源在幅值调节的方法上也存在成本高、抗干扰能力差等缺陷。

因此,本文设计了FPGA和DDS技术相结合的程控调幅多路并行信号源。

1 基于DDS的幅值调节方式

目前,基于FPGA的DDS的信号源的幅度调节方式有2种。第一种是利用外部存储器芯片,如文献[9]中,将不同幅值不同波形的归一化波形值烧入存储器中,然后按照需要输出的信号要求进行寻址,再通过D/A转换输出。这种方法直观方便,但外部存储器芯片价格高,容量也有限,在需要输出多种波形及幅值步进小的情况下,是不能满足设计需求的。

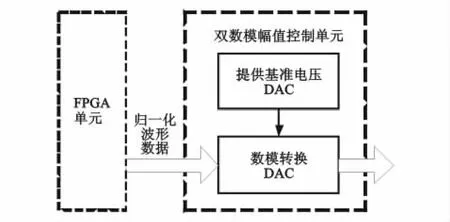

第二种幅度可调设计是基于双数模的方式,由多个DAC嵌套的方式来实现。如文献[8]中,输出信号的幅度控制是通过2片DAC芯片实现的,其中第1片用来将FPGA输出的波形的数字信号转换为模拟阶梯信号,幅值的调节则是通过第2片的输出改变第1片DAC的参考电压来实现的。可以看出这种方法硬件成本很高,设计过程复杂。两片DAC的输出受外围电路影响,对于精度不高的电阻电容,误差就较大,且抗干扰性差,见图1。

图1 基于FPGA的DDS信号源的幅度调节方式Fig.1 The block diagram of signal source based on FPGA and DDS

2 基于FPGA的程控调幅

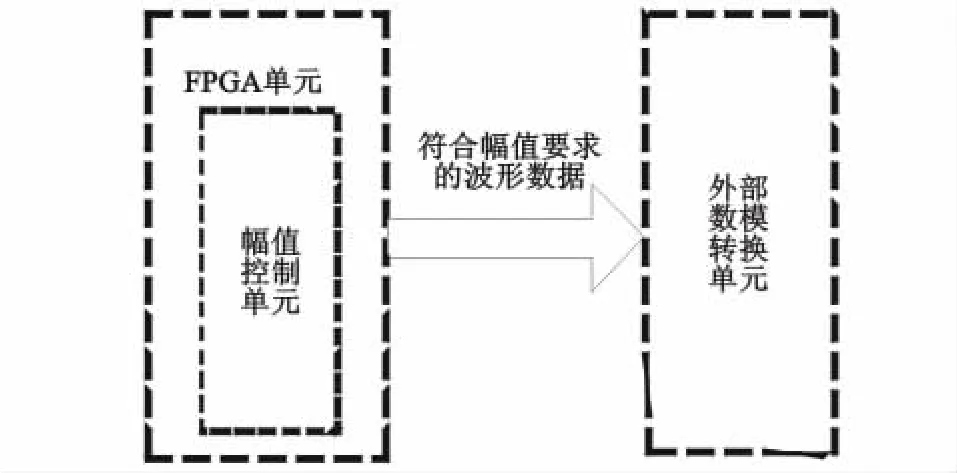

本设计信号源中,启动信号源时控制命令由上位机下发,信号源模块接收传来的LVDS串行数据并进行解串后传输至FPGA进行分析。DDS部分在FPGA内部完成,设计思想参考了流水线式无缝访问方式,32路信号都是共享一组波形ROM,在最大程度上提高了资源利用率,见图2。

信号源的频率可调采用DDS技术实现。一个直接数字频率合成器(DDS)由频率控制字、相位累加器、波形储存ROM、D/A转换器和低通滤波器(LPF)构成。

图2 程控幅值方式Fig.2 The block diagram of Programmable amplitude modulation

本设计中DDS技术的相位累加器和波形储存ROM在FPGA内部实现。相位累加器由32位加法器和32位寄存器级联构成对上位机下发的频率控制字进行累加,每累加一次所得结果的高N位作为波形ROM的地址进行一次寻址,寻址输出波形采样点的二进制数字量进行数模转化,最后经过LPF后输出。

波形ROM调用FPGA内部IP Core实现,其中ROM1-ROM4分别存放正弦波、三角波、锯齿波、矩形波的归一化数字量[10]。为了合理利用资源,信号源的32个通道共享4个波形ROM,而对波形ROM的访问方式借用了流水线式的设计方式,达到了数据流没有时间停顿地送到数据流的下级处理模块,从而实现了数据最大限度的无缝缓冲与处理。

本设计中采用了基于FPGA的程控实现幅值可调的思路,即在FPGA内部就将归一化波形的数字量转化成所需幅值波形的数字量后再传给D/A转换器进行数模转化。转化的方式是利用数字量的线性关系,在FPGA内部来作数据处理。虽然FPGA作运算处理的速度不是最理想的,通过精确地计算配合硬件,尽量简化数据处理的过程。只需要调用FPGA内部的运算IP Core就可以实现灵活调节幅值的功能,不会造成逻辑的占用负担。

程控调幅的方法可做到步进小、速度快的调控,此法更加灵活,可拓展性和适应性都非常高,设计成本更低,且更适合于多路可调节的信号源。

在D/A转换之后要输出32路信号,若每一路都采用一个D/A进行模数转换再调理输出的话,一来标准的板卡物理空间尺寸不允许,二来增加了系统开发的成本,再者违背了设计简洁的原则。在本设计中通过电子开关及电压保持电路把各路模拟信号切换到相应的通道上,实现一对多的切换。

3 理论分析与性能测试

3.1 实现程控调幅

在本设计中,信号源技术指标为输出信号幅值的精度达到0.1%。D/A转换器的分辨率越高,输出波形的精度也就越高,且随着量化精度的增加,频谱中杂波的幅度相应降低。理论上,选用14位分辨率的DAC即可实现本设计的精度要求,但由于DAC电路本身产生的误差,实际的DAC电路无法达到DAC芯片所描述的精度[10]。因此,为了得到14位的量化精度,所选用的DAC芯片应具有14位以上的量化精度,在此选用16位分辨率的高精度AD768。为保证精度要求,D/A转换器的外围电路及信号调理电路采用精度为0.1%、温漂系数为10 pp m/℃的优质电阻。

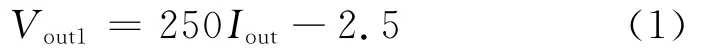

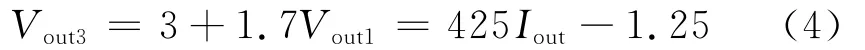

根据要求输出的模拟信号电压范围要求在-1~+7 V,AD768为电流输出型,采用高速运放AD811实现电流/电压转换。在AD768 AR参考电流为5 mA的前提下,REFOUT引脚输出的2.5 V的参考电压以及1 kΩ限流电阻(R103)使得电流IBIPOLAR恒为2.5 mA,Iout为0~20 mA。根据I/V转换电路设计可得Iout与Vout1关系式:

由式(1)可得Vout1的范围为-2.5~+2.5 V,图3中Vout1经调理输出Vout2和Vout3分别为:

根据式(1)—式(3)可得:

由于AD768输出电流与输入数字量值D关系为:

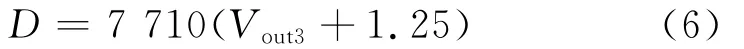

因此,由式(4)、式(5)可得:

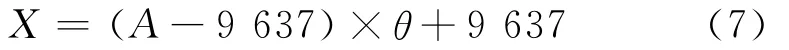

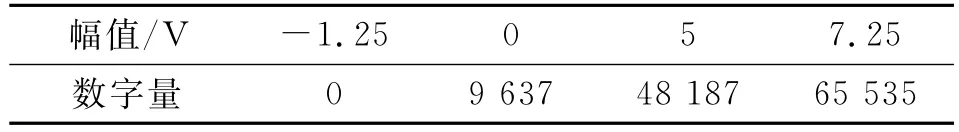

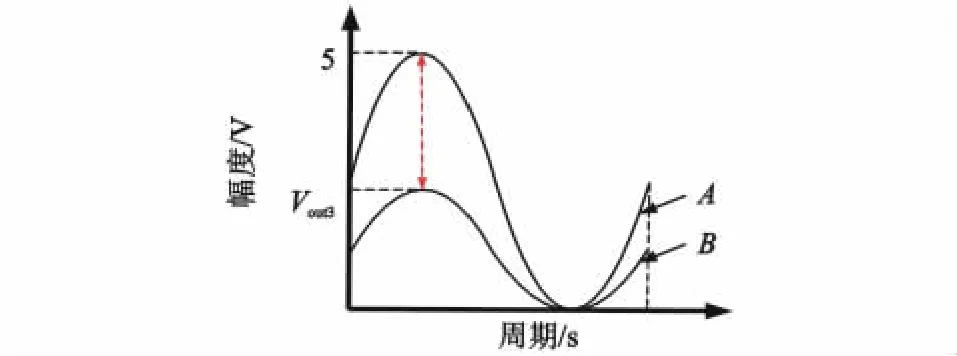

图3为输出信号间的数字量非线性关系示意图,其中A曲线为归一化波形,B曲线为可调范围内任意幅值波形,表1为输入数字量与输出信号幅值的对应关系表,通过计算得Vout1与归一化数字量(0~5 V)数字量的非线性关系为:

式(7)中,X为对应Vout3所需要的数字量,A为此时刻DDS部分寻址所得的归一化信号的数字量,θ为上位机下发的16 bit的幅度系数(θ=Vout3/5)。

表1 幅值与数字量的对应关系表Tab.1 The corresponding relations of amplitude and digital quantity

图3 输出信号间的数字量非线性关系图Fig.3 The diagram of digital modulation principle

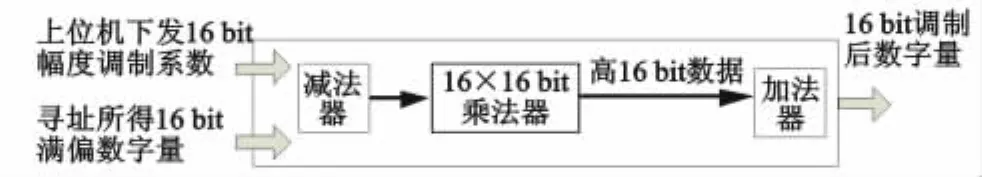

幅度可调模块是式(7)在FPGA内部的逻辑实现如图4所示,其中减法器实现(A-9 637)运算过程,16×16 bit乘法器调用FPGA内部IP Core实现。乘法器计算得出的32 bit数据中高16 bit数据经过加法器实现(+9 637)后输出至D/A转换器。

图4 FPGA内的幅度调制模块Fig.4 The diagram of amplitude modulation in FPGA

3.2 性能测试

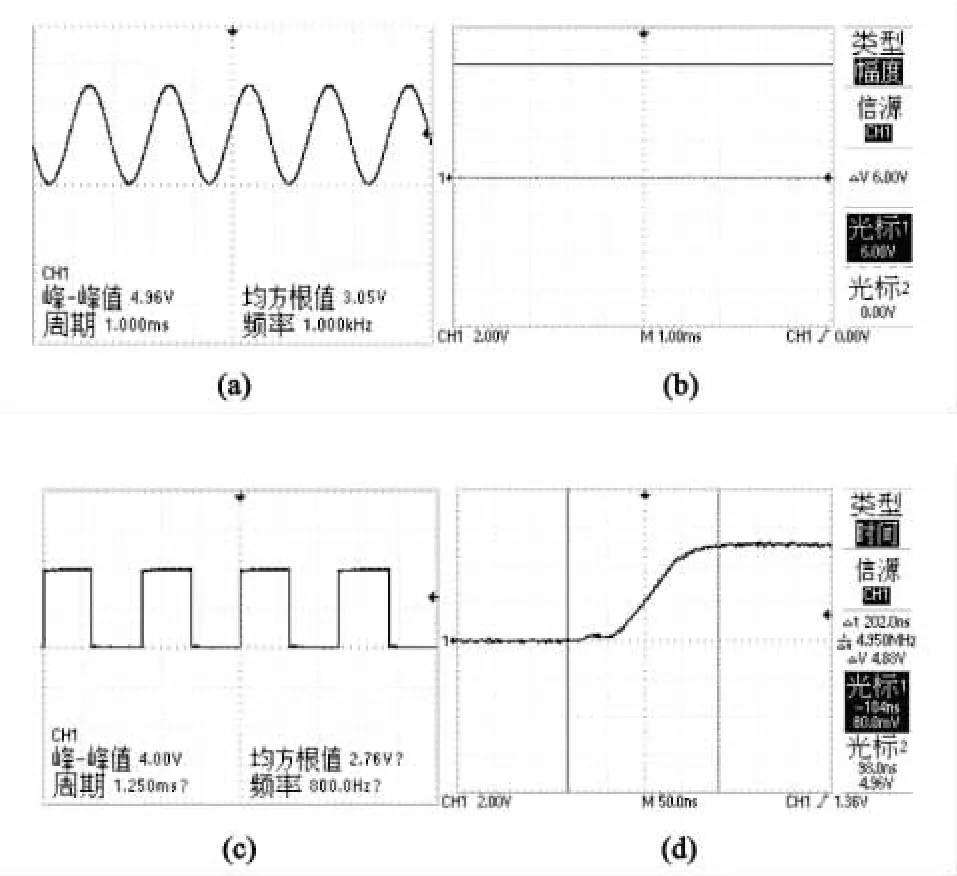

针对传统的多路信号源存在的输出路数少、成本高、资源占用率高等问题,设计信号源具有同时输出32路模拟信号的功能,输出波形具有正弦波、三角波、锯齿波、矩形波和直流量5种选择,交流量输出频率为1 Hz~1 k Hz范围内可调,交流量输出幅值为0~+5 V可调,矩形波边沿时间小于1μs,直流量输出幅值为-1~+7 V,输出信号的精度为0.1%。

通过对设计信号源的性能测试,信号源输出波形如图5所示,其中(a)为输出频率1 k Hz,幅值5 V的正弦波;(b)为幅值6 V的直流量;(c)为输出频率800 Hz,幅值4 V的矩形波;(d)为矩形波上升沿时间。从图中可以看出,信号源输出波形光滑,频率稳定度高,矩形波边沿时间为202 ns<1μs,直流信号精度达到0.1%,满足设计要求。

图5 信号源输出波形Fig.5 The diagram of Signal output wave

4 结论

本文设计了基于FPGA和DDS技术相结合的程控调幅多路并行信号源。该信号源发挥了DDS技术频率转换快、频率精度高和FPGA逻辑资源丰富、速度快等特点,在FPGA内实现DDS的资源优化,利用DDS原理配合FPGA无缝式内部访问IP Core方式实现频率可调;利用FPGA内部程序设计对归一化的数字量进行调制及转换实现幅值可调。

实验表明:该信号源可并行输出32路高精度信号,输出信号的频率、幅度、波形等均可由用户按实际需求通过上位机软件设定。直流信号的精度达到满量程的0.1%,可用于测试被测系统的静态特性,输出的矩形波边沿时间小于1μs,可用于测试被测系统的动态特性。该信号源可完成不同通道并行输出波形、频率和幅值不同的信号,且具有输出稳定、频率精度高、频率范围宽、成本低、设计灵活、集成度高、可扩展性强等优点。

[1]李祥伟.直接数字合成的技术原理与实现[D].上海:上海交通大学,2008.

[2]刘金亮.直接数字频率合成技术实现研究[D].北京:北京交通大学,2008.

[3]Wang Zheng Yu,Chang M C Frank,Chou Jessica Chiatai.A simple DDS architecture with highly efficient sine f unction lookup table[C]//Proceedings of t he 14th ACM Great Lakes Sy mposium on VLSI.USA:ACM,2004.

[4]周芸,路青起.基于数字信号处理器技术的直接数字合成快速跳频通信信号源[J].探测与控制学报,2007,29(5):77-80.ZHOU Yun,LU Qingqi.The design of signal source of fast hopping-frequency co mmunication based on DDS&DSP[J].Jour nal of Detection & Contr ol,2007,29(5):77-80.

[5]杨秀增.基于FPGA和DDS的信号源设计[J].电子设计工程,2009,11(17):7.YANG Xiuzeng.Design of a signal generator based on FPGA and DDS[J].Electronic Design Engineering,2009,11(17):7.

[6]孙昊.基于FPGA的DDS信号源设计[D].成都:电子科技大学测试计量技术与仪器,2009.

[7]邓耀华,吴黎明,张力锴,等.基于FPGA的双DDS任意波发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,30(11):2 255-2 258.DENG Yaohua,WU Liming,ZHANG Likai,et al.Design of dual DDS ar bitrar y wave generator based on FPGA and denoising of spur noise[J].Chinese Jour nal of Scientific Instru ment,2009,30(11):2 255-2 258.

[8]张有志,张鹍.基于FPGA的幅值可调信号发生器设计[J].电子设计工程,2011,19(9):115-118.ZHANG Youzhi,ZHANG Kun.Design of amplitude adjustable signal generator based on FPGA[J].Electronic Design Engineering,2011,19 (9):115-118.

[9]赵呈恺,甄国涌,焦新泉.基于FPGA和AD768的高精度多路信号源设计[J].机械工程与自动化,2010,158(1):139-141.ZHAO Chengkai,ZHEN Guoyong,JIAO Xinquan.Design of high accuracy multi-channel signal source based on FPGA and AD768[J].Mechanical Engineering & Automation,2010,158(1):139-141.

[10]王巧兰,丁志宇.在DDS中波形存储表设计的实现方法[J].中国测试技术,2008,34(4):65-66.WANG Qiaolan,DING Zhiyu.Design of wavef or m ROM in DDS[J].China Measurement & Testing Technology,2008,34(4):65-66.