基于FPGA的高速采样系统实现*

傅仙伟,赵翠芳,张长江

(浙江师范大学 数理与信息工程学院,浙江 金华 321004)

目前数字信号处理技术的应用范围越来越广,对数字信号处理技术的要求也越来越高,尤其对高速采样和实时高速信号处理电路的要求也更加严格,于是出现了高速模数转换器件ADC(Analog Digital Converter)和高速可编程器件。这一发展趋势也带来了诸如ADC采样速率和集成电路处理速率匹配、PCB布局布线、ADC输出数据同步等一系列问题[1]。基于这些问题的考虑,本文在激光回波数据采集的两路双通道250 MHz高速采样电路设计中,除了在器件选择、布局布线等硬件方面给予综合衡量,还在数据输出同步上给出了软件处理方法。系统中 ADC选择 TI(Texas Instruments)公司的 ADS62P29IRGC[2],FPGA选择 Xilinx公司 Virtex-4系列的 XC4VSX35-FFG668,其优点是I/O接口和内部存储器资源丰富,功耗低,处理速度快[3-4]。最终经过测试,该高速采样信号处理电路达到了250 MHz的处理速度,符合本系统设计要求。

1 高速采样系统设计实现

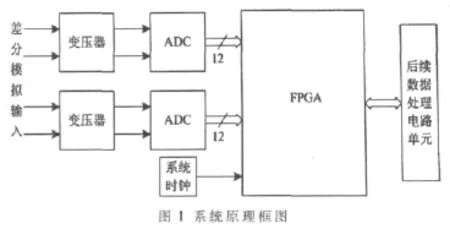

1.1 工作原理

系统原理框图如图1所示。外部差分模拟输入信号经过变压器耦合到ADC的差分输入端,ADC输入时钟由FPGA内部性能稳定的数字时钟管理模块DCM(Digi-tal Clock Manager)产生250 MHz的信号,DCM产生的时钟再经过差分输出缓冲器OBUFDS转换为差分信号提供给ADC作为采样时钟,此时钟经过ADC内部缓冲器后作为数据输出同步时钟。另一方面,FPGA将ADC配置成双数据速率低压差分信号传输DDR LVDS(Double Data Rate Low Voltage Different Signaling)工作模式,在数据输出同步时钟的控制下,ADC的每个通道以250 MHz的速率输出 6对(即 12 bit)差分数据送给 FPGA,然后再经FPGA送入后续数据处理电路进行处理。

1.2 布局布线

考虑到本采样系统的高速性,为最大程度地削减电磁干扰 EMI(Electro Magnetic Interference)、增强系统的电磁兼容性EMC(Electro Magnetic Compatibility)以及数据传输的同步性,需在PCB布局布线时结合以下几方面给予综合考虑[5]:

(1)在元器件密布的Top层的下一层放置地层,以地层的大面积铜为器件提供一个参考面,起到屏蔽的作用。

(2)内电层与地层应该紧密耦合,高速差分信号走线层放置在这两层之间。系统在工作时高速信号线会产生大量的电磁辐射,对周围器件造成干扰;而内电层和地层的大面积铜就很好地提供了屏蔽罩效果,从而大幅度地削弱了电磁干扰。另外,在板的边缘会向外辐射电磁干扰,因此内电层和地层在布局时还要遵守“20H原则”,即内电层相对地层要内缩20H的距离,以抑制边缘辐射效应,将内电层内缩使得电场只在地层范围内传导,有效提高电路板的EMC。这里H指的是内电层与地层之间的距离。

(3)为提高数据传输的抗干扰性和同步性,ADC的输入时钟线和高速输出信号线采用差分走线,并且两路ADC的输入时钟线严格等长,而且各个输出线也要求严格等长,必要时采用蛇形走线。这样就从硬件上保证了传输延迟和衰减阻抗的一致性。此外,线与线之间的距离要在3个线宽及以上,以减少线间信号串扰[6]。

1.3 FPGA模块设计

整个 FPGA分为6个模块:ADC配置、DCM、输入输出缓冲 (包括 IBUFGDS、IDDR和 OBUFDS)、 同步控制、RAM和后续数据处理电路接口。系统上电后,配置模块将ADC配置成DDR LVDS工作模式。DCM将50 MHz的系统外部输入时钟经倍频和分频后转换为三路[7],即由DCM模块 CLKFX产生的 250 MHz、CLK0产生的与输入时钟同相的50 MHz和CLKDV产生的10 MHz。250 MHz经过OBUFDS后差分送给ADC作为其采样时钟,50 MHz输出给同步控制模块、10 MHz输出给ADC配置模块。ADC输出的差分数据信号经IDDR后送入RAM,IDDR的工作时钟由ADC的数据输出同步差分时钟经IBUFGDS后提供。在同步控制模块的作用下,两路ADC总共4个通道的数据被同时送入RAM,之后后续数据处理电路单元再将数据读走。FPGA内部结构图如图2所示。

1.4 IDDR的约束

由以上分析可知,当ADC工作在DDR LVDS模式下,在一个采样周期内,ADC分别在采样时钟的上升沿和下降沿各采一次数,因此其输出的每个数据包含2bit。基于对本系统高速特性和采用DDR LVDS工作模式这两方面的考虑,利用FPGA的IDDR模块对ADC传给FPGA的数据进行适当的降速处理以及对IDDR模块进行更进一步的约束 (包括物理约束和时序约束)是十分必要的[8]。

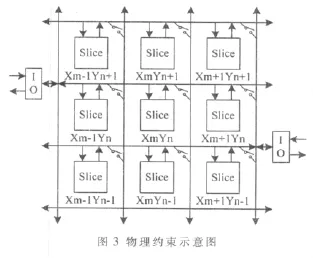

物理约束主要包含两方面内容:

(1)与CPLD不同,FPGA的I/O口之间的物理链路是多种多样的,而不同的链路将会带来不同的信号延迟,因此需通过编程添加物理约束以进一步减小信号传输时延。

(2)数据处理单元的具体位置通过约束来实现,即Slice在FPGA内部的物理位置加以指定。

物理约束示意图如图3所示。

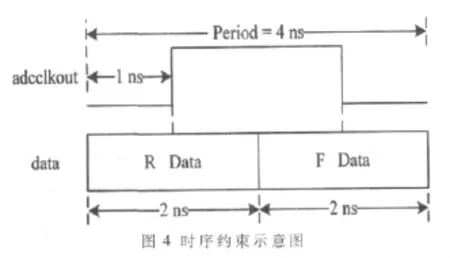

时序约束。对于ADC送入RAM里的数据加上时序限制,这样就可使得程序在综合实现时以此限制为准则最大程度地优化FPGA内部的布局布线,从而进一步确保数据的传输延迟一致。本文对经IDDR的数据加上时序约束限制,使得数据的中心位置与时钟沿严格对齐。

时序约束示意图如图4所示。

1.5 数据同步传输

由于器件的制造工艺原因,不同ADC之间的输出时钟或多或少存在相位差。因此,数据传给FPGA时也存在着不一致性。针对这一问题,本文通过利用ADC的输出时钟来同步接收使能信号RX_en,以消除不同ADC通道之间的时钟差异,实现信号的严格同步。首先在进程P1中,当复位信号clr有效时,立即将RX_en变为无效,FPGA接收数据被锁闭;否则,RX_en为有效。在进程P2中,当RX_en有效时,在ADC输出时钟的每个上升沿到来时将数据送入FPGA,当数据采样个数达到设定的值时,又将clr置为有效,此时 RX_en在进程P1中即被置为无效,当采样个数未达到设定值,clr保持无效。这样就从软件上最大程度地保证了数据传输的同步性。仿真结果如图5所示,从上至下波形依次为系统外部输入时钟信号clk_50M,ADC采样时钟信号adcclkout、发送使能信号TR_en、接收使能信号RX_en和复位信号clr。

2 实验结果

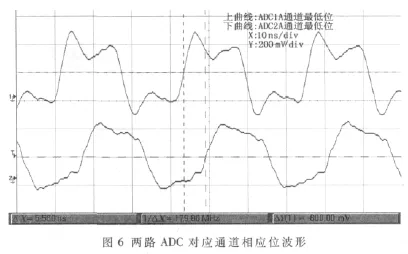

图6是在ADC输出数据每4个输出时钟周期加1的测试模式下,通过高带宽示波器同时测试的两路信号最低位的输出波形,此时信号的频率为250 MHz/8=32.5 MHz。由图可见两路波形良好,两路信号的时间差仅为5.560 ns。这是由于在进程P1中RX_en依赖于ADC采样触发信号TR_en的上升沿,而程序只能保证TR_en的上升沿和ADC输出时钟的上升沿相差一个ADC输出时钟周期,即1/250 MHz=4 ns,这由图5的仿真结果可以看出。实验结果表明数据同步性到达了预期的结果,系统达到了设计要求。

本文重点论述了基于FPGA的高速采样系统设计的具体实现方法,阐述了硬件布局布线要求和注意点、给出了IDDR的约束实现以及采样数据同步传输的硬件和软件实现方法。通过仿真结果和实验测试结果可知,本高速采样系统性能稳定、数据传输同步性良好,达到了设计要求。

[1]陆浩,王振占.基于FPGA的高速采样电路设计与测试[J].微电子学与计算机,2011,28(7):106-109.

[2]Dual Channel 14-/12-Bit,250-/210-MSPS ADC With DDR LVDS and Parallel CMOS Outputs[Z].Texas Instruments,2009.

[3]Virtex-4 FPGA User Guide(V2.6)[Z].Xilinx,2008.

[4]Virtex-4 Family Overview(V3.1)[Z].Xilinx,2010.

[5]周景润,景晓松,赵俊奇.OrCAD&PADS高速电路板设计与仿真[M].北京:电子工业出版社,2007.

[6]陈伟,黄秋元,周鹏.高速电路信号完整性分析和设计[M].北京:电子工业出版社,2009.

[7]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[8]张华,高陈岚.DDR源同步接口的设计与时序约束方法[J].计算机工程与设计,2008,29(7):1600-1602,1605.