基于CPLD的LED大屏幕显示控制系统

郭志冬

(三门峡职业技术学院 机电工程系,河南 三门峡 472000)

0 引 言

LED电子显示屏是集微电子技术、光电子技术、计算机技术、信息处理技术以及视频技术于一体的高科技大屏幕显示系统。它具有色彩鲜艳、亮度高、工作电压低、耗电量少、寿命长、驱动简单、动态范围广、性能稳定等优点,广泛应用在军事、铁路、民航、宾馆、体育、会议厅堂、广告宣传、高速公路、商场、文化广场、银行、证券市场等多个领域[1]。

LED电子显示屏的发光部分由LED发光二极管点阵拼装组成的,即构成LED阵列。随着社会发展的需要和科技的进步,LED显示屏的超大规模要求日益突出,显示实时性要求也越来越高。本设计将给出一种能满足大规模要求和实时性要求的系统模型,通过CPLD的引入,实现了LED屏自动扫描的功能,大幅提高了LED屏的频率,同时分担了CPU的任务,提高了CPU的处理能力[2]。

1 点阵显示原理

本设计采用的LED点阵模块是由4块点阵共16×16=256个LED发光二极管组成,可以用来显示汉字、英文、字母及简易图形。若要用点阵发光二极管显示汉字,首先要将汉字放在一个方块内,方格块分成16×16共256个小方格。在方块内写上汉字,在有笔画下落处的小方格里填上“1”,无笔画处填“0”。这样就形成了一个汉字二进制数据,将若干个汉字形成的数据组按一定规律排列,并把它贮存在存储器内,就完成了汉字库的建立工作。不过现在有很多现成的汉字字模生成软件,不必自己去画表格算代码。字模提取软件如图1所示。

图1 软件取字视图

软件打开后先输入汉字,再点“检取”,由十六进制数据组成的汉字代码便可自动生成,我们只需把所要的竖排数据复制到程序中即可。设计者把行列总线接到单片机的I/O口,再把分析得到到的扫描代码送入总线,装入存储器,便得到了显示的汉字信息[3]。

2 设计方案确定

本设计采用串行输出动态扫描的方法,此方法电路结构简单,译码电路也容易设计,适合应用在大屏幕设计中。采用动态扫描方法,其扫描速度必须大于一个下限值才能保证信息稳定显示。此外,显示信息提取、缓存数据更新以及输出数据锁存均需要时间;特别是采用了串行数据输出模式,数据由并行转换为串行、移位输出,占用了更多CPU的处理时间[4]。

因此,大屏幕显示引入CPLD来实现。系统核心是以CPLD构造的高速扫描电路显示数据的提取,并行转换为串行及扫描信号的产生都由高速的CPLD扫描电路控制。这样就把原本由CPU软件来完成的操作由硬件来实现,一方面提高了LED屏的频率,另一方面分担了CPU的工作。系统结构框图如图2所示。

图2 系统结构框图

高速的CPLD扫描电路实现的部分操作,使CPU操作得到了很大程度的简化。CPLD具有高频率工作特性,这就使它能高速地完成数据提取、并串转换以及移位输出;还能够很好地实现扫描同步、扫描译码输出。另外,此系统工作于单CPU模式,操作比较方便。

系统可分为数据产生、扫描输出和锁存驱动三大模块。其中,数据产生模块的控制单元是人机交互接口,可以是PC机,或者其它具有数据处理和通信连接的设备。MCU主要用于数据接收、存储控制。存储器可采用Flash存储器,可以电擦除和编程。扫描输出模块利用VHDL硬件描述语言和CPLD器件的高速特性,保证了RAM数据更新及数据刷新速度。

采用Altera公司的PLD开发工具QuartusⅡ,使用逻辑电路搭建方式或者VHDL语言方式进行逻辑设计,并对所设计的逻辑进行编译、仿真,最后将设计好的逻辑写入Altera的可编程逻辑器件中[5]。

3 CPLD的设计

3.1 芯片的选择

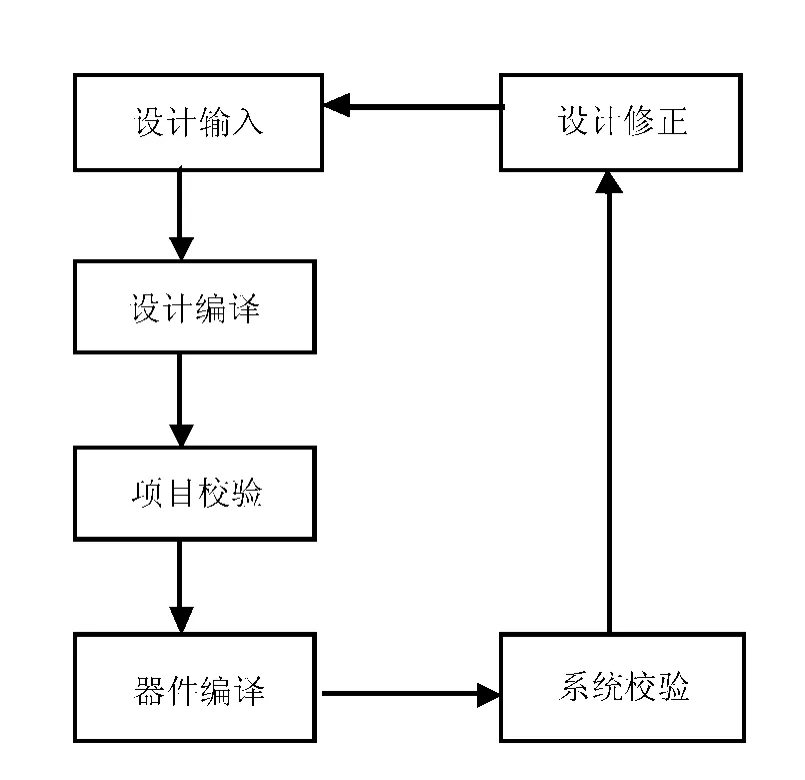

本设计使用Altera公司的FLEX10K系列可编程逻辑器件中的EPF10K10LC84-4。FLEX10K系列器件是高密度阵列嵌入式可编程逻辑器件系列。由该公司的QuartusⅡ开发系统提供软件支持,可在PC机上运行。其结构更复杂、功能更强大。从最初的电路设计思想到QuartusⅡ的时序仿真,一般开发流程如图3所示[6]。

图3 开发流程图

3.2 系统原理与设计

3.2.1 系统原理图系统原理如图4所示。

图4 系统原理图

首先,计算机要把显示的信息转换成和LED对应的点阵数据和地址,然后通过专用接口电路及单片机与CPLD接口电路把它送入扫描板的写入地址以及数据产生器中。写入地址及数据产生器的作用是产生要写入存储器的数据和地址。切换控制电路的作用是当有数据要写入存储器时就产生写控制信号。读写转换开关电路根据控制信号来决定完成以下两种操作的哪一种:是把写数据和写地址同存储器连接还是把读数据和读地址同存储器连接。读地址产生器产生存储器的读出地址。扫描控制电路把存储器中的数据送到显示屏上,同时产生时钟信号、锁存信号和行扫描信号。

以上每个功能模块都采用VHDL语言编写,在每个模块编写完之后进行编译,编译成功再进行功能仿真。

下面是采用原理图方法实现的转换开关电路图,如图5所示。

图5 转换开关电路原理图

3.2.2 单片机与CPLD/FPGA接口电路

在功能上,单片机与大规模PLD有很强的互补性。单片机具有功能灵活、性价比高、人机对话易实现、数据处理能力强等特点;复杂可编程逻辑器件即CPLD则具有高速度高可靠性和开发便捷规范容易转化为ASIC(专用集成电路)芯片等方面的优点[7]。现今,很多高性能仪器设备和智能电子产品中将会广泛采用以CPLD和单片机两类器件相结合的电路结构。CPLD与单片机的接口方式有两种,即总线方式与独立方式,本设计采用总线接口方式进行数据通信[8]。

单片机以总线方式与复杂可编程逻辑器件CPLD进行数据通信有许多优点。比如只需一条单字节指令就能完成所需的读/写时序。如:

MOV@DPTR,A;

MOV A,@DPTR。

CPLD与MCS-51单片机的总线接口通信的VHDL源程序编写时要注意双向端口RAM的VHDL语言描述。803l以总线方式工作,例如,由8031将数据5AH写入目标器件中的第一个寄存器LATCH_OUTl的指令是:

MOV A,#5AH

MOV@DPTR,,#6FF5H

MOVX@DPTR,A

当READY为高电平时,8031从目标器件中的寄存器LATCH_INl将数据读入的指令是:

MOV@DPTR,#9F7EH

MOVX A,@DPTR

3.2.3 系统设计

利用层次化设计方法,先组建底层设计,然后实现顶层设计。EDA工具软件提供了良好的逻辑综合与优化功能,它能够将设计人员设计的逻辑级电路图自动地转换为可供综合的门级电路,并生成相应的网表文件、时序分析文件及各种报表,最终生成可编程下载的文件。本系统中先将各个子模块进行编译,先生成子模块符号,然后建立顶层设计文件,在顶层设计文件中调入生成的各个子模块符号,经过恰当的连接即可得到设计顶层文件。CPLD扫描控制电路的设计顶层文件Top.gdf如图6所示。

图6 扫描控制电路顶层原理图

可以使用逐列循环扫描的方式来不间断地显示“VHDL”这4个英文字母。CPLD扫描控制电路包括以下3个模块:模块CHW,此模块控制每一个汉字或字母显示的时间,改变常数可改变显示时间的长短;模块CNTA,此模块产生列选择信号;模块CORA,此模块对应列选择信号输出每一列对应的数据,点亮相应的灯管。

3.2.4 编译仿真与项目校验

在对顶层设计文件“Top.gdf”构成的项目“Top”编译前,先选择目标器件,本设计使用Altera公司的FLEX10K系列可编程逻辑器件中的EPF10K10LC84-4,然后进行编译。编译过程中将产生一系列标准文件可进行时序模拟、适配,完成对设计的功能、时序仿真。时序仿真时进行时序分析,判断输入输出时间的延迟。对扫描控制模块进行时序仿真后得到输出波形,通过波形图中输入输出波形的对比,可以很容易看出预定项目的完成情况。本系统在设定了CLK,SEL信号的情况下,经过仿真后,设计的各信号的延迟在2 ns左右,基本符合设计指标要求。波形图如图7所示。

图7 时序波形图

4 结 语

系统采用以CPLD为核心来控制LED显示屏的方法,此方法把本来由软件进行的数据提取、并串转换以及移位输出和锁存等复杂的操作,交由CPLD硬件实现,大大提高了系统的可靠性。引入CPLD极大地简化了软件的编程,并且因为CPLD器件具有高速特性,能够使超大规模的LED显示屏的刷新速度得以保证[8]。此外,CPLD扫描电路的核心模块可通过PC显示卡接口,如此就可以借助计算机平台,将LED显示屏很好地应用于高速实时显示领域,满足了现如今对LED显示屏实时性的要求,具有非常广泛的应用价值。

[1]曾和兰,刘登桃.基于STC11L08的动画显示控制器[J].长春工业大学学报:自然科学版,2011,32(4):399-403.

[2]童星,熊文龙.基于CPLD的LED显示控制板[J].武汉理工大学学报:交通科学与工程版,2007(1):144-147.

[3]诸昌铃.LED显示屏系统原理及工程技术[M].成都:电子科技大学出版社,2000:35-157.

[4]刘爱荣,王振成.EDA技术与CPLD/FPGA开发应用简明教程[M].北京:清华大学出版社,2007:321-321.

[5]庄镇泉,胡庆生.电子设计自动化[M].北京:科学出版社,2000:3-15.

[6]潘松,王国栋.VHDL实用教程[M].成都:电子科技大学出版社,2000:5-15.

[7]唐杨波.基于单片机和CPLD共同控制的的LED大屏幕显示系统的设计与实现[J].科技创新导报,2009,13:24-25.

[8]马海涛,刘玉川,庄然,等.基于CPLD的时差法在小管径流量测量中的应用[J].长春工业大学学报:自然科学版,2007,28(3):264-266.