基于接口逻辑模型的MCU物理设计优化研究*

王 鹏,侯立刚,吴武臣,彭晓宏

(北京工业大学 集成电路与系统研究室,北京100124)

随着VSLI设计进入深亚微米时代,人们一方面因为芯片功能的极大提高而受益,另一方面,随着特征尺寸的不断缩小,芯片的物理设计变得越发复杂。同时,为了赢得市场,芯片设计的周期被不断压缩,而芯片设计的规模却仍旧飞速地增长,这使得物理设计的耗时问题得到了越来越多的关注。因此,需要有一种能够提高物理设计效率和竞争力的方法。

采用接口逻辑模型进行分层次的物理设计可以解决上述问题。接口逻辑模型(ILM)是由模块的接口逻辑电路转化而成的一种结构模型,它只包含时序受模块外部环境影响的逻辑单元。ILM在简化模块复杂度的同时可以提供准确的时序模型,在大型设计的顶层中,用ILM替换若干个模块,可以提高整个设计的时序优化质量,缩短设计耗时。

1 WT20芯片的展平式物理设计

WT20芯片是一款基于ARM Cortex-M0处理器的通用MCU芯片,其系统总线采用 AMBA AHB、APB双总线结构,挂载的 IP包括 UART、ADC等。

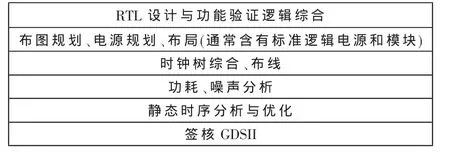

图1 传统展平式物理设计流程

如图1所示,WT20芯片的传统展平式物理设计以IC Compiler为平台,采用自下而上的设计方案:芯片经过RTL设计仿真,通过逻辑综合产生门级网表以及对应的标准时序约束SDC文件,再调用单元库中的标准单元和大模块单元,以及这些单元的时序库,通过布图规划、电源规划、布局、时钟树综合以及布线实现物理设计,提取RC参数进行时序分析,最后产生GDSII文档完成全部设计。

2 分层次物理设计

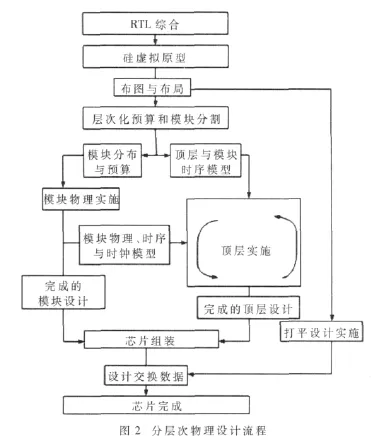

如图2所示,分层次物理设计方法通过层次化预算和模块分割,使一个很大的设计转化成多个小的设计,从而降低了设计的复杂度。设计顶层在例化设计好的模块之后,在布局(place)、时钟树综合(clock)以及金属布线(route)三个阶段的工作量会大大减小,从而缩短设计耗时。此外,在大型设计中,各个模块的物理设计同步进行,最后在设计的顶层进行芯片组装,做到并行不悖。WT20芯片基于接口逻辑模型的分层次物理设计的具体实现过程将在第3节和第4节中进行介绍。

3 ILM分层次物理设计的设计规划

在WT20芯片基于接口逻辑模型的分层次物理设计的初始阶段,首先需要为接口逻辑模型构造独立的模块(block),这部分工作在设计规划阶段完成,因此,设计规划是整个分层次物理设计的基础。设计规划包括如下工作:

(1)确定芯片面积。芯片的面积越小,每张硅片上产出的裸片数量越多,平均到每个芯片上的成本也越低。但如果芯片的面积过小,一方面会增加芯片中标准单元的拥塞程度,提高物理设计后期布线的难度,另一方面也会使芯片管脚难以摆放。因此,一个合理的面积设定可在保证布线及管脚排布的同时尽量节约产品的成本,所以设计规划的最初目标是估计芯片面积的大小[1]。

(2)创建plan group。plan group划定了接口逻辑模型所包含逻辑的范围。在创建plan group时需要考虑设计中的逻辑关系、模块规模以及在虚拟布局中的物理连接关系。通过IC Compiler的create_plan_group命令可以实现plan group的创建,plan group的形状及在芯片中的位置可以根据需要进行调整。在本设计中,通过对原有的WT20芯片设计进行静态时序分析,发现关键时序路径大量分布于ARM内核中mcu/sys/timing/init_imp/cortexm0integration区域内,因此将cortexm0integration作为一个plan group进行独立设计。

(3)plan group的管脚排布(pin assignment)以及时钟预算(timing budget)。IC Compiler根据 plan group的物理位置以及从plan group中获得的时序信息设定管脚的位置。在进行管脚排布时,应该避免在小面积的plan group边界上排布大量的管脚,否则会导致管脚排布失败。为了满足分层次设计时序收敛的要求,在管脚排布阶段要保证plan group拥有充裕的时序预算,这些工作可以通过allocate_fp_budgets命令来实现。

在完成上述三步后,plan group会被转化成软模块,其在接口逻辑模型的实现阶段会被用于生成ILM模块。图3中的黑色矩形部分是包含了plan group接口电路逻辑关系以及时序信息的软模块。

4 接口逻辑模型的实现

图4是一个简单原模块以及与其相对应的接口逻辑模型的示意图。接口逻辑模型包含了与之对应的模块的输入、输出端口以及与之相连接的组合逻辑电路和时钟电路[2],可以有效地缩短物理设计耗时,提高设计的承载量。与其他抽象模型相比,接口逻辑模型可以提供更精确的时序信息并且构建耗时更短[3]。

4.1 分层次物理设计数据库的准备

在这一阶段,需要为物理设计的顶层(top)以及由plan group生成的软模块分别构建物理设计所需的数据库。每一个数据库中包含能够被IC Compiler识别的milkyway library、标准设计约束SDC文件以及物理设计中所需的脚本。将plan group转化成软模块之后,通过split_library命令就可以生成模块级物理设计数据库。

4.2 接口逻辑模型的生成

在构架好物理设计库之后,由plan group转化成的软模块就可以在不影响顶层其他部分的情况下独立进行布局、时钟树综合以及布线等物理设计工作。完成软模块的物理设计之后,通过create_ilm命令将plan group生成接口逻辑模型,同时在顶层和模块层分别生成包含接口逻辑模型所有时序信息的库文件。图5是本设计中完成物理设计之后的软模块以及生成的接口逻辑模型,可以看到,相比右侧的软模块,左侧的接口逻辑模型的结构得到了明显的简化,这会使顶层设计的物理设计耗时大大减少。之后用create_macro_fram命令为生成的接口逻辑模型创建一个FRAM模型,该模型包含了对应接口逻辑模型的抽象物理结构信息,借助FRAM所提供的信息,IC Compiler可以在接口逻辑模型的上方进行布线。在MCU芯片设计的顶层例化组装已经完工的ILM模块,并完成其余的顶层物理设计后,WT20芯片基于接口逻辑模型的分层次物理设计就完成了。

5 分层次物理设计结果分析

本文从物理设计所耗费的时间(runtime)和物理设计静态时序分析结果两方面来对传统的展平式物理设计方法与基于ILM的分层次物理设计方法进行对比,验证后者是否能在节约设计耗时的同时,保证设计静态时序的相关性,优化时序结果。

5.1 物理设计耗时分析

通过比较在物理设计的布局优化、时钟树优化以及布线优化三个阶段展平式物理设计与基于ILM的分层次物理设计的设计耗时,计算后者与前者之比,如表1所示。得益于模块分割后,设计难度降低以及并行设计的特点,基于接口逻辑模型的分层次物理设计与传统的展平式物理设计相比,在布局优化、时钟树优化以及布线优化阶段的设计耗时都有大幅降低,有效地缩短了设计周期。

表1 各阶段分层物理设计与展平式物理设计的设计耗时之比

5.2 物理设计静态时序结果分析

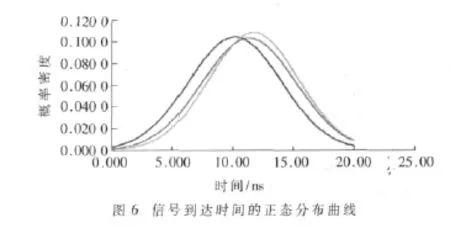

通过静态时序分析可以得到时序路径终点的信号到达时间(arrival time)以及代表路径时序紧张程度的slack,slack越大表示时序越宽松。采用统计的方法,选取10 000条穿过接口逻辑模型并且时序最紧张的关键路径作为采样,在布局、时钟、布线三个阶段进行静态时序分析,以路径的信号到达时间为随机变量,绘制正态分布曲线。如图6所示,从左至右依次为布局优化、时钟优化、布线优化三个阶段的信号到达时间正态分布曲线,三条曲线的对称轴以及离散程度并没有发生明显的变化,说明采用接口逻辑模型的分层次物理设计在不同设计阶段的静态时序分析结果是相对收敛的,具有较好的静态时序相关性。

表2 分层物理设计与展平式物理设计的时序优化对比

分层次物理设计的布线工作完成后,从穿过接口逻辑模型的时序路径中,同样选择10 000条关键路径作为采样进行静态时序分析。同时,在展平式物理设计中的布线完成阶段,对同样的路径也进行静态时序分析,比较相同路径的slack优化情况。发现通过基于接口逻辑模型的分层次物理设计,37%的关键路径的slack值升高了,时序得到了优化,表2列举了其中的 5条;57%的关键路径其时序结果未发生明显变化;仅6%的关键路径其时序结果出现了轻度恶化。

从以上结果可以看出,基于接口逻辑模型的分层次物理设计方法,在有效缩短设计耗时的同时,可以保证设计静态时序结果的相关性,并能优化部分关键时序路径,在大规模ASIC物理设计中,相比传统的展平式物理设计方法具有明显的优势。

[1]陈春章,艾霞,王国雄.数字集成电路物理设计[M].北京:科学出版社,2008.

[2]IC Compiler User Guide[S].2009:1-11.

[3]IC Compiler Design Planning User Guide[S].2009:1-4.