专用集成电路静态时序分析

唐 拓,张 伟

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

为了使电路性能达到设计预期目标,并满足电路工作环境要求,必须对一个电路设计进行诸如时序、面积、负载等方面的约束,并自始至终使用这些约束条件使电路设计软件按照设计意图来运行。设计约束一般包括专用集成电路(ASIC)生产厂家的设计规则约束和设计者自定义的设计优化约束。设计规则约束优先权高于设计优化约束,是隐含的,无须设计者指定,因此,这里重点讨论设计优化约束。设计优化约束包括设计者对电路性能上的一系列在时序、面积和版图布通性等方面的指标,其中最重要、最复杂的是时序约束。

2 设计的时序约束

2.1 单时钟同步电路的时序约束

要对一个电路的时序行为进行充分约束,至少应考虑时钟网络、端口输入输出延迟以及端口的驱动和负载特性。

2.1.1 时钟网络

对于一个实际的时钟网络,最重要的两个属性就是时钟的传播延时和时钟的不确定性。时钟的传播延时包括时钟源延时和时钟网络延时。在版图设计完成之后,时钟树上电路单元和网络延时等参数可以反标回来,通过适当设置,让这些延时信息在时钟网络上传播,这样可以自动获得时钟的这些重要属性。

当时钟网络上包含除缓冲器和反相器之外的逻辑时,就会产生门控时钟信号。通过约束使门控信号在相对时钟沿的建立时间和保持时间区域内保证不发生变化。

最小时钟脉宽的检查对时序电路非常重要,由于时钟网络上的门控单元和延时等的影响,脉宽在时钟的传播过程中会减小,可能在时钟网络的某些点上,时钟不再往后传递。因此必须设定脉宽的最小限制。

2.1.2 端口延时

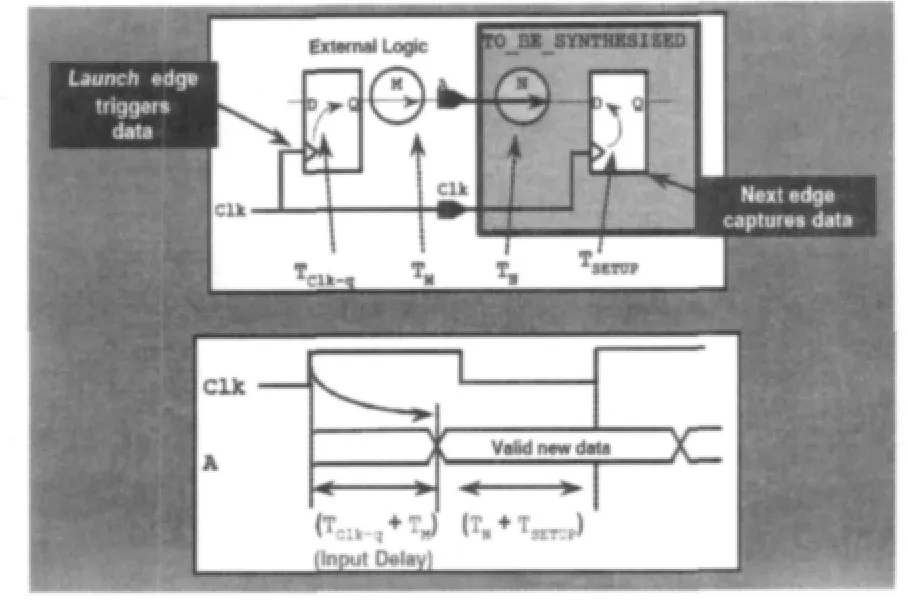

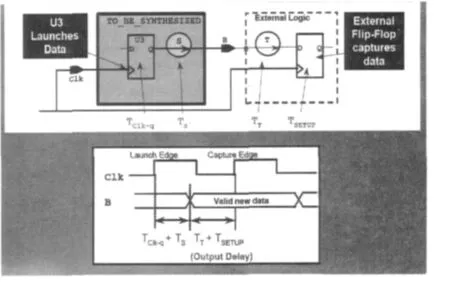

端口输入延时是指外部路径到电路输入(或双向端口)的相对于时钟沿的时间。端口输入延时应该等于从源寄存器时钟脚到驱动单元(输入脚的直接驱动单元)输出脚的延时减去驱动单元与负载相关的那部分延时。端口输出延时是指输出脚(或双向端口)到外部寄存器的路径延时,端口输出延时的最大值等于从输出脚到外部寄存器数据端的路径延时的最大值加上寄存器的建立时间。端口输出延时的最小值等于从输出脚到外部寄存器数据端的路径延时的最小值减去寄存器的保持时间。输入(input delay)和输出(output delay)延迟的图解如下。

图1 输入延迟

图2 输出延迟

2.1.3 端口的驱动和负载特性

端口的驱动和负载特性描述了电路与外部环境的接口,将影响电路的时序行为。应用环境转变到约束如图3所示。可以为不同的输入端口从库单元中选择不同的驱动单元,为输入、输出端口指定负载值,同时还可以为输出端口设定扇出负载的大小。在端口进行时序约束时,应考虑端口驱动和负载特性对时序的影响。

图3 电路的驱动和负载信息

2.2 多时钟同步电路的时序约束

多时钟同步电路是指电路中的多个时钟都由同一时钟源派生而来,它们之间有相对固定的相位关系,其中有的时钟不一定有实际对应的电路端口。从总体上说,多时钟同步电路可以采用与单时钟同步电路同样的约束策略,也包括定义时钟(必要时需要建立虚拟时钟作为端口输入、输入延时的参考)、指定I/O脚相对时钟的延时等步骤。由于可能出现一个端口或网络上存在多个约束的情况,时序分析工具总是选择最苛刻的约束条件作为计算建立时间和保持时间的约束条件。对于特殊的电路结构,还可以通过设置多周期路径和最大、最小延时等办法,来满足建立时间和保持时间的要求。

3 静态时序分析

静态时序分析技术是一种穷尽分析方法,用以衡量电路性能。它提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟传播,找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析的方法不依赖于激励,而且可以穷尽所有路径,运行速度很快,它完全克服了动态时序验证的缺陷,适合进行大规模及超大规模ASIC电路的验证,可以节省多达20%的设计时间。静态时序分析的问题在于:它不了解电路的动态行为,因而受到电路中众多伪路径的困扰;同时,目前静态时序分析还只局限于同步电路的分析。因此设计结束之前要对全芯片进行一次动态仿真。

4 设计实例及结果

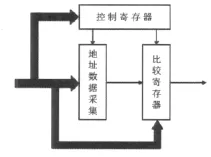

在一款硬件调试芯片设计中,采用静态时序分析技术很好地分析了芯片的时序状况。该芯片主要由地址/数据采集寄存器,控制寄存器以及比较器模块构成。分别完成对地址/数据的采集工作,在控制寄存器的控制作用下,与编程到比较器的数据进行比较,从而完成对程序执行的实时监控。其结构框图如图4所示。

该芯片的时钟频率有12M,分别完成芯片内部同步逻辑的控制工作。从整体上说,该款芯片属于同步电路,因此,应用静态时序分析工具来对其进行时序分析是一种很好的选择。在分析的时候,存在的问题是复位信号经过两级同步电路同步后,由于同步寄存器之间几乎没有电路,因此出现了HOLD TIME的违背情况。这可以在后端布局布线的时候予以解决。

图4 硬调试芯片总体框图

在芯片版图(layout)设计前,所有时钟网络必须设置 set-don’t-touch-network 和 set-ideal-net,以确保不影响后端版图设计中时钟树的设计及版图设计。待版图设计完毕后,抽取出SDF文件和SPEF文件,然后在静态时序分析工具中进行反标门级网表,进行静态时序分析。在版图设计中,绝大多数(hold)错误,必须通过手工插入缓冲区解决。对于时钟路径的处理,对最小时钟脉宽分析,通过set-min-pulsewidth分析;对setup timing和hold timing的分析,通过report_timing命令来分析,还可以用report_constraint–all_violators命令来检查所有时序上的违背情况。

5 结束语

采用UMC公司0.35微米CMOS标准单元库(Faraday FS8000A 0.35微米library),逻辑综合工具为Synopsys Design Compiler,ATPG产生工具为Tetra-MAX静态时序分析工具采用Prime Time。通过对全芯片进行静态时序分析,芯片的时序状况良好并为设计人员所把握,为后续环节的处理提供良好的依据,为整个芯片的成功设计提供了坚实的基础。

[1] Benkoski J,Vanden Meersch E,Claesen L J M,et al.Timing Verification Using Statically Sensitizable Paths[J].IEEE Trans on Computer2Aided Design of Integrated Circuits and Systems,1990,9(10):1073-1083.

[2] Prime time Workshop.Synopsys Customer Education Services[EB/OL].http://www.synopsys.com.

[3] 吕宗伟,林争辉,张镭.数字集成电路的时序分析[J].微电子学,2001,31(2):126-129.