基于FPGA和VHDL的序列检测器设计

李 瑞,孙显龙,刘宝娟

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.沈阳工业大学,沈阳110178)

1 引言

序列信号是由0,1组成的脉冲序列,在数字通信、雷达和遥测领域应用很广。为了保证信息的可靠传输,一般需要在发送端加入固定的同步码组,而在接收端则需要检出该同步码组。接收端采用的序列检测器就是一种用来检测一组或多组序列信号的电路。对于设计序列检测电路来说,有传统的经典设计方法,即根据设计要求画出状态图,列出状态转换表,通常用这个表对状态图进行化简,再从状态转换图画出电路状态和输出的卡诺图,用以求出驱动方程和输出方程,最后画出电路。这种传统的脉冲序列检测器的设计方法,通过组合各种分立元件来实现各个状态之间的转换,不仅开发周期长,设计修改成本高,而且可移植性差。随着通信技术的发展,对脉冲序列信号检测的要求越来越高,传统的设计方法已经很难满足性能指标要求。

本设计基于现场可编程门阵列(FPGA),以Xilinx公司的Spartan-3E系列FPGA芯片XC3S100E为平台来实现和验证序列检测器的功能,系统集成度高,与传统的设计方法相比,减少了元器件的使用数量,提高了测量精度和可靠性,并利用硬件描述语言VHDL编程,优化了设计,提高了效率,具有在线可编程和易于功能扩展、升级的优点。

2 利用状态图法设计序列检测器

序列检测器是具有能识别任意一串二值信号中某特殊码组功能的逻辑电路。序列检测电路在序列信号正常工作时,如果检测到待测码组,则电路输出识别信号。设计序列检测器的关键在于获取正确的状态转移图。为了减少错误检测的概率,序列检测器应该预置起始状态。

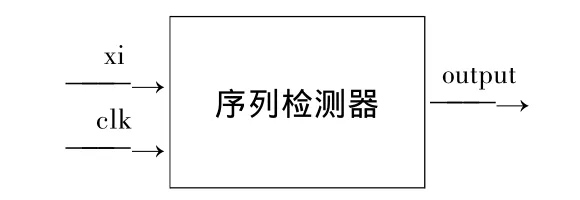

本设计的序列检测器能够从连续收到的一组串行码流中检出同步码组:1110010,同时输出检测结果标志信号。由此可知,序列检测器应该有2个输入信号和1个输出信号。输入信号一个是二进制串行信号xi,另一个是时钟信号clk。输出信号是检测结果标志信号output,其值为高电平‘1’,表示检测到同步码组;其值为低电平‘0’,表示没有检测到同步码组。序列检测器电路框图如图1所示。

图1 序列检测器电路结构框图

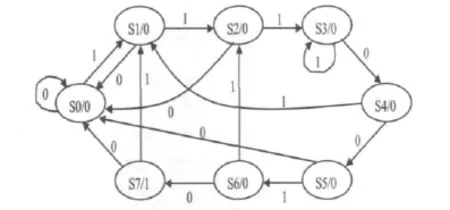

序列检测器每收到一个符合要求的串行码,就需要一个状态进行记忆。因为电路要求检测的同步码组是1110010,有7位,电路需要记忆的输入信号有1,11,111,…,1110010 等7 种,加上初始状态,即没有收到一个有效码,共8种状态。设检测器的初始状态为s0,s0是收到‘0’时的状态,检测器电路共需要8种状态(s0~s7)。用摩尔状态机来实现8种状态的转换关系,状态转移图如图2所示。图中圆圈内为当前状态和输出标志信号output的取值,箭头旁边标的数字为输入信号xi的取值。

图2 序列检测器电路状态转移图

3 利用ISE软件实现序列检测器

ISE(Integrated Software Environment)是Xilinx公司提供的FPGA/CPLD高性能设计开发集成环境,其界面友好,使用便捷。在ISE上可以完成输入(Design Entry)、综合(Synthesis)、实现(Implementation)、验证(Verification)、下载(Download)等工程设计流程,使设计者能方便地进行设计输入、快速处理和器件编程。本设计利用ISE 9.1i开发软件来实现序列检测器,下面详细介绍设计流程。

3.1 设计输入

设计输入包括原理图、状态机、波形图、硬件描述语言(HDL)等图形或文本输入方法,是工程设计的第一步。ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(State CAD)、原理图编辑器(ECS)、IP核生成器(Core Generator)和测试激励生成器(HDL Bencher)等。目前在工程设计中,常用的输入方法是HDL文本设计输入法,其中广泛使用的硬件描述语言是VHDL和Verilog HDL。使用硬件描述语言的优点是利于由顶向下设计,利于模块的划分与复用,可移植性好,通用性强,设计不因芯片的工艺和结构的变化而变化,更利于向ASIC的移植。

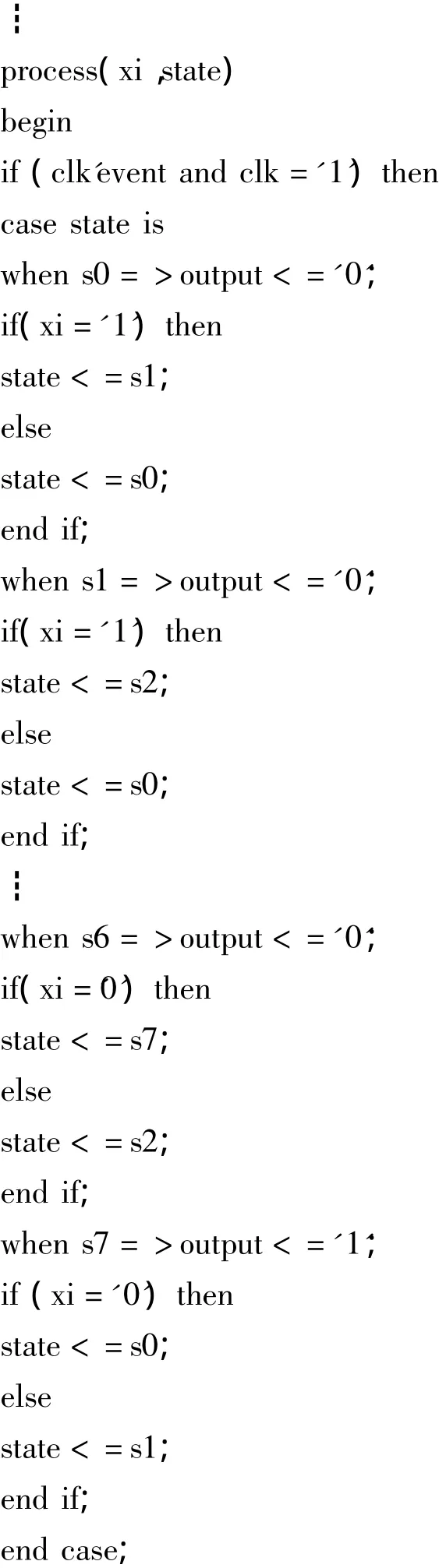

在本设计中,根据状态转移图可以很方便地写出VHDL程序,本设计采用单进程的设计方法。由于是同步信号检测,所以采用了if-then语句和clk'event and clk= '1'语句以确保在时钟信号 clk 的上升沿检测输入信号;又由于检测的是序列信号,故采用了case-when顺序语句。下面是序列检测电路的部分VHDL程序:

3.2 设计综合

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

利用Xilinx ISE自带的综合工具中的XST,将VHDL语言设计输入翻译成由逻辑门、RAM和寄存器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求优化所形成的逻辑连接,输出edf和edn等文件,供ISE布局布线器进行实现。

在综合前若指定器件,应注意器件资源和设计要求相匹配。本设计的序列检测电路仅为实际应用开发系统的部分电路,占用器件资源少,选用Spartan-3E系列FPGA芯片XC3S100E完全能满足设计指标要求。

3.3 设计实现

设计实现是根据所选芯片的型号将综合输出的逻辑网表适配到具体器件上。Xilinx ISE的设计实现过程一般分为转换(Translate)、映射(Map)、布局布线(Place&Route)等3个步骤,本设计采用ISE设计工具提供的默认值来完成。

3.4 设计验证

设计验证包含综合后仿真和功能仿真等。功能仿真就是对设计电路的逻辑功能进行模拟测试,看其是否满足设计要求,通常是通过波形图直观地显示输入信号与输出信号之间的关系。通过仿真能及时发现设计中的错误,修改设计中的错误,加快设计进度,提高设计可靠性。每个仿真步骤如果出现问题,就需要根据错误的定位返回到相应的步骤更改或者重新设计。本设计的序列检测器时序仿真结果如图3所示,分析此波形可知仿真结果符合设计要求。

图3 序列检测器仿真波形图

3.5 编程下载

编程下载是设计开发的最后步骤,利用ISE中的编程工具iMPACT,将已经仿真实现的位流文件下载到开发板上的FPGA中进行在线调试,或者将生成的配置文件写入PROM器件中。最后,将配置好的FPGA器件,加入实际信号进行测试,以检查是否满足设计要求。若有错误,重回设计输入阶段进行改正,直到功能正确并满足设计指标要求为止。

4 结束语

基于FPGA使用硬件描述语言VHDL设计序列检测器的方法,具有减小电路板尺寸、易于集成到片上系统、缩小系统体积、方便修改等特点,具有很好的可重用性,可大大缩短设计周期,降低成本,提高设计的可靠性。在Xilinx的FPGA应用开发系统中,已经成功地利用本设计完成了多路脉冲序列信号检测的功能。实际使用证明,本设计为序列信号检测电路提供了一种可靠实用的方案,灵活高效且易于扩展,具有良好的应用前景。

[1] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2002.

[2] 罗朝霞.基于CPLD的序列信号检测器设计与实现[J].现代电子技术,2005(11):59-60.

[3] 徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京:电子工业出版社,2002.