基于FPGA的多通道直流电机控制器设计

易龙龙,张复春,王美玲,郝雁中

(中国人民解放军空军航空大学 航空理论系,吉林 长春 130022)

机电一体化系统中常需要产生多通道PWM信号以完成对多台电机进行协调控制,而传统控制系统仍然采用单片机内部的定时/计数器来产生所需要的PWM信号,但由于定时/计数器及IO端口数量的限制,单个单片机控制器常不能满足多通道电机并行控制的要求[1-3]。而FPGA内部程序并行运行,不同逻辑任务可同时执行,使其工作更有效率,且其具有丰富的逻辑资源和I/O引脚资源。文中采用Altera公司Cyclone II系列的EP2C8Q208芯片,采用模块化的设计方法,以四台无刷直流电机为控制对象,完成了多通道的直流电机控制器的设计,有效地缩小了设计规模,节约了设计成本。

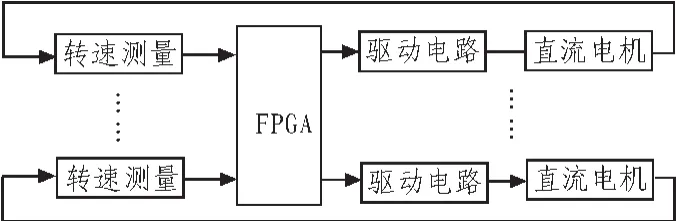

1 系统整体设计

本系统采用自顶向下的设计思路,将系统主要分为以下模块:FPGA控制模块、电机驱动模块,转速检测模块[4]。如图1所示。本系统以FPGA为控制核心,通过程序设定控制电机速度的PWM信号的占空比,由FPGA的I/O口输出给直流电机驱动电路以完成对直流电机的驱动。电机转速测量由霍尔传感器完成,反馈给FPGA计数模块,通过计数结果以决策电机控制状态。文中将着重介绍FPGA控制模块及各部分的功能设计与实现方法。

图1 系统结构框图Fig.1 Structure of the system

设计中将FPGA控制模块又分为分频模块,计数模块,并行控制模块,PWM生成模块4部分。分频模块把外部高频时钟信号降低为系统所需的标准频率。计数模块对霍尔传感器输入脉冲进行计数以完成对电机转速的测量。并行控制模块通过计数模块的计数结果决策PWM信号的占空比。PWM生成模块通过并行控制模块输出的占空比信号生成PWM波形。如图2所示。

图2 FPGA内部模块框图Fig.2 Module chart in FPGA

2 各功能模块设计

2.1 电机驱动模块

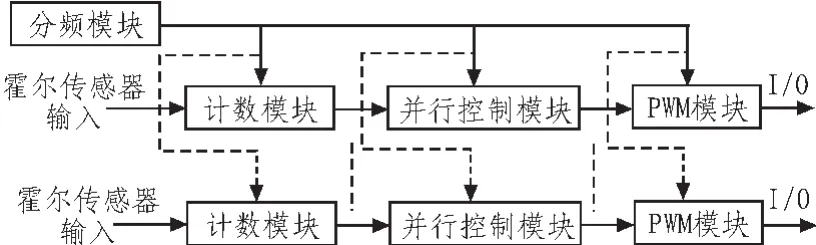

本设计中直流电机驱动模中采用ST公司生产的一种高电压、大电流电机驱动芯片L298P,内含两个H桥的高电压大电流全桥式驱动器,采用标准TTL逻辑电平信号控制。由L298P构成的脉宽调速电路如图3所示。在图中,L298P可驱动两个直流电机,可以分别控制它们的转速、转向、运转与停止。图中ENA、ENB分别控制两个电机的运转与停止,当端口为高电平时电机旋转,加低电平时电机停止旋转;由In1,In2端送入脉宽调制信号,通过改变信号的脉宽达到调速和换向的目的。M1_+,M1_-和M2_+,M2_-分别是两个直流电机的电压输入端[5]。

图3 LMD18200电机驱动电路Fig.3 Motor drive circuit based on LMD18200

2.2 分频模块

尽管可以设计中采用锁相环来完成分频器的设计,但为了节省逻辑资源,降低芯片功耗,在对于时钟要求不太严格的设计中,可自主设计进行时钟分频。本设计中采用常用的计数分频,只改变分频系数就可实现随意分频。其设计过程简单,且消耗系统资源少。在本设计中输入时钟CLK_25M为25 MHz,为了设计方便,选择分频系数设为16。通过对模块输出进行仿真,测量时钟输出频率为1.562 5 MHz,周期为640 ns满足设计要求。

2.3 计数模块

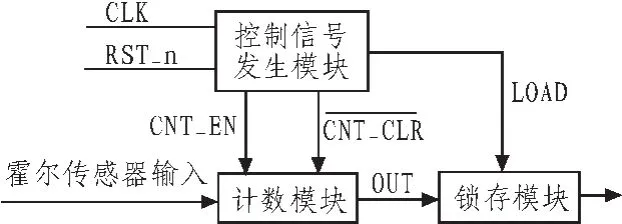

本设计中采用霍尔传感器对直流电机进行转速测量,电机每转一圈,霍尔传感器就输出一个高脉冲。测速模块其功能主要是计数,并且将所得到的数字应予锁存输出。根据单位周期内霍尔传感器输出的高脉冲数就可以估算出电机的转速。在本设计中设定每500 ms的周期内对计数结果进行一次输出并清零。根据其具体逻辑功能将利用Verilog HDL语言实现,其逻辑框图如图4所示[6]。

图4 测速模块逻辑图Fig.4 Logic chart of speed measure module

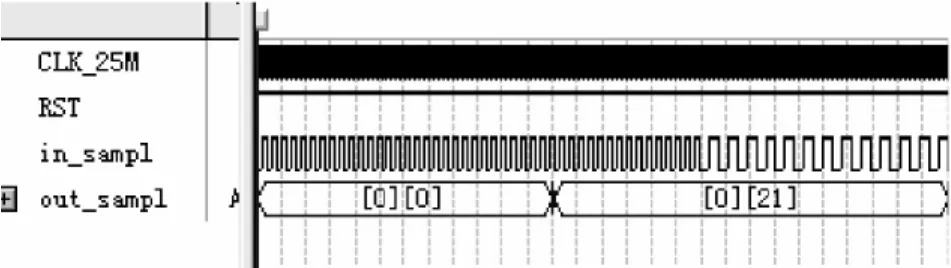

测速模块的逻辑仿真结果如图5所示,分频后系统时钟频率为1.562 5 MHz,系统复位后,开始对被测霍尔传感器输入进行计数测量,其结果为20。已经被测输入信号周期为50 ms,则频率为20,表明设计完全正确。

2.4 并行控制模块

图5 测速模块仿真图Fig.5 Simulation chart of speed measure module

并行控制模块部分是电机控制的核心部分,主要负责根据预定设置和计数模块的计数结果,按照设计目的,完成对PWM占空比的控制。由于要实现各通道电机之间互不干扰,则要求各并行控制模块与测速模块和PWM生成模块一一对应,以实现各通道并行独立控制。

2.5PWM生成模块

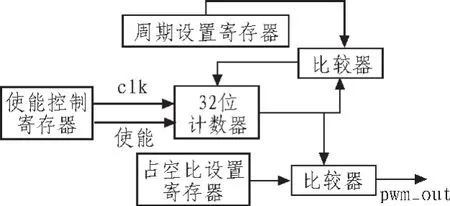

产生PWM原理:FPGA中的基准计数器用来产生类似模拟电路的三角波基准,是一个最小计数值为0,最大计数值为周期寄存器中保存的数值。PWM的任务逻辑由输入时钟CLK,输出信号pwm_out,使能位,32位计数器以及一个32位比较器组成。输入时钟作为32位计数器的时钟信号,32位计数器的当前值与占空比设定寄存器中的值经过比较器后来决定pwm_out的输出为高或为低。当前计数器中的值小于或等于占空比寄存器中的值时,pwm_out输出低电平,否则输出高电平。PWM的周期设定寄存器来设置pwm_out的信号周期,当前计数器的值等于周期设定寄存器中设定的值时产生一个复位信号来清除计数器中的值。使能控制寄存器能使时钟信号有效或无效,从而控制计数器是否工作,进而控制pwm_out是否保持当前状态不变。PWM生成模块逻辑图如图6所示。

图6 PWM生成逻辑图Fig.6 Logic chart of generate PWM

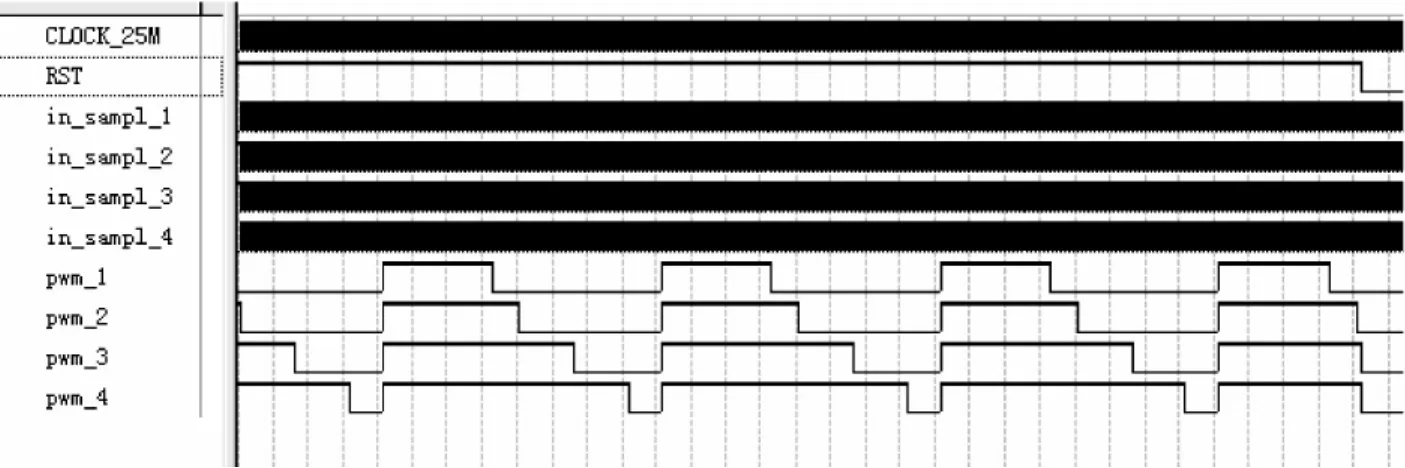

本系统共设计了4条PWM信号输出通道,每条通道的仿真波形如图8所示。通过仿真发现,当改变占空比寄存器data中的数据时,模块输出信号波形的占空比也随之发现变化,符合脉宽调制的要求。在本设计中采用时钟同步信号,只有当一个完整的PWM波输出时,才能接收data下一个数据,有效避免输出信号发生混乱,使输出信号具有良好的可预见性。

3 实验结果与分析

本实验中设计了四通道PWM以完成对4个直流电机控制。利用Quartus II自带的仿真工具对系统进行时序仿真,如图7所示。由图可以看出各个通道的PWM波的占空比与每个通道的霍尔传感器输入信号有关,各通道之间互不影响。

图7 多通道PWM时序波形图Fig.7 Timing wave of multi-channel PWM

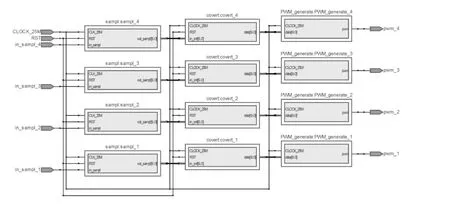

对系统综合之后,通过观察RTL逻辑视图,如图8所示,可以看出,各个通道是并行的,互不影响,符合设计要求。同时,也不难看出,系统结构较为简单,具有较强的拓展能力,能够方便地实现多通道电机的并行控制。

图8 系统RTL逻辑视图Fig.8 RTL logic view of the system

随着PWM设计通道数量的增多,所需要的片内逻辑资源也就越多,即设计PWM通道数目在一定程度上取决于FPGA片机逻辑资源的大小。

4 结束语

本设计充分利用了FPGA丰富的I/O引脚资源及程序并行运行的特点,代替了普通的单片机实现了多通道电机的控制,克服了传统PWM控制器通道少的不足,同时有效地减少了电路规模。本系统采用Quartus II自带的仿真工具进行仿真,验证了设计的可行性。虽然本设计在功能上还比较单一,在由于其具有良好拓展性,可根据实现设计要求,能够方便的对系统进行升级和维护。

[1]刘小威,翟超,颜芳.基于FPGA的LAMOST多电机控制驱动系统[J].机械与电子,2008(6):17-19.

LIU Xiao-wei,ZHAI Chao,YAN Fang.The controlling and driving system of multiple motors based on FPGA in LAMOST[J].Machinery&Electronics,2008(6):17-19.

[2]韦鲲,任军军,张仲超.应用于无刷直流电机的新PWM调制方式[J].电气传动,2005,35(2):37-40.

WEI Kun,REN Jun-jun,ZHANG Zhong-chao.The research on novel PWM method in BLDC motor[J].Electric Drive,2005,35(2):37-40.

[3]孙伟,黄大庆,闫亚辉.基于FPGA的多通道PWM控制器设计[J].江苏科技学院学报,2009,22(4):72-76.

SUN Wei,HUANG Da-qing,YAN Ya-hui.Design of multichannel PWM controller based on FPGA[J].Journal of Suzhou University of Science and Technology,2009,22(4):72-76.

[4]刘卫国,李榕,杨浩东,等.基于单DSP的多电机控制系统[J].电气传动,2005,35(8):25-28.

LIU Wei-guo,LIRong,YANG Hao-dong,etal.Control system of multiple motors based on a single DSP controller[J].Electric Drive,2005,35(8):25-28.

[5]宋健.基于L298的直流电动机PWM调速器[J].潍坊学院学报,2004,2(2):87-89.

SONG Jian.PWM speed regulator for DC motor based on FPGA[J].Journal of Weifang University,2004,2(2):87-89.

[6]常晓明,李媛媛.Verilog-HDL工程实践入门[M].北京:北京航空航天大学出版社,2005.