一款深亚微米ASIC芯片的后端设计

邹文英,徐新宇,徐 睿

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

集成电路的后端设计过程是从RTL综合到GDSII数据的实现过程,一个好的芯片版图设计为集成电路物理设计和实施奠定了良好的基础。随着集成电路工艺与设计技术的不断发展,如何缩短芯片的设计周期,同时解决芯片特征尺寸缩小、芯片规模增大、时钟频率提高以及电压降等因素使芯片物理设计复杂度越来越高的问题,已成为版图设计师需面临的主要挑战。用自动布局布线工具来完成芯片后端设计可以节省宝贵的设计时间,但后端设计绝不仅仅是自动化工具的掌握和应用,结合电路特点开发有针对性的后端设计流程对芯片的成功起着关键性作用。

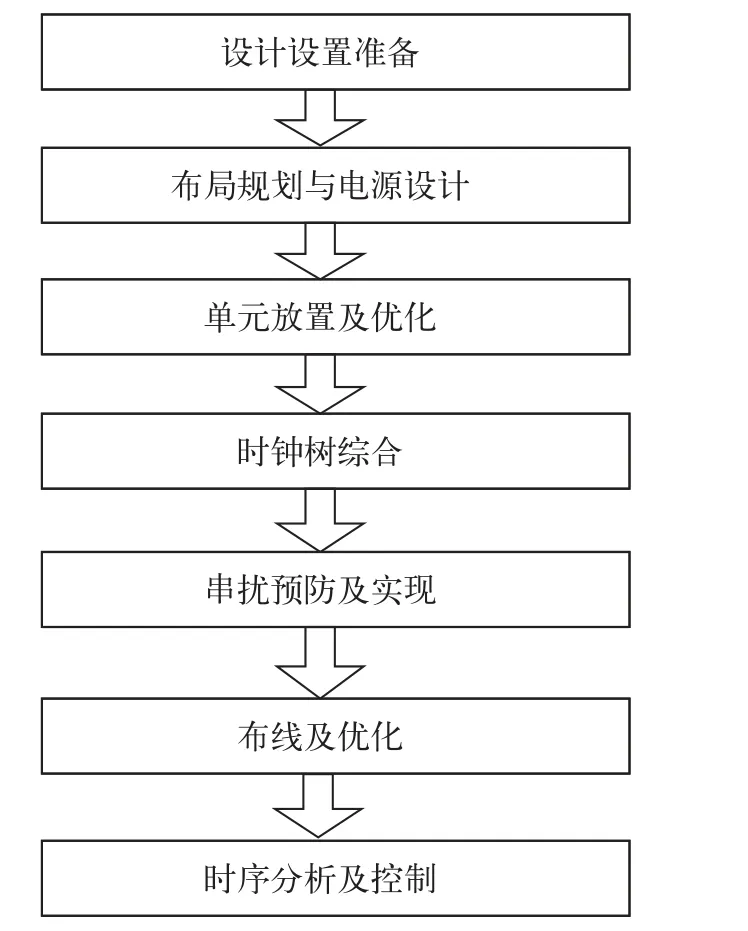

本文介绍了采用Cadence公司Soc Encounter后端工具对基于0.18μm工艺的ASIC芯片后端设计的过程,其中包括了设计之前的数据准备、布局规划、电源设计、单元放置及优化、时钟树综合、布线过程,另外还介绍了如何预防串扰和如何保证芯片时序能够满足设计要求。

2 芯片介绍

芯片是一款为用户定制的专用芯片,采用0.18μm 1P4M Salicide CMOS工艺。芯片内部集成一个双端口的SRAM IP宏单元,规模约为15万门,工作频率100MHz。电路电源电压为3.3V,电源、地引脚分为两组,其中一组为芯片内核及端口前级驱动供电;另一组为芯片上所有端口后级驱动供电。

3 芯片后端设计流程

此芯片后端设计采用Cadence公司Soc Encounter工具进行自动布局布线,芯片物理验证使用Mentor Graphics公司Calibre进行版图的DRC/LVS等检查,最后使用主流寄生参数提取工具Star-RCXT进行寄生参数提取并将抽取的网表用于门级与晶体管级的混合后仿真验证。

3.1 芯片布局布线流程

此芯片后端布局布线设计流程见图1。

3.2 设计设置准备

这一步Soc Encounter完成对芯片做布局布线之前的准备,首先创建一个设计库,然后把创建的设计库与参考库链接起来,读入网表,并将网表展开。打开设计库创建一个初始单元,然后把读入的网表捆绑到该初始单元中。

3.3 布局规划

布局规划是芯片设计的最初步骤,主要包含了芯片大小的规划、芯片输入输出单元的规划以及硬核或模块的规划等。 此芯片封装引脚240个,输入输出单元的放置位置是按照封装的要求与用户的实际情况摆放。芯片仅一个硬核,所以布局规划相对简单。

后端布局规划采取以下几个原则:(1)使关键路径上的模块放置较近,连线比较短,这样更短的连线更利于减小互连线上的寄生效应;(2)减少大的布线拥塞,以避免过长的绕线;(3)合理摆放宏单元,保证模块放置与外部引脚的安排相对应。

图1 芯片布局布线流程

3.4 电源规划及设计

电源规划是给整个芯片设计均匀的、供电充分、满足长期工作可靠性的供电网络,并解决不同电压之间的隔离问题,其中主要包括电源环(Power Ring)和电源条线(Power Stripes)规划。根据此芯片的功耗(600mW)及电源网络的电迁移、电压降方面的要求,采用了增加电源/地线的宽度及供电引脚数量的常用方法。由于芯片是采用0.18μm 1P4M Salicide CMOS工艺,根据工艺线提供的参数可知高层金属较底层金属厚,方块电阻值小,承受电流能力最强,因此设计时主要选择了高层金属作为电源环。依照这个原则,水平方向放置Metal 3,垂直方向放置Metal 4,在芯片内部水平、垂直方向每隔一定距离放置电源、地线的Stripes,以减小到达晶体管上的电压降。将芯片的电源、地环连到电源/地PAD的VDD/VSSPAD上,将Stripes连到主电源环上,将硬核的Ring 连到主电源环上,用一系列与标准单元等宽的水平电源/地线将标准单元的电源/地与主电源环和 Stripes 连接起来,就形成了芯片完整、密集的电源、地线供电“井”型网络。

为了更好地稳定电源、地线网络,在芯片设计过程中,我们自行设计了专门的片内去耦电容,片内去耦电容设计为标准单元形式,并生成布局布线工具所需要的EDA模型,纳入本芯片的布局布线流程,与标准单元及其他宏单元一起完成自动布局布线,很好地保证了设计流程的可重复性,使芯片物理设计的反复迭代简单易操作。

3.5 时钟树综合

时钟树综合是时序优化处理中最重要的一步,时钟树综合的目的是减小时钟偏斜和插入延时。在本芯片的时钟树综合中主要考虑以下几点:第一,要评价芯片时钟树综合的先后顺序,结合本芯片存在15路不同频率时钟的特点,我们评价了各路时钟进行时钟树综合的优先顺序,最终选择了把最重要的时钟放在最后综合的时钟树综合方案;第二,本芯片在逻辑设计过程中采用三模结构,因此存在不同时钟域之间的时钟平衡问题,利用Soc Encounter工具时钟树综合提供不同时钟域之间的时钟平衡处理方法,使复杂的时钟树综合问题得以解决;第三,在Soc Encounter中要明确时序参数及模型的设置;第四,为时钟网络设置专门的布线规则,我们采用了2倍于正常设计规则的线宽规则作为时钟线的连线规则以降低连线负载等负效应,采用了2倍于正常设计规则的线间距规则作为时钟线的间距规则以减小时钟毗邻连线的耦合电容及由此带来的信号间串扰;第五,不断调整约束便于更好地控制时钟树上的偏斜及插入延迟;第六,考虑RC参数的优先布线原则并进行线长优化等策略;第七,采用双通孔规则增强时钟线可靠性。

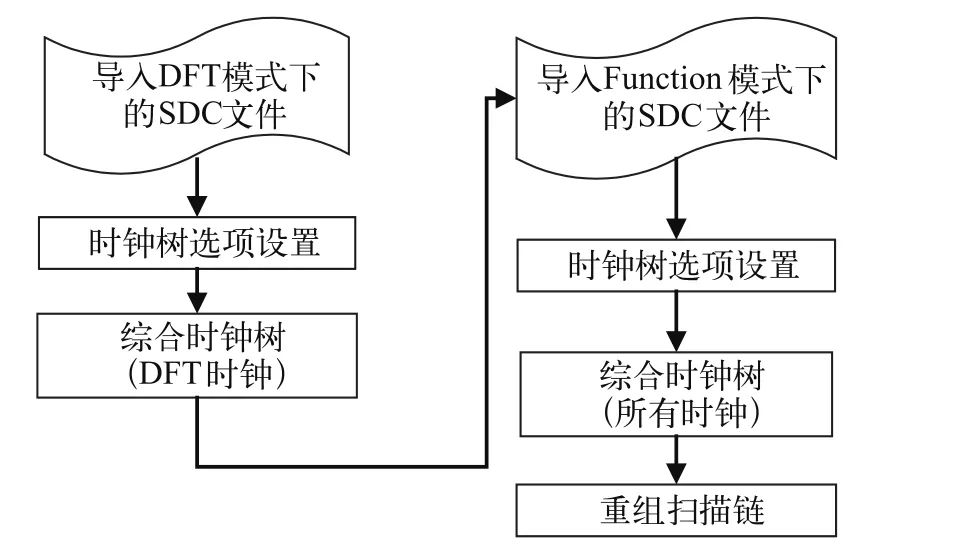

芯片中有多种工作模式,主要的两种工作模式是DFT模式与Function模式,DFT模式的优先级低于Function模式。时钟树综合时采用先综合低优先级时钟,再综合高优先级时钟的策略,即先综合DFT模式下的时钟树,再综合Function模式下的时钟树。前端设计人员把SDC文件分成DFT模式下的SDC文件和Function模式下的SDC文件,这两个文件分别导入以上两种工作模式。时钟树综合的流程示意图如图2所示。经过这种时钟树综合策略,综合后的时钟树便能很好地满足此芯片严格的时序要求。

3.6 布线及优化

布线是继布局和时钟树综合后的一项重要工作,其目的是将分布在芯片内部的模块、标准单元和输入输出(I/O)单元按逻辑关系进行互联。在自动布线的过程中分为三个步骤,即全局布线(Global routing)、详细布线(Detail routing)和布线修正(Search & Repair)。全局布线速度快、时间短,如果布线发现问题,可以及时解决调整,从而节省时间。详细布线是布线的具体实现。在布线开始时选择布线修正功能,在详细布线完成发现有错误时,布线工具会自动去搜寻并修正错误。

图2 芯片时钟树综合流程

3.7 串扰预防及实现

在0.18μm设计中,互连线的耦合电容已不再是金属线与电气地之间的耦合,而是金属连线与其毗邻连线之间的耦合,即串扰电容。串扰会给芯片带来噪声,使延迟变大,影响芯片的性能,因此信号完整性分析已经必不可少,它要解决的首要问题就是串扰。设置串绕阻止选项可以在全局布线及详细布线阶段有效阻止大部分串扰现象。

本芯片设计时采用的串扰抑制方法包括:(1)控制电源网络噪声,通过加入片上(On-Chip Decoupling Capacitance)去耦电容等各种策略以最大限度地降低芯片电源网络噪声,具体做法已在电源规划小节中介绍过;(2)增加信号线的布线间距;(3)转换到另一层连线;(4)通过设置约束,由布局布线工具实现对走线线长的控制。在此芯片中,时钟是频率最高的信号线,与其他信号线发生串扰的几率很大,所以通过有意增加时钟网络布线间距的方法,使时钟树这个大的噪声源本身的信号间噪声得到有效控制。

3.8 时序分析及控制

在芯片的设计中,时序控制一直是后端设计的重中之重。

但是在整个后端布局布线流程中,特别是时钟树综合过程极大地影响芯片的时序。在芯片时钟树结合阶段,需达到的关键性、针对性目标是最小的插入延迟、最小的时钟到达触发器或其他时序单元的时序端口的偏斜(Skew)。在CTS阶段,Soc Encounter为达到上述时钟树综合的主要目标,一定程度上会通过移动其他单元位置等途径来优化时钟树,从而影响了芯片的时序。事实上,通过反复的分析,我们已经发现在完成CTS之后,芯片的时序一定会出现一定程度的恶化现象,所以必须在CTS之后再针对芯片时序完成进一步的时序优化。由于本电路采用三模结构的特点,只能在完成CTS之后对芯片进行时序优化,其他阶段的时序优化均会改变三模结构,这是设计过程中不允许的。但是我们在其他阶段例如布线阶段、串扰优化阶段都会进行时序检查与分析。

经过以上步骤分析,我们发现还存在一些时序方面不满足的情况,我们在流程中采取了另外一种补救策略。主要过程描述如下:首先在Soc Encounter完成布局布线及时序优化,将网表及寄生参数SPF文件输出至静态时序分析工具Prime Time中,由Prime Time静态时序分析工具分析两种工作模式下的时序情况,如果出现建立、保持时间的违例,再将违例信息反馈至Soc Encounter中,借助Soc Encounter的内嵌工具在时序违例处加入修复单元,并进行ECO布线,完成后再次将网表及寄生参数SPF文件输出至Prime Time中,由Prime Time工具分析。通过这个过程的反复迭代,直至满足芯片所需的100MHz工作时序要求。

4 结束语

本文介绍了采用Cadence公司Soc Encounter后端工具对一款ASIC芯片进行后端设计的过程,是作者后端设计实践工作的一些经验总结。后端设计过程不能单纯仅靠利用工具来实现,而需紧密结合电路具体特点才能更好地实现。高度重视电源网络、时钟树、时序、串扰等各方面问题,同时认真分析和控制其他一些物理因素,如天线效应、电迁移、电压降等,并找出针对芯片的具体解决方案,方能设计出成功的芯片。

芯片采用0.18μm 1P4M CMOS工艺,在7.26mm×9.56 mm芯片尺寸内完成了一款用户定制的、工作频率100MHz、15万门左右的ASIC芯片的后端设计,流片后经过测试,芯片的功能及性能满足用户要求。

[1] 陈春章,艾霞,王国雄. 数字集成电路物理设计[M]. 北京:科学出版社,2005.

[2] Weste NHE,Harris D.CMOS VLSI Design:A Circuit and Systems Perspective,3rd Ed[M]. 2005.

[3] WANG Dong-hui, YU Qian, HONG Ying, HOU Chao-huan.SuperV Back-End Design Flow Based on Astro[J]. 2005 IEEE.

[4] Cadence User Manual[P].Soc Encounter User Guide.