基于CMOS工艺平台反熔丝FPGA实现

陶 伟,石乔林,李天阳

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

对于集成电路在卫星系统中的应用,设计人员可以选择的技术包括:专用集成电路(ASIC)、以SRAM为基础的现场可编程逻辑阵列(FPGA)、反熔丝为基础的FPGA。对于以上三种技术,设计人员需要针对特定的应用权衡取舍各种特性,以找出最佳的解决方案。

对于多数卫星的运载舱和有效负荷设备,ASIC是具有高密度、最小重量和最低功耗的解决方案,但是缺乏FPGA所提供的灵活性。而且,把设计工具成本、校验时间和非经常性工程费用(NRE)一并考虑后,ASIC也是成本最高的解决方案。以SRAM为基础的FPGA优势在于拥有高逻辑密度和高灵活性,可在卫星发射前后期修改设计,因此多用于有效负荷设备中。然而,灵活性的增加会提高系统的复杂性,并增加元件数目和功耗、降低总体可靠性。更关键的是由于其更容易受到宇宙辐射,产生单粒子效应(SEU)干扰。以反熔丝为基础的非挥发性FPGA器件比ASIC和SRAM产品具有更多优势,采用抗辐射的反熔丝FPGA,设计人员可以免除ASIC设计中那些NRE成本和工程延误风险,并且可享有只有FPGA才能提供的设计灵活性和产品快速上市的优势[1]。

目前国外对于反熔丝FPGA开展了很多研究[2~6],ACTEL等公司已经相继开发出一系列的产品。主要实现方法包括MTM和ONO熔断技术[7~8]。但由于工艺平台的限制,国内尚未见反熔丝FPGA的报道,使我国卫星和军事应用受到极大的限制。针对目前现状,本文利用普通CMOS工艺,开发出一种反熔丝技术,可满足不同应用领域的要求。

2 反熔丝单元试验

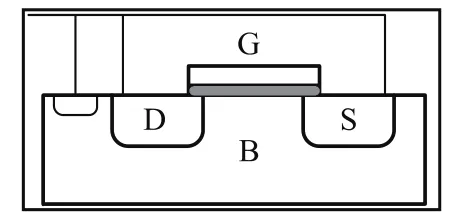

反熔丝单元利用普通MOS管结构,采用MOS管电容连接方式,将漏源和衬底连接在一起,利用高压将栅氧化层击穿,以实现熔断,如图1所示。此工艺的关键是优质栅氧化层的实现,对单元编程后的稳定性起到关键作用。

图1 反熔丝单元

我们利用现有工艺线,在工艺工程批次中制备了五种不同厚度的栅氧化层,分别为4nm、8.35nm、12.5nm、16.5nm和27.5nm。以27.5nm栅氧化层为例,利用7.5V的电压对两试验样品进行熔断。测试采用NI PXI-4130可编程电源,具体测试结果如下。

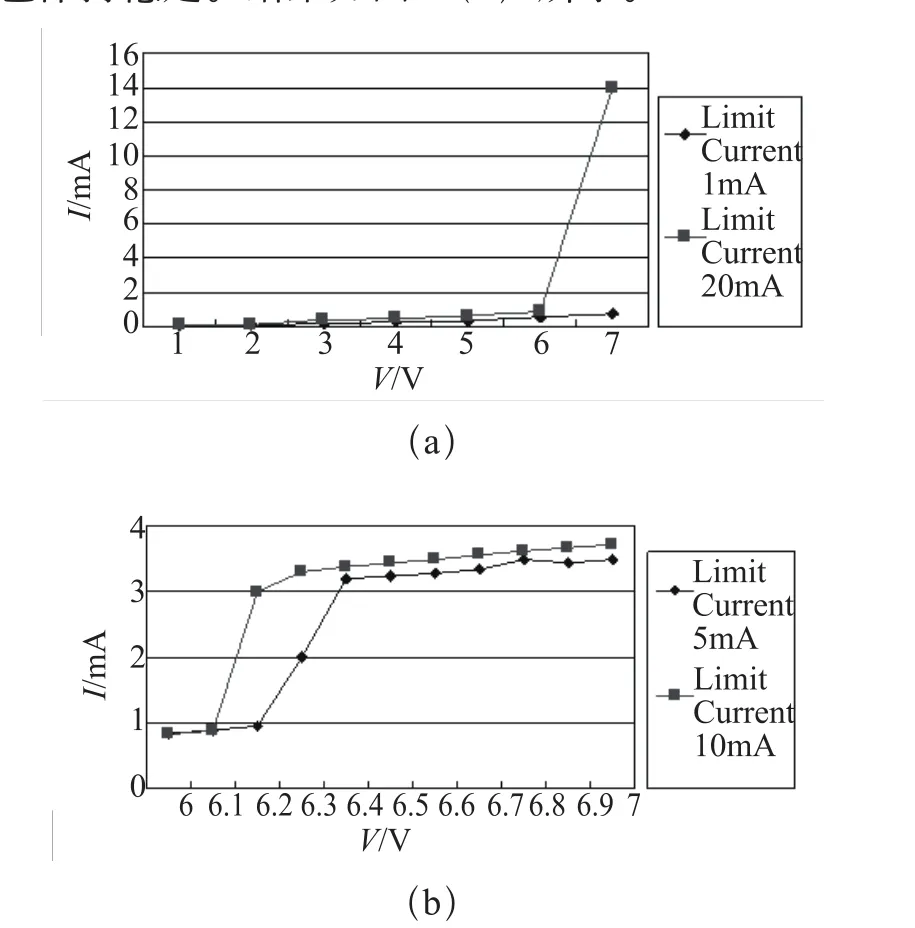

样品一:选择0~7V的电压测试范围,测试电压步长为50mV,限流1mA。在测试过程中,单元一直未熔断。将限流条件放宽至20mA,电压步长为20mV,发现在6.76V时单元被熔断,此时电流为1.15mA。此后加大电压,电阻值保持在350Ω左右,电流为14mA。结果如图2(a)所示。之后对样品一的电压测试范围调整至6V~7V,限流5mA,测试步长为10mV。熔断电压约为6.3V,此时熔断电流为2mA,熔断电阻为2kΩ,且保持稳定。将限流调整为10mA,测试步长为5mV。发现在6.2V时发生熔断,此时熔断电流达到3mA,熔断电阻为1.31kΩ,且之后也保持稳定。结果如图2(b)所示。

图2 样片一测试结果

样品二:初始测试与样品一相似,在0~7V范围内,限流1mA情况下,单元一直未熔断,将限流条件放宽至20mA,电压步长为20mV,发现在6.6V时单元被熔断,此时电流为1.23mA。此后加大电压,电阻值同样保持在350Ω左右,电流为17mA。测试曲线与图2(a)相似。调整测试方案,在6V~7V的电压范围内,限流5mA,测试步长为20mV,发现单元在6.3V左右熔断,熔断后电流为3.8mA,电阻保持在2.3kΩ左右,将限流扩大至20mA,测试步长调整为5mV,发现测试样品大约在6.4V熔断,熔断后电流为15mA,熔断后电阻保持在335Ω左右。结果如图3所示。

图3 样品二测试结果

单元熔断后,重新加0~7V电压,不限流情况下重新测试,得出以下结果:在电压正负不颠倒的情况下,熔断电压在6.2V~6.7V范围内,限流在1mA时已熔断,但电阻在6kΩ左右,随着限流增大,电阻等比例减小。而在不限流时,熔断电阻基本保持在330Ω~400Ω左右,电流保持14mA~19mA。样品一可能由于栅氧制备原因引起窗口问题,导致熔断后单元有不稳定的情况。而样品二熔断后能保持稳定。

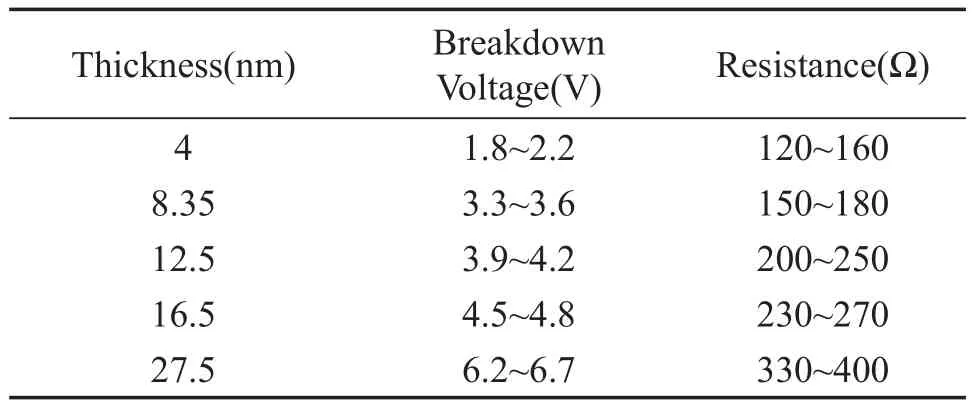

利用栅氧化层击穿技术形成的反熔丝单元,其击穿电压主要与介质层厚度有关,同时也受到制备条件及成分密度的影响。采用相同的测试方法,各种不同厚度的样品击穿电压以及击穿后电阻的大小如表1所示。

表1 各样品击穿电压及阻值

测试结果说明,与MTM以及ONO反熔丝技术相比,此结构的单元同样具有很好的稳定性与熔断特性,且不受特殊工艺的限制,能与CMOS工艺兼容,是一种理想的实现方法。

3 反熔丝阵列设计

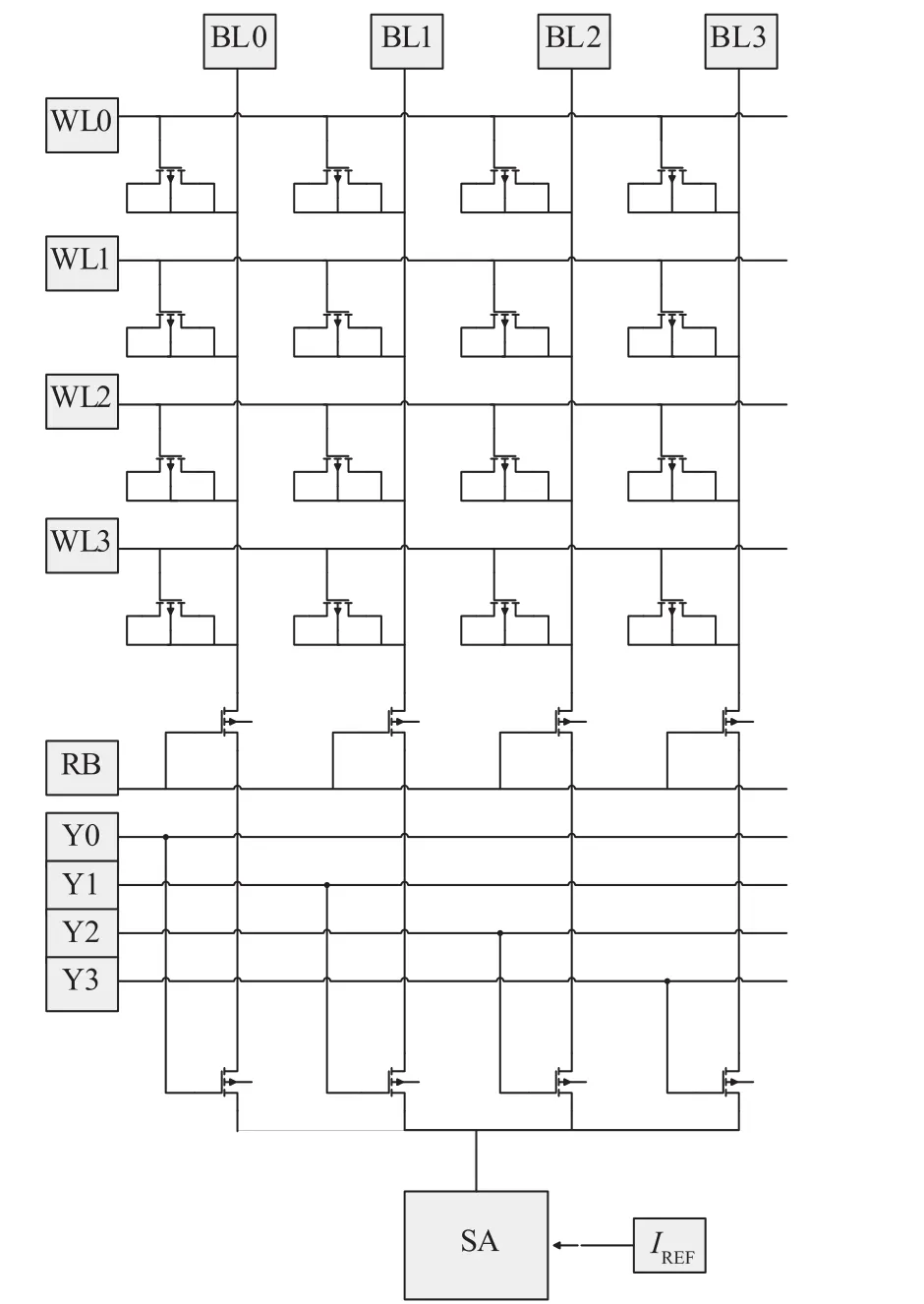

以4×4反熔丝阵列为例,如图4所示,其中WL为字线,BL为位线,RB是读允许控制端,Y端为列译码线,SA为灵敏放大器,用于将从单元读出的电流与IREF电流比较,读出数据“0”和“1”。具体工作方式为:(1)编程阶段。RB端为低电压,读操作被关闭,字线WL端接相应的熔断电压。对需要编程的位,将BL端接GND,不需要编程的位,将BL端接高电压或浮空。将MOS单元熔断,实现编程。(2)读出阶段。将RB端接高电平,使读出允许。将需要读出字的WL端接VDD,通过译码控制Y0~Y4,将对应位以电流的形式读出。将读出电流传输至小信号放大器(SA),通过与参考电流IREF的比较,读出数据“0”或“1”。整个电路简洁,编程和读出操作也易于实现,且具有高密度、低功耗的优点,方便此结构FPGA的大规模应用。

4 总结

文章在现有MOS工艺的基础上,通过对不同厚度栅氧化层击穿电压的试验和测试,找到了一种可兼容MOS工艺的反熔丝单元设计。通过试验证明了熔断后单元的稳定性,是传统的、需要特殊工艺支持的反熔丝FPGA 的一种良好的替代。并且具有电路简洁、编程和读出操作易于实现、高密度、低功耗的优点,方便了此结构反熔丝FPGA的大规模应用,不但满足了军事和航天领域的需求,也为以后反熔丝产品的实现提供了有价值的借鉴。

图4 反熔丝阵列设计

[1] Ken O'Neill. Antifuse FPGA Technology Best Option for Satellite Application[J]. 电子产品世界,2005,10:92-94.

[2] McCollum J. ASIC versus antifuse FPGA reliability[J].IEEE Aerospace conference, 2009:1-11.

[3] Nejad R J, Rickey P A, Konadu K, et al. Radiation Characterization of a Hardened 0.22μm Anti-Fuse Field Programmable Gate Array[J]. IEEE Transactions on Nuclear Science, 2006, 53(6):3525-3531.

[4] Rezgui S, Wang J J, et al. SET characterization and mitigation in RTAX-S antifuse FPGAs[J]. IEEE Aerospace conference, 2009:11-14.

[5] Daichi Kaku, Toshimasa Namekawa, et al. A Field Programmable 40-nm Pure CMOS Embedded Memory Macro using a PMOS Antifuse[J]. Solid-State Circuits Conference, 2009:217 - 220.

[6] Wlodek Kurjanowicz, Ottawa, Split-channel Antifuse Array Architecture:USA 7,402,855B2[P/OL]. 2008-06-22[2005-05-06].

[7] Yoshida, et al. Method of Manufacturing Semiconductor Integrate Circuits:USA 3,634,929[P/OL]. 1972-01-18[1969-10-29].

[8] Mohsen, et al. Programmable Low Impedance AntifuseElement:USA 4,823,181[P/OL].1989-04-18 [ 1986-05-09].