ADV7180在图像采集嵌入式系统中的应用

廖 诤,张 攀,颜 悦

(国家知识产权局专利局 专利审查协作北京中心,北京 100190)

视频信号的数字化应用已扩展到多媒体、数字电视、图像处理、视频监控、可视电话、视频桌面系统等广泛的领域,因此对小型化的视频信号采集及处理系统的需求也日益增加,针对这种需求,本文介绍了一种以ADI公司的ADV7180视频采集芯片、TI公司的TMSC6415 DSP[1-2]和Xilinx公司的XQV300 FPGA芯片组成的视频采集处理系统。

该视频采集处理系统的视频采集功能主要由ADI公司的ADV7180视频采集芯片来完成。由于视频信号中除了包含图像信号之外,还包括了行同步信号、行消隐信号、场同步信号、场消隐信号等,因此本系统中采用了ADI公司的ADV7180芯片,该芯片将一个10位ADC、3路具有抗混叠滤波器的视频输入通道、自适应梳状滤波器、CTI/DNR视频增强器、自动增益控制(AGC)等非常复杂的视频信号A/D转换电路集成到一块芯片中,支持NTSC/PAL/SECAM的解调及自动检测,可输入CVBS、Y/C和YPrPb等类型的视频信号,输出与8 bit ITU-R BT.656接口标准兼容的YCrCb 4∶2∶2的视频信号以及水平、垂直、场同步信号。应用ADV7180视频采集芯片不但降低了整个视频采集处理系统的设计复杂度,而且提高了该系统的可靠性。

该视频采集处理系统的视频处理功能主要由TI公司的TMSC6415 DSP芯片来完成。该DSP芯片为600MHz主频的高性能定点数字处理器,采用了数据总线与程序总线分开的哈佛结构,配有独立的乘加器,可通过EDMA方式大大提高数据块的传输速度,并可采用流水线技术及单指令多数据流技术,使指令执行速度大大提高,且具有低功耗的特点,因此非常适合于本文介绍的小型视频采集处理系统的需要。

在该视频采集处理系统中,通过FIFO实现了ADV7180与DSP之间的连接,该FIFO功能是由Xilinx公司的XQV300 FPGA芯片来完成的。

1 系统硬件组成

视频采集处理系统的硬件框图如图1所示。

首先,DSP芯片串口1的FSR1及FSX1管脚,分别与ADV7180芯片的I2C控制器中的SCL及SDA信号线相连,通过DSP对ADV7180进行配置和控制,使其可以自动检测输入的模拟视频信号,并进行A/D变换;然后,ADV7180通过其P8到P15管脚,向FPGA芯片实现的FIFO,输出8 bit宽度的A/D转换后的数据,当数据采集到FIFO半满时,向DSP的外中断7发出中断请求,通知DSP读取FIFO中的数据;最后,DSP以32 bit宽度由EMIFA读取FIFO中的数据,通过EDMA方式存入DSP内存,进行视频压缩编码,并将处理后的数据从串口0输出,或以文件形式存入SDRAM中。

E2PROM及Flash可在整个系统上电时分别对FPGA和DSP加载程序。

2 系统软件组成

下面对应于上述的硬件系统,介绍相应的软件系统组成。该软件系统主要包括DSP程序和FPGA程序两部分,其中DSP程序在TI公司的CCS开发环境中应用C语言进行开发,主要完成设置、启动ADV7180,接收FIFO数据并处理的功能;FPGA程序在Xilinx的ISE开发环境中应用VHDL语言进行开发,主要完成数据拼组、亚抽样的功能。其软件系统框图如图2所示。

首先,DSP程序申请用于存放输入视频数据的乒乓缓冲区,初始化相应的EDMA通道,设置串口1的工作模式为通用I/O,设置串口0的工作模式为标准串口,并初始化定时器1和外中断7。

然后,DSP通过串口1虚拟I2C总线时序[2-3],对ADV7180芯片进行工作参数设置,并通过定时器1的输出管脚向ADV7180发送开始工作信号。

接着,FPGA程序主要实现FIFO的功能,接收经过ADV7180模数变换的数据,根据DSP的EMIFA位宽将4个8-bit作为一组,同时为了提高DSP程序中图像的压缩率,在FPGA程序中增加一个亚抽样的过程,就是将ADV7180产生的、原为4∶2∶2的YCbCr格式的数据亚抽样为4∶1∶1,这是因为人眼对亮度信号的敏感程度远远高于对色度信号的敏感程度,经过这样的处理,图像的质量变化并不很大,但数据量却减少了1/4,既提高了压缩率,又节省了DSP片内的RAM。

当FPGA中的数据达到半满后,会向DSP的外中断7发出中断请求,DSP外中断7的中断服务子程序对其进行响应,通过EDMA方式读入从EMIFA传入的FIFO数据,并存入DSP的内存中。

最后,DSP对内存中的视频数据进行压缩编码等处理,并将结果通过串口0输出,该部分程序可以根据需要采用不同的图像压缩编码算法,以适应不同视频源、压缩比、传输介质等的要求。

3 虚拟I2C设置ADV7180

前面提到了虚拟I2C总线技术,在通常的视频采集系统中,需要诸如ADV7180之类的视频采集芯片作为模拟视频前端,而视频采集芯片的初始化一般通过I2C总线接口来完成,然而,目前的单片机和DSP器件大多都不带有I2C总线接口,因此,需要采用虚拟总线技术来模拟实现I2C总线功能。本节中就对虚拟I2C总线技术[3]进行一个简要介绍。

I2C总线既可用于构成多主系统,又可工作在单主方式下。本系统采用单主方式,DSP作为主设备,ADV7180作为从设备,利用DSP多通道缓冲串口1(McBSP1)的通用I/O模式,根据图1的硬件系统框图和DSP串口通用输入输出管脚设置可以查出,通过控制其管脚控制寄存器(PCR)的FSXM,FSRM,FSXP和FSRP这4位,就可以模拟出I2C总线上SDA和SCL的时序,从而实现DSP对ADV7180 I2C控制寄存器的写入和读出。

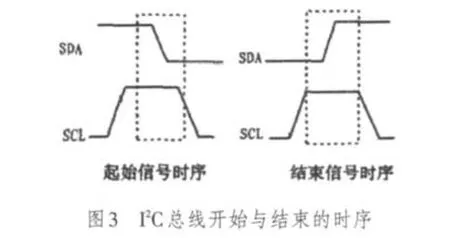

在DSP程序中,I2C总线的开始与结束的时序如图3所示,相应的程序如图4所示。

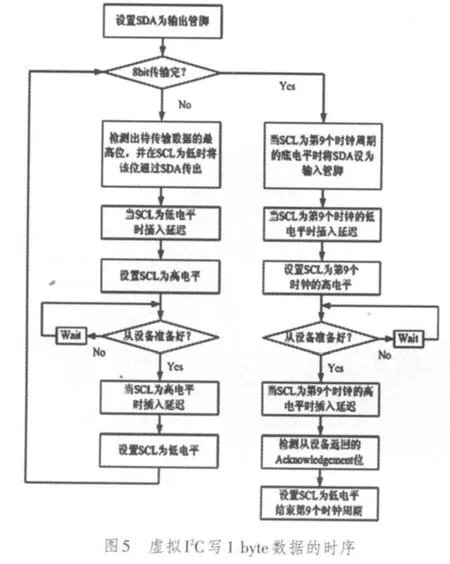

通过虚拟I2C向从设备写入1byte的操作步骤如图5所示,通过虚拟I2C由从设备读出1 byte的操作步骤与之类似。

在实现了虚拟I2C的读写操作后,DSP就可以对ADV7180的I2C控制寄存器写入控制字并回读该控制寄存器中的值,其中写序列和读序列的时序如图6所示。

当DSP对ADV7180进行写操作时从地址为0x40,对其进行读操作时从地址为0x41。

通过本节所述的方法,可成功实现DSP对ADV7180的参数设置,使其可按需要对输入视频数据进行A/D转换。

4 运行结果

整个视频采集处理系统在经过软硬件调试后,工作正常。首先,DSP程序通过虚拟I2C总线,回读ADV7180 I2C控制寄存器中的状态寄存器(0×10),可以看出视频信号已经锁定(in lock),并且成功检测出输入视频信号的格式为PAL B;然后,以文件形式保存传入DSP内存的原始数字视频信号数据,再利用通用的YUV播放器进行观察,可看到清晰的彩色图像;最后,将采用某种压缩编码算法处理后的视频数据经过串口0输出,与另一台计算机的串口相连,在该计算机上运行相应的解压解码算法程序,看到输出后的彩色图像。

5 结论

综上所述,本文中介绍的基于ADV7180视频采集芯片和TMSC6415 DSP的视频采集处理系统,工作稳定可靠,具有体积小、功耗低、通用性强等特点,可通过DSP对ADV7180进行不同设置,来满足不同输入视频源的需要,并可通过DSP中图像处理算法的不同,来满足不同图像压缩率和数字信号输出码率的需要。该系统可应用于数字便携照相机和PDA、视频通信、个人多媒体录放机、多媒体手持设备、汽车安全系统等广泛领域。

[1]周霖.DSP通信工程技术应用[M].北京:国防工业出版社,2004.

[2]李方慧,王飞,何佩琨.TMS320C6000系列DSPs原理与应用[M].北京:电子工业出版社,2003.

[3]张克满,何格夫.用虚拟I2C总线技术实现SAA7111的初始化[J].国外电子元器件,2005(1):26-29.