遥感图像采集中的SDRAM图像缓存技术

刘妍妍,李国宁,金龙旭

(1.长春理工大学电子信息工程学院,吉林 长春 130022;2.中国科学院长春光学精密机械与物理研究所,吉林 长春 130033)

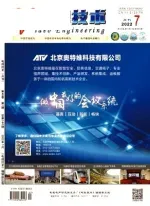

随着卫星遥感相机朝着高分辨力、宽覆盖等方向发展,急剧增加的遥感图像数据量给存储及传输带宽带来了巨大压力,星载遥感图像采集和缓存是空间技术应用中的关键技术之一[1-2]。同步动态随机存储器SDRAM的控制器设计虽然比较复杂,但是方式灵活,可以最大限度地节约资源,达到更高的图像数据传输率[3-6]。考虑到大面阵CCD的图像数据量非常大且采用4个象限同时输出,采集得到的图像要进行数据重组,因此在进行图像压缩和显示之前必须要缓存图像数据。图像缓存在整个系统起着重要的衔接作用,面阵CCD485的有效像素为4 k×4 k,每一个像素量化后的数据位宽为8 bit,因此一帧图像的数据量为16 Mbyte,这么大的容量非常适合用SDRAM来实现。本文中使用了2块三星(SAMSUNG)公司生产的SDRAM作为图像缓存,型号为K4H560838D,存储容量为32 M×8 bit,该系统每帧能缓存的最大数据量可达到32 Mbyte,系统硬件框图如图1所示,系统主要由CCD视频信号处理器、核心控制器FPGA、图像缓存SDRAM、高速并行数字差分接口、高速图像采集卡和图像存储和显示等组成。

1 SDRAM简介

图1 系统硬件总体框图

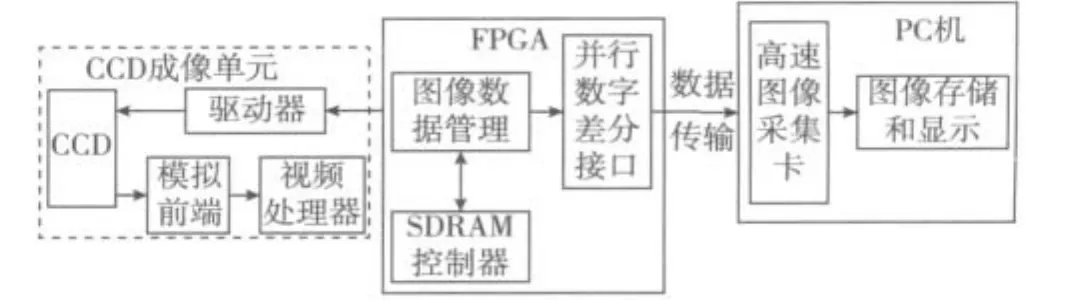

SDRAM的存储单元由一个MOS管和一个容量较小的电容器组成,如图2所示。它的存储数据的原理主要是利用电容器的电荷存储效应来实现。当电容充有电荷,即充电的电容时,呈现高电压,在数字电路中,相当于存有逻辑“1”,反之,当电容没有电荷,即放电的电容时,呈现低电压,在数字电路中,相当于存有逻辑“0”,MOS管相当于开关,所以,电容器上不能长期地保存存储的电荷,因此必须定期给电容补充电荷,以免数据丢失,这个过程即为对SDRAM的存储单元的刷新或再生的操作。SDRAM的4种基本操作为初始化、刷新、读和写操作。

图2 SDRAM存储单元的基本结构

2 设计SDRAM控制器

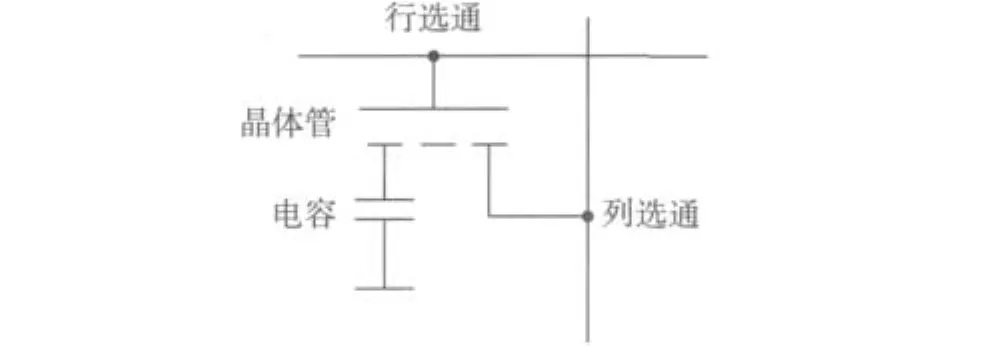

该SDRAM控制器与外部接口信号SDRAM结构框图如图3所示,使用2片三星公司生产的K4H560838D作为数据缓存。

图3 SDRAM控制器与外部接口信号

SDRAM控制器左端的接口信号是与系统主机相连接的信号,其中,SYS_CMD为系统主机发给SDRAM的指令信号,SYS_CLK为系统主机的时钟信号,SYS_CMDACK为SDRAM接收到系统主机指令后返回给主机的信号,SYS_ADDR为SDRAM控制器的地址信号,SYS_DATAIN为写入SDRAM控制器的存储数据信号,SYS_DATAOUT为系统主机接收SDRAM控制器的数据信号,SYS_DM为系统主机给出的字节屏蔽信号,控制器右端的接口信号是直接与SDRAM对应管脚相连的信号,ADDR为控制器送给SDRAM的地址信号,DQ用于连接SDRAM的数据线,BA为SDRAM的块选择信号,RAS和CAS分别为SDRAM的行地址和列地址使能信号,CS和WE分别为SDRAM的片选和写信号,CLK和CKE分别为SDRAM的时钟和时钟使能信号,DQM为SDRAM的数据掩码。

SDRAM指令即CMD指令解析如表1所示。

表1 SDRAM指令解析

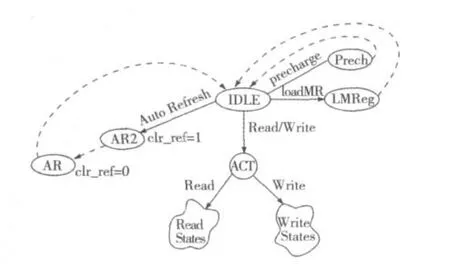

SDRAM控制器的状态机如图4所示,SDRAM控制器平时处于IDLE状态,根据系统指令进入PRECHARGE,LOAD_MR,AUTO_REFRESH和读写状态。

图4 SDRAM控制器的状态机

其中,在执行LOAD_MR指令时,是将寄存器的数据存入到SDRAM的模式寄存器中,从而控制SDRAM的工作模式。寄存器预设用户定义的SDRAM的刷新周期。其中,读写状态如图5所示。

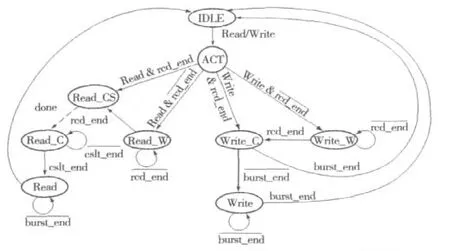

图5 SDRAM控制器的读写状态

对读写操作,控制器先进入ACT(行有效)。执行写操作时,控制器需要检查RAS_TO_CAS delay结束标志和突发结束(burst end)标志。写操作需要3种状态:WRITE_W,WRITE_C和WRITE。状态WRITE_W用于查询rcd_end标志,状态WRITE_C发送第一个数据和WRITE指令到SDRAM中,状态WRITE继续发送数据直到突发结束。执行读操作时,除了检查RAS_TO_CAS delay和突发结束标志以外,控制器也需要检查CAS latency。读操作需要4种状态:READ_W,READ_CS,READ_C和 READ。状态READ_W用于查询rcd_end标志,状态READ_CS满足RAS_TO_CAS delay,状态READ_C发送READ指令到SDRAM中,状态READ继续读取数据直到突发结束。

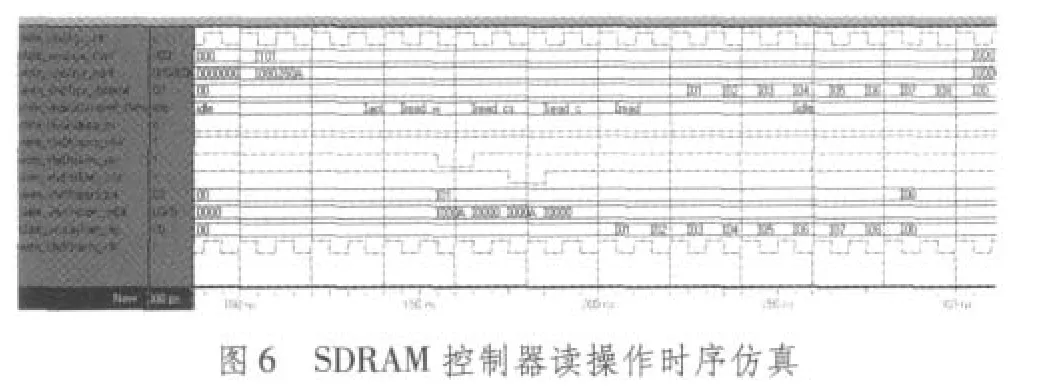

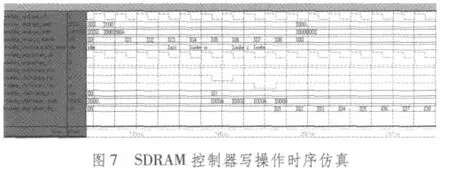

3 SDRAM控制器的读写操作仿真时序

由于本系统采用的SDRAM为K4H560838D,存储容量为32 M×8 bit,分为4个Bank,每个Bank容量为8 M×8 bit,每个Bank的行地址和列地址分别为13位和10位,即每个Bank是由8 k行和1 k列的存储单元阵列组成。SDRAM控制器设定SYS_ADDR共25位地址信号,其中SYS_ADDR[24:23]映射到SDRAM 的4 个Bank,SYS_ADDR[22:10]映射到 SDRAM 的行地址,SYS_ADDR[9:0]映射到SDRAM的列地址。SDRAM控制器的读写操作仿真时序如图6和图7所示,图中SYS_ADDR为0x080280A(0100000000010100000001010),由上面映射可知,分别是对第2个Bank中起始行地址为0x0A(0000000001010),起始列地址为0x0A(0000001010)的存储单元进行8 byte的突发读写操作。由于行地址和列地址共同占用SDRAM_ADDR,所以采用 SDRAM_RAS和SDRAM_CAS信号来区分SDRAM_ADDR上是行地址还是列地址,两者均为低电平有效。contrl_state为SDRAM控制器的内部状态,状态转移完全符合图4和图5。

4 结论

本文首先介绍了SDRAM的存储原理和基本操作,提出了一种能满足遥感图像采集中的SDRAM图像缓存技术,对于面阵大小为4 k×4 k,每一个像素量化后的数据位宽为8 bit,一帧图像的数据量为16 Mbyte的遥感图像实时采集和缓存。实验结果表明,采用SDRAM作为高速、大容量的中间缓存优势相当明显,而且在FPGA中设计,对SDRAM的访问速度和存储位宽改变非常方便。

[1]张浩,张育林.卫星遥感图像数据压缩质量评价研究[J].中国空间科学技术,2007(2):55-60.

[2]刘荣科,张晓林,廖小涛.星载遥感图像压缩编码技术综述[J].遥测遥控,2004,25(2):7-12.

[3]王明富,杨世洪.大面阵CCD图像实时显示系统中的SDRAM控制器设计[J]. 计算机应用,2009,5(5):1449-1451.

[4]苏海冰,吴钦章.用SDRAM在高速数据采集和存储系统中实现海量缓存[J]. 光学精密工程,2002,10(5):462-465.

[5]吴子彧,余松煜,管云峰,等.基于卷积交织的SDRAM控制器的设计[J]. 电视技术,2006,30(12):29-31.

[6]刘维亚,杨旭,刘超,等.基于SDRAM的实时视频传输系统存储管理[J]微计算机信息,2009,25(1-2):292-293.