基于Cadence的源同步时序仿真

朴卫杰,程 号

(西安电子科技大学电子工程学院,陕西 西安 710071)

随着电子技术和IC技术的不断进步,数字系统的时钟频率越来越高,信号skew也越来越陡,PCB系统已不再是以往设计中仅仅只是支撑电子元器件的平台,而变成一个高性能的系统结构,PCB发展到集合了电子、热、机械等多学科的专业学科技术。

IBIS模型的高速PCB板级信号完整性分析,可以在设计阶段最大化解决潜在的SI问题,在高速系统设计中具有较高的指导意义。基于IBIS信号完整性的仿真由于加入了性能预测分析和设计实施约束等可控点,因此,当系统性能不能满足要求时,问题定位和分析都有章可循,与传统的PCB的设计相比,缩短了设计周期,又降低了设计成本。

1 基于Cadence的信号完整性仿真

1.1 IBIS模型介绍

IBIS是采用I/V和V/T表的形式来描述IC器件的输入、输出和I/O Buffer行为特性的文件,并且用来模拟Buffer和板上电路系统的相互作用。IBIS模型的分析精度主要取决于I/V和V/T表的数据点数和数据的精确度。IBIS的精确度对于系统级的分析而言已经足够,同时相对于SPICE模型仿真所需要的时间相比则大大缩短。IBIS模型可用于系统板级或多级信号完整性仿真,包括串扰、反射、震荡、上冲、下冲、不匹配阻抗、传输线分析、拓扑结构分析,IBIS尤其能偶对高速震荡和串扰进行准确精细的仿真,它可以检测最坏情况的上升时间条件下的信号行为及一些用武力测试无法解决的情况。关键在于半导体厂商在不透露之间的知识产权的同时为客户免费提供这种模型,这样对开发人员而言可以节约一些开发成本。总之IBIS模型以其方便、快捷以及一定的精确度,得到越来越多的应用。

1.2 Cadence信号完整性的仿真

“第一时间推出产品”已经成为各个公司在竞争激烈的市场中生存的关键,所以在产品设计初期识别、预防和改正设计错误,可以防止电路板出错,这种操作模式至关重要。通过前仿真来决定系统的设计方案,可以有效地解决困扰高速设计中SI问题,将后续PCB设计风险降到最低,这就是PCB SI和SigXplor工具需要完成的任务。Cadence公司的PCB SI和SigXplor设计工具,以仿真实际物理设计中的各种参数,对系统中的信号完整性和时序(Timing)、串扰(Crosstalk)和EMI问题进行量的分析。通过仿真可以验证设计方案的可实现性,根据设计对SI于时序要求选择关键元器件、优化系统时钟网络及系统各部分的延迟、选择合理的拓扑结构,调整PCB的元器件布局。

Cadence公司的PCB SI和SigXplor设计工具为高速PCB的仿真提供了有效的手段,在系统设计时通过仿真可以解决很多棘手的问题,增加了对系统设计方案的可预见性,配合后端的PCB设计与后仿真,能解决大部分高速信号完整性问题。

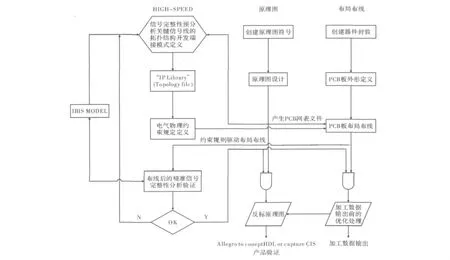

基于Cadence Allegro设计工具的PCB设计流程 如图1所示。

图1 Cadence高速设计流程

2 源同步介绍

在过去的十几年中,高速数据总线一直在不断发展,它们不仅变得更快,而且还在改变系统对数据的定时方式。为增加数据的吞吐量,源同步传输方式应运而生。

源同步技术是指数据和时钟/锁存并行传送。源同步接口信号工作在相对的时钟系统下,这样对全局系统时钟的skew要求就可降低,传输速率主要由数据和时钟/锁存信号间的skew决定,这样系统就能达到更高的传输速率。

在源同步时钟系统中,由于数据和源同步时钟是同步传输的,所以只有保证两个信号的飞行时间完全一致,才能达到源同步的设计要求。这就要求整个系统在时序上的稳定性,完全体现在数据和同步时钟信号的匹配程度上,包括传输延时的匹配,器件性能的匹配等。只有数据信号和同步时钟信号完全匹配,才能保证系统时序完全正确。

3 源同步的时序分析

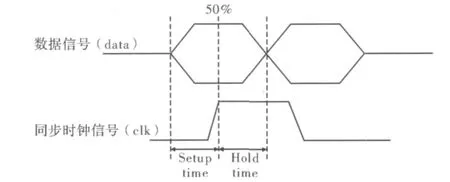

源同步时钟信号必须要有一定的建立时间和保持时间,主要体现在数据信号和同步时钟信号之间的时序要求上。最理想的情况是同步时钟信号能在数据信号的中央部分读取,如图2所示,这样才能保证最充分的建立和保持时间。

图2 理想的源同步数据传输时序图

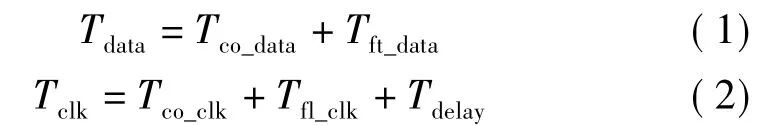

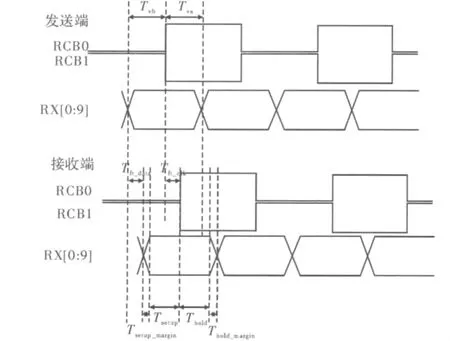

源同步时钟系统设计中最重要的一点就是保证data和同步时钟信号之间的skew最小,下面通过时序图3可以得出源同步的时序关系

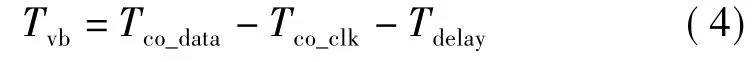

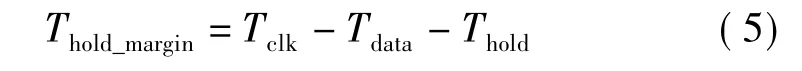

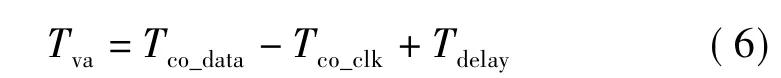

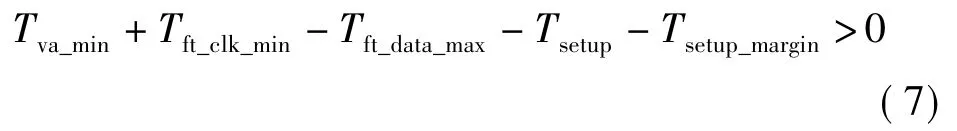

式中,Tco和Tft分别表示数据和同步时钟信号在器件内部延迟和信号传输飞行时间;Tdelay是指数据信号和同步信号之间的延迟。

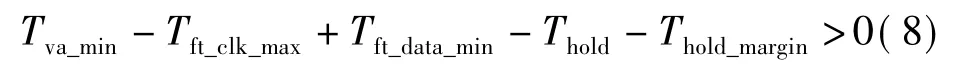

建立时间的冗余量的计算公式为

驱动端的建立时间为

接收端保持时间的冗余量计算公式为

发送端的保持时间计算公式为

值得注意的是,Tva,Tba作为器件的重要指标,可以在器件的 datasheet中查找。由时序图2可知建立时间

保持时间

图3 源同步时序图

4 源同步仿真

在源同步技术中,影响速度的最主要因素是数据和时钟/锁存信号之间的skew,而走线的长度Tco,器件本身的快慢不是影响速度的决定因素。在仿真的过程中要求仿真环境必须灵活适应不同的设计方法,Cadence软件中的SigXp工具提供自定义测量Custom Measurement这一功能,从而可以更好地适应源同步总线设计的使用方法。

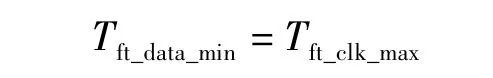

时钟和数据信号是由同一芯片产生,因而两者所处的环境如电压、温度相同,可以认为两者的flight time值的最大、最小值同时发生。由此可知:时钟、数据信号线的飞行时间必须严格相等即

在Cadence中对源同步仿真过程如下:

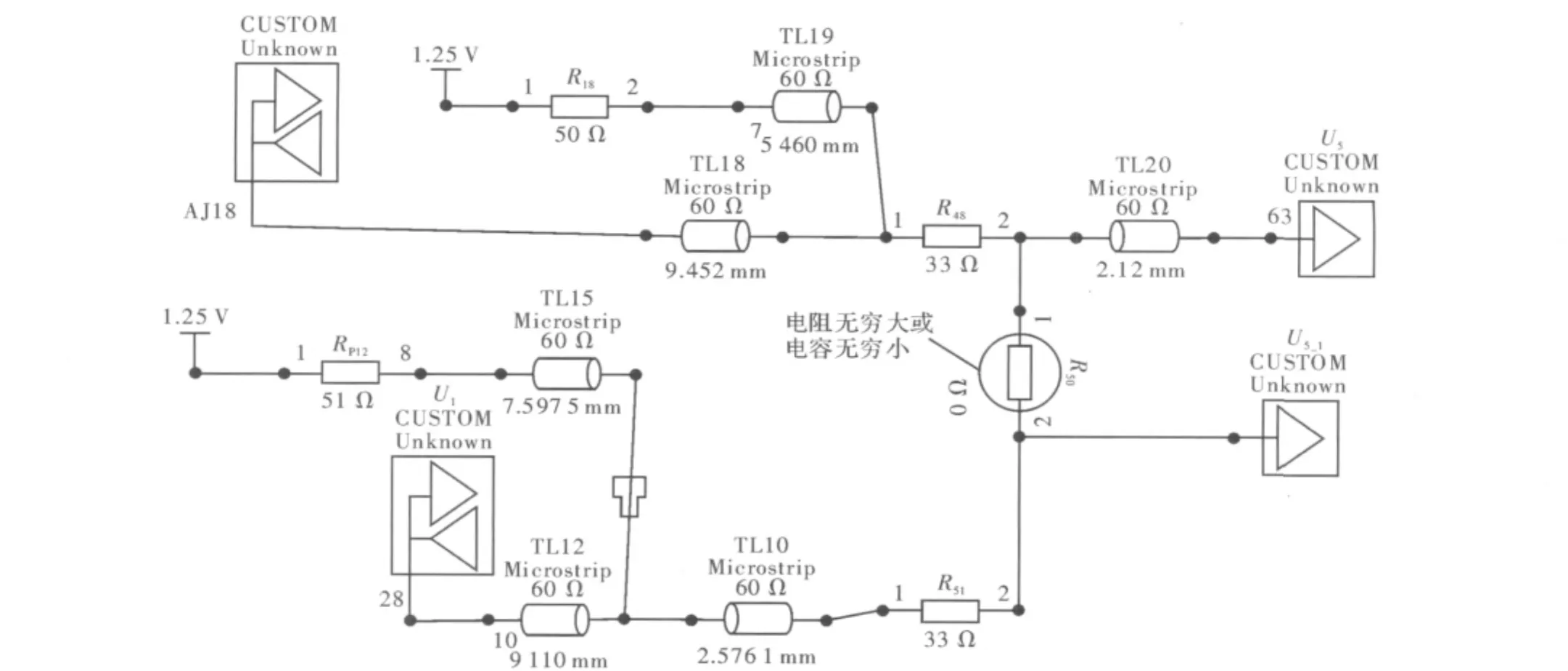

(1)对data信号进行拓扑抽取,抽取成功后将其保存。

(2)对同步时钟信号进行拓扑抽取,抽取成功后将data的拓扑放在同一个界面中。Cadence仿真时是不允许将两个拓扑网络放在一起仿真,这里要测试一下软件,让其认为这两个拓扑是同一个网路的拓扑,执行方式是在菜单中选择“File→Append”命令,之后要用一个很大的电阻(一般是MΩ)或者很小的电容,放在拓扑网路的同一位置,造成电气上的连接关系。

图4 源同步的拓扑结构

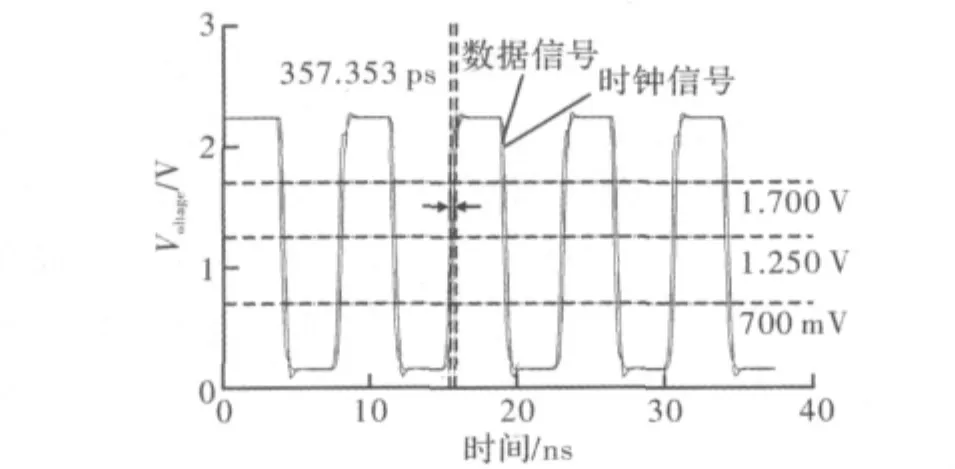

(3)进行仿真,测量并比较仿真结果。图4是拓扑结构调整后的仿真结果,噪声容限和过冲都能满足,同时仿真后可知数据线和时钟线间的延时约在0.3 ns,满足源同步系统设计要求,即数据和同步时钟延迟差在0.5 ns之间。

如果仿真的波形差,有大的过冲和反射,或者延时不满足,就要在SigXplor软件中调整拓扑结构,调整方法有加源端匹配电阻、匹配走线长度、修改拓扑结构,然后重新进行仿真。

图5 源同步时序仿真波形

5 结束语

与普通时钟系统相比,源同步总线在PCB布线的设计比较方便,只要严格保证线长的匹配即可,而不必过多考虑信号线本身的长度。但是,源同步技术一般都会有很高的频率,这样信号的skew更加陡峭,会带来更加复杂的信号完整性方面的问题,所以要综合考虑设计方案,比如对于地址/控制信号采用普通的时钟总线,而高速的数据传输则是采用源同步总线。这些对于高速PCB设计者而言又提出了一个更加严峻的挑战。

[1]邵鹏.高速电路设计与仿真分析:Cadence实例设计详解[M].北京:电子工业出版社,2010.

[2]ERIC B.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2005.

[3]李新,张琳.利用Cadence Allegro进行PCB级的信号完整性仿真[J].现代电子技术,2002,26(6):83 -85.

[4]西安电子科技大学模式识别与控制研究所.IBIS模型简介[M].西安:西安电子科技大学模式识别与控制研究所,2008.

[5]SUDARSHAN D S,RAVISHANKAR K.Signal integrity check by simulation to improve pcb performance[C].Moscow:Proceedings of INCEMIC,2003.