一种S波段噪声干扰激励源设计方法

罗 杰,陈 林

(1.船舶重工集团公司723所,扬州 225001;2.池州学院,池洲 247000)

0 引 言

随着科技的发展,雷达干扰和抗干扰技术就如矛和盾一样,在不断迅速地向前发展着,干扰的样式越来越多,相应的抗干扰样式也越来越多、越来越复杂[1]。现在的电子对抗中,针对雷达设备的干扰手段也变化多端,雷达干扰是用电子方法破坏对方雷达的正常工作,使雷达不能正确探测和跟踪真正的目标。为了提高雷达的抗干扰性能,雷达在生产和使用中都需要采取各种措施来检验雷达的抗干扰能力。基于此,针对雷达的干扰装置也在不断衍生。而作为其中的代表,噪声干扰是一种重要的电子干扰技术,广泛应用于对雷达、通信网络等进行压制性干扰。噪声干扰通常分为瞄准式、阻塞式和扫频式3种类型,噪声波形主要包括直接噪声、噪声调频和噪声调相,噪声波形通常由噪声干扰激励源产生。

本文提出了一种S波段噪声干扰激励源的设计方法,从功能、组成以及工作原理等方面做出了阐述。

1 噪声干扰激励源介绍

噪声干扰激励源作为一种干扰装置,其主要优点是需要了解敌方雷达的信息很少,噪声干扰机不需要详细了解雷达的信号特征和处理信号的环节,只需要知道雷达的工作频率,干扰设备比较简单,对传统雷达目标检测系统的干扰效果好。

噪声干扰的主要缺点是:对于脉冲多普勒(PD)雷达来说,噪声很容易被雷达相干处理,使其不能达到有效干扰的目的;且压制性干扰信号从雷达的主瓣进入时,干扰机的方向易被暴露;同时若雷达采用一些先进技术如超低旁瓣天线、相干旁瓣对消器或旁瓣匿影器等,就会使得噪声干扰相对失效[2]。

1.1 噪声源功能

本文所设计的噪声源,其工作频率为2.7~3.2 GHz,可以产生窄带瞄准噪声、宽带阻塞噪声、扫频噪声等噪声信号,要求噪声分布函数为高斯、均匀等概率分布。

1.2 噪声源实现原理

噪声干扰激励源中噪声的产生可以有很多途径,可以通过噪声管、数字调谐振荡器(DTO)、压控振荡器(VCO)以及直接数字合成器(DDS)等多种方法来实现。采用噪声管来产生噪声,其噪声密度较高,但其工作带宽不够;采用DTO以及VCO来产生噪声,有频率准确度不够、频率随温度漂移等缺点。随着DDS器件的发展和成熟,现今大多采用DDS来产生噪声干扰信号。

本文所介绍的噪声干扰源以DDS为核心,由FPGA通过串口接收外部控制计算机的命令,产生DDS的频率控制字,通过在FPGA中产生噪声数据,从而产生各种干扰信号,其原理如图1所示。

图1 噪声模拟器实现原理图

1.3 主要性能指标

频率范围:2.7~3.2 GHz;瞄准噪声带宽:10 k Hz~50 MHz,步长10 k Hz;阻塞噪声带宽:50~500 MHz,步长50 MHz;扫频噪声带宽:50~500 MHz,步长50 MHz;调制方式:调频、调相;谐波/杂散:优于50 d Bc;输出功率:≥10 d Bm。

2 设计方法

噪声干扰激励源的设计包括时钟电路设计、DDS模块设计、噪声数据产生、DDS+变频电路设计,下面分别进行相应介绍。

2.1 时钟电路的设计

噪声源中噪声产生模块的数模转换(DAC)采样率为2 GHz,采用ADI公司的AD9516时钟芯片为外部时钟源,用于控制DAC的采样频率,以保证系统时钟统一。其控制电路图如图2所示。

由于AD9739的时钟输入是高压差分信号(HVDS)格式,时钟管理器AD9516输出后需经过低压伪发射极耦合逻辑(LVPECL)→HVDS的转换,故选择芯片为ADCLK914。

2.2 DDS模块设计

DDS采用ADI公司的AD9737实现。AD9737的最高转换速率可达2.5 GHz,转换数据位可达14 bit,同时可对高达3.6 GHz的信号进行直接数字频率合成(DDS)。由于噪声源中需要DDS输出的最高频率为800 MHz,故需要在电路中增加平衡变压器设计。AD9739在2 GHz转换输出800 MHz时,其杂散优于50 d Bc。本模拟器设计中需要DDS的输出频率范围为300~800 MHz。

噪声源信号产生主要由AD9739、现场可编程门阵列(FPGA)、可擦除可编程只读存储器(EPROM)等组成。EPROM 用于接收双口随机存储器(RAM)下载所需产生的各种噪声信号数据并存储,根据外部控制信号选择相应的频率数据送FPGA,FPGA将频率数据转换成AD9739所需的格式,以一定时序下载给AD9739芯片。AD9739在FPGA的控制下产生各种需要的噪声信号。

2.3 噪声数据产生

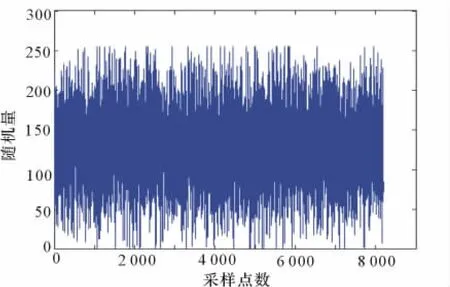

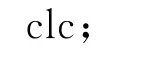

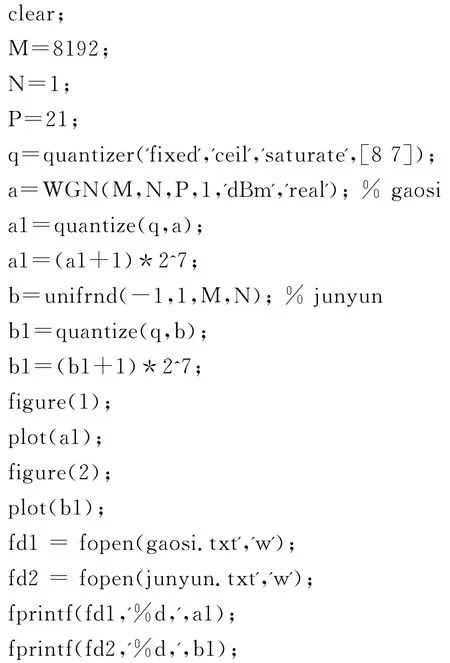

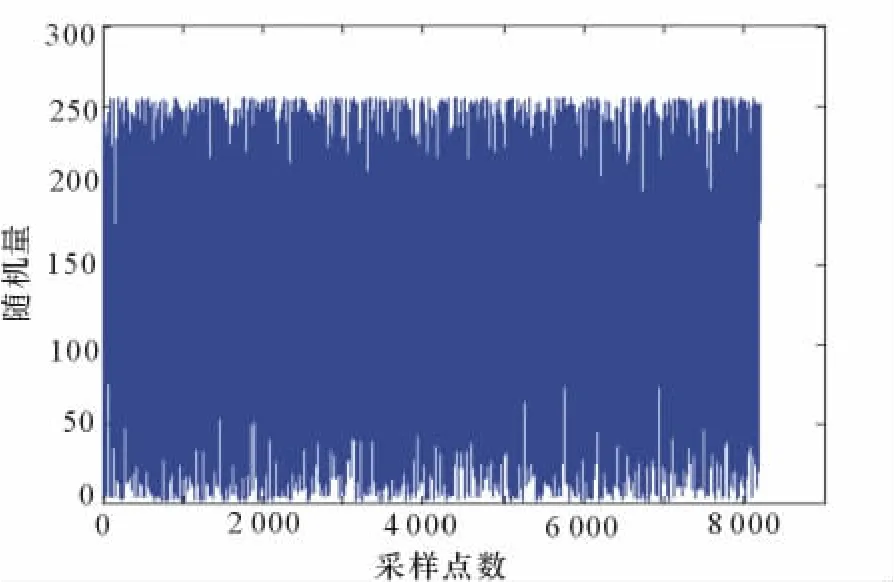

噪声源的函数分布服从高斯和均匀分布,高斯分布和均匀分布的随机噪声数据在MATLAB下产生,生成的数据以文件的方式保存在FPGA软件中,FPGA处理器根据输出的带宽,确定噪声干扰的系数,将随机数写入FPGA中,再实施干扰,其数据仿真结果如图3、图4所示。

图3 均匀噪声数据

产生高斯分布和均匀分布随机噪声数据的程序如下:

图4 高斯噪声数据

2.4 DDS+变频网络的设计

由于最终需要设计的噪声源为S波段,工作频率为2.7~3.2 GHz,而AD9739所产生的信号频率较低,故需要将DDS输出的信号进行变频。变频网络的设计是重要环节,在本方法中选择1次变频完成频率搬移,选择的本振信号频率为3.5 GHz,通过混频产生2.7~3.2 GHz的信号。为了尽量减少混频过程中所产生的交调信号,混频器的选择直接影响噪声源的指标,在此需要选择高IP3的混频器。在选择混频器的时候,应该进行混频分析,针对分析结果选择相应适合的混频器。以本方案为例,本变频方案中,会有1LO-2RF、1LO-3RF等组合分量在2.7~3.2 GHz频带内,所以选择的混频器需要对这些组合分量有很好的抑制,本噪声源的变频网络原理如图5所示。

图5 噪声源变频网络原理图

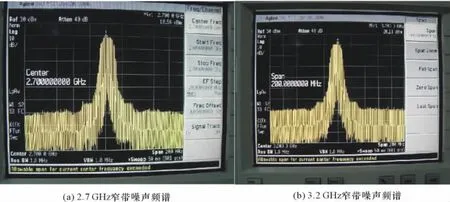

变频网络中带通滤波器完成对带外信号组合分量的抑制,保证信号的杂散指标;放大器主要弥补混频器以及滤波器的插损;后级低通滤波器主要是对放大器输出信号的谐波进行抑制,通过2次滤波,保证信号的杂散水平。噪声源在2.7 GHz,3.2 GHz 2个频点输出的噪声频谱如图6所示,设定的噪声带宽为10 MHz,通过测试,噪声源的信号频谱干净,分布服从高斯分布。

图6 2.7 GHz与3.2 GHz噪声输出频谱图

3 结束语

文章针对S波段噪声源的功能、原理以及设计的主要方法做出了较为详细的阐述、通过本文介绍方法所设计的噪声源已成功用于某型干扰模拟设备,通过对实体雷达进行干扰,干扰效果有效。这种噪声源既可用于雷达和通信干扰设备,也可用于干扰检验电子设备的抗干扰性能。

[1]陈相麟.雷达试验[M].北京:国防工业出版社,2004.

[2]文富忠.一种有效的雷达噪声干扰技术[J].电讯技术,2003(6):47-50.