PVT法掺钒SiC单晶生长电阻率变化规律研究

洪 颖,冯 玢,王 磊,吴 华,郭俊敏,杜 萍

(中国电子科技集团公司第四十六研究所,天津300220)

碳化硅单晶是目前最具有发展前途的宽禁带半导体材料。由于高电阻率的半绝缘碳化硅在高频下有低的介电损耗,使得它在作为基于宽带隙半导体的高温、大功率、高频电子器和传感器的衬底上具有相当大的优势,高质量半绝缘碳化硅(SI-SiC)衬底是高频SiC和GaN基器件的基础[1,2]。

本文采用掺杂的方式,通过掺入深能级杂质钒来补偿SiC单晶生长中所有的浅施主和浅受主能级以实现材料的半绝缘特性。晶片电阻率测试采用的是 COREMA(contactless resistivity mapping)方法,它依据电容驰豫原理,样品被当作漏电介质放置在电容器中,根据测定系统中电量的变化推导得到材料的电阻率。碳化硅单晶片电阻率测试范围为(105~1012)Ω·cm。采用该方法测试晶片电阻率,Mapping结果一目了然,且具有操作便捷,非破坏性、速度快、重复性好等特点。SiC单晶中掺杂剂钒(V)以及杂质元素氮(N)和硼(B)的含量采用二次离子质谱(SIMS)测试,将其结果与COREMA测试结果相结合,研究探讨单晶生长过程中电阻率的变化规律及其原因。

1 实 验

我们在自行研制的SiC单晶炉中,采用PVT(physical vapor translation)法进行2英寸4H-SiC单晶的生长。为降低生长系统中杂质N的掺入,采用高纯的石墨材料做坩埚,高纯碳化硅粉作为源,钒采用固态源方式掺杂,生长在特定的坩埚系统中进行。

将生长后得到的4H-SiC单晶进行定向、滚圆、切参考边后,垂直于单晶生长方向进行多线切割,我们将获得的标准2英寸4H-SiC晶片按单晶生长方向进行统一排序,生长初始记为1#,以此类推,直至生长结束;采用德国Sem iMap公司的COREMA测试仪对晶片的电阻率进行逐一测试,研究探讨单晶生长过程中电阻率的变化规律。

根据COREMA电阻率测试结果,我们适当选取具有代表性的晶片,在其与测试电阻率对应区域进行取样,样片经抛光清洗后对其影响半绝缘性能的掺杂剂V以其主要杂质元素N和B含量进行SIMS测试,以分析探讨单晶生长过程中杂质元素含量与晶片电阻率变化的关系。

2 结果与讨论

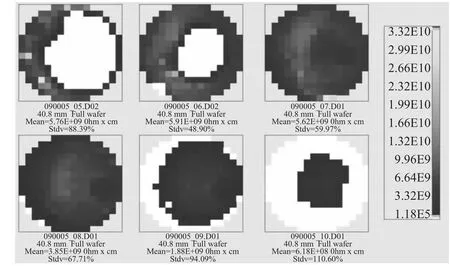

图1为晶体090005,晶片编号为5#~10#的电阻率测试结果,图中白色区域代表电阻率的测试值低于1×105量级,也就是低阻;而其他区域电阻率测试值对应于右侧标识,大约在1×109量级,具有半绝缘性能。从该图中可以清楚地看到在单晶生长过程中晶片电阻率从低阻到高阻,再从高阻到低阻的一个渐变过程,其变化趋势非常一致,具有一定的代表性。

图1 晶片电阻率COREMA测试结果

我们对此展开分析研究,结果发现晶片电阻率的变化趋势宏观上与其晶体表面的形状相对应,从图1来看,晶片表面电阻率优先发生变化的区域是晶片的周边区域,从目前我们生长得到的SiC单晶整体形状来看,中心略突,周边略低;晶片是垂直于单晶生长方向切割而成的,因此同一晶片表面并不是同一时刻生长所得的,晶片电阻率的变化也证实了这一结果,间接反映出单晶实际的生长状态。当单晶生长表面较平时,晶片间的电阻率就不存在渐变的可能,而是存在突变的可能,同一晶片电阻率相差较小,但晶片与晶片间的电阻率可能会相差较大;由此可推断,单晶生长表面较平有利于提高同一晶片电阻率的均匀性。

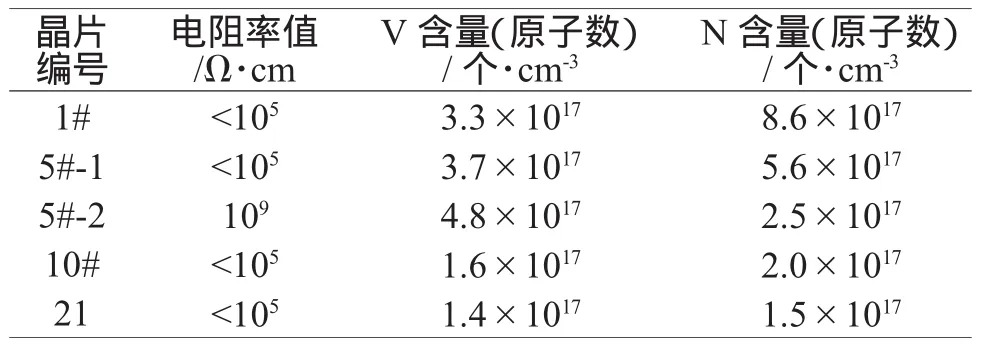

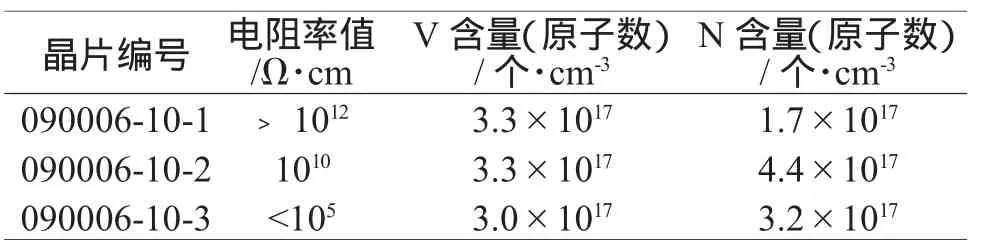

SiC单晶生长过程中电阻率的变化趋势与晶体生长表面宏观形状相关只是一个表观现象,追其根本原因还是与单晶生长过程中每一时刻生长气氛中掺杂剂V以及杂质N和B的含量相关。采用掺V的方法制备半绝缘SiC单晶其根本原理是通过掺入深能级杂质V来补偿单晶生长过程中浅施主N和浅受主B,从而实现材料的半绝缘性能。表1为晶体090005部分晶片电阻率测试值以及晶片中掺杂剂V、杂质N的含量,其中5#晶片分别选取了对应高阻和低阻的两个区域,因为B的测试含量一般在1×1015量级,与V和N的含量相差较大,故浅受主杂质B的影响忽略不计,SiC单晶半绝缘性能只与深能级杂质V和浅施主杂质N相关。

表1 晶体090005部分晶片电阻率测试值以及晶片中掺杂剂V、杂质N的含量

据资料显示,V在SiC单晶中的溶解度为(3~5)×1017,从表1中可以看出其单晶中V的含量已接近溶解度,表1的结果说明当掺杂剂钒的浓度(CV)与杂质氮的浓度(CN)相近,且浓度较高,在1×1017量级时,晶片电阻率存在高阻和低阻相互变化,当CV>CN时,有显示出高阻的可能性,如5#-2,当CV<CN,则基本上一定为低阻。

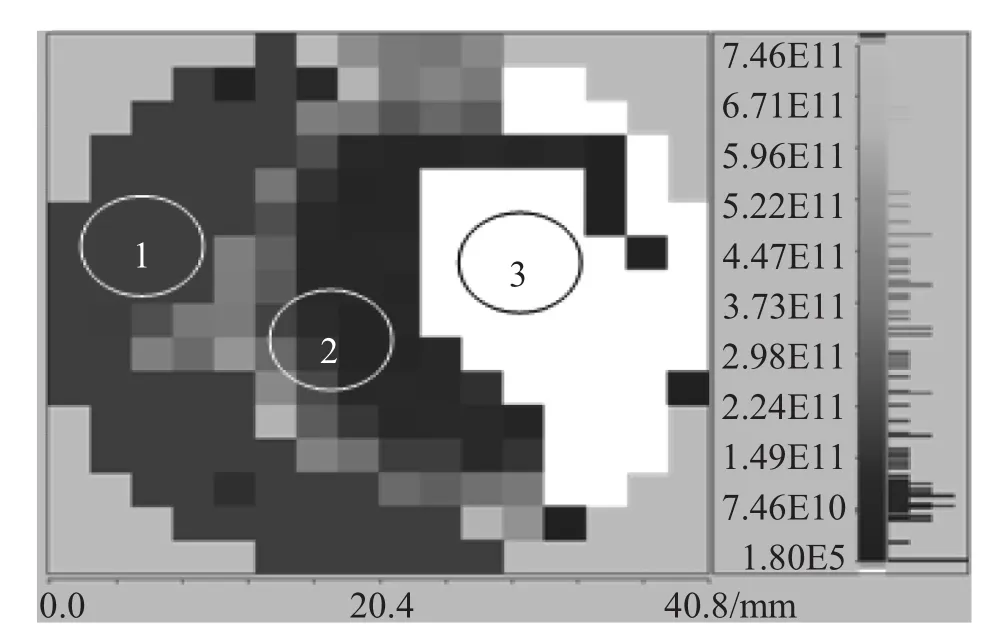

图2同样是我们得到的一个晶片的电阻率测试结果,图中白色区域(3#)同图1,其电阻率的测试值低于1×105量级,而1#区域代表其电阻率的测试值大于1×1012量级,均超过电阻率测试量程。图1是高阻和低阻并存,而图3则是超高阻(>1012量级)和低阻并存,同样在不同的电阻率测试值对应区域取样进行SIMS测试。结果如表2,CV与 CN同样都在 1×1017量级。

图2 晶片090006-10电阻率测试结果

表2 晶片090006-10电阻率测试值以及晶片中掺杂剂V、杂质N的含量

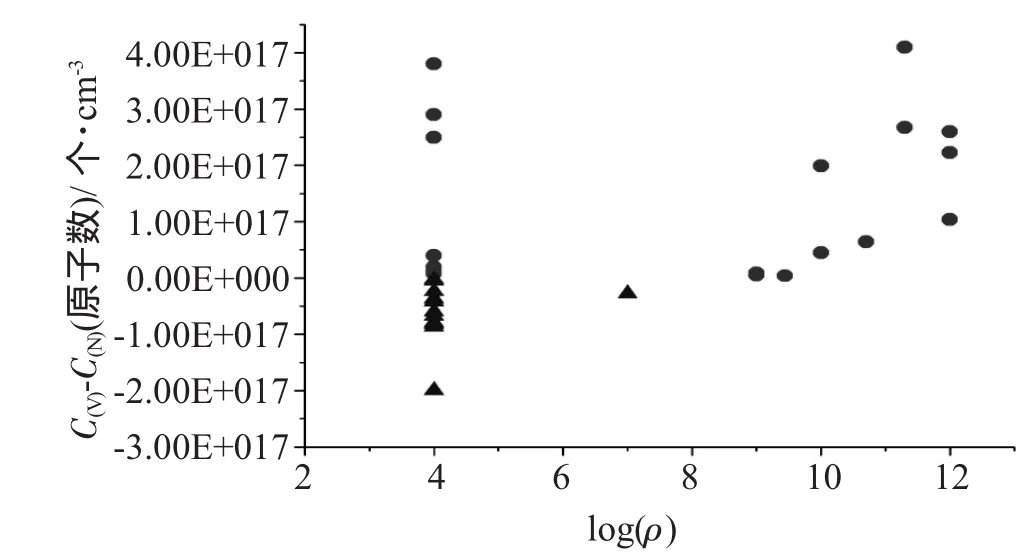

图3为我们统计所测试晶片中CV、CN浓度在1×1017量级左右,晶片的电阻率与其影响电学性能的元素V和N的含量之间的关系,其中横坐标为掺杂剂钒的浓度与杂质氮的浓度之差,纵坐标为利于表征,选取的是晶片电阻率的对数。[举例,电阻率为 ρ=1010Ω·cm,则 log(ρ)=10]。当电阻率测试值<1×105Ω·cm(低阻)时,我们将其定义为1×104Ω·cm;电阻率的测试值大于1×1012量级,我们定义为从1×1012Ω·cm。图中可以看出,当CV<CN时(三角标识),意味着掺入的深能级杂质V未能完全补偿浅受主N,因而材料显示为低阻;而当CV>CN时(圆形标识),从测试结果来看,大部分显示出高阻,且电阻率测试值集中分布在1×109~1×1012量级,但同时有少部分显示出低阻,说明不是所有的V都参与了补偿作用。SiC单晶半绝缘性能的实现与单晶中V和N的含量相关,但其具体的电阻率的大小与V和N的相对含量没有必然的联系。

图3 晶片中杂质元素V和N含量与电阻率测试值的关系

在实验中还发现,当单晶中V和N的含量都降到1×1016量级时,晶片电阻率变化同样复杂,同一晶片不同区域会出现高阻、超高阻(>1012量级)以及低阻共存;这一结果说明当SiC单晶中的杂质浓度较低时,其单晶中本征缺陷所引起的深能级可能会显现出一定的作用,其在补偿材料电性能方面具有与杂质能级相同的效果,不同的是,本征缺陷能级产生原因复杂,稳定性差,更难于控制。

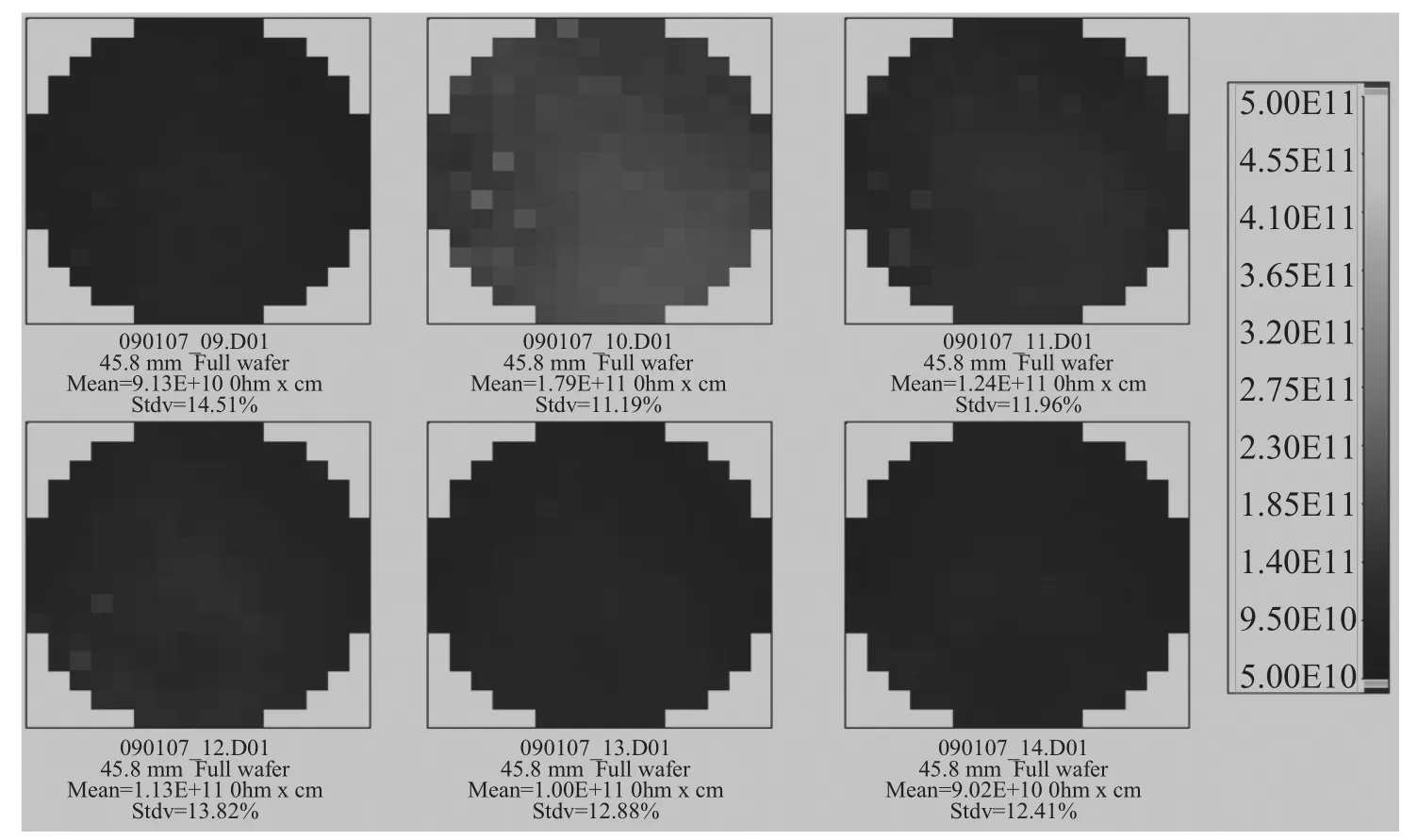

经实验证明在SiC单晶生长过程中只有当V含量在1×1017量级,而N含量在5×1016量级以下时,深能级杂质V完全补偿浅施主N,则可制备得到高阻,其电阻率均匀性好的SiC单晶。图4为我们在该条件下制备得到的电阻率测试值在1×1010量级,且均匀性非常好的半绝缘SiC单晶。

图4 晶片电阻率COREMA测试结果

3 结 论

通过采用掺入深能级杂质钒的方式制备半绝缘SiC单晶,单晶生长过程中电阻率的变化趋势反映出实际单晶生长表面形状,其半绝缘性能的实现与单晶中V、N的含量相关。当晶片中V和N的含量都在1×1017量级时,晶片电阻率变化较为复杂,同一晶片不同区域会出现高阻甚至超高阻与低阻并存,如果CV<CN,则材料一定为低阻;如果CV>CN,则大部分为高阻,电阻率测试值集中分布在1×109~1×1012量级,但电阻率的大小与V和N的相对含量没有必然联系;少部分显示低阻,说明不是所有测试得到的V都参与了补偿作用。

[1]BICKERMANNM,WEINGARTNERR,WINNACKER A,et al.On the preparation of vanadium doped PVT grow th SiC boules with high semi-insulating yield[J].Journal of Crystal Grow th,2003,254(1):390-399.

[2]ZVANUTM E,KONOVALOV V V,WANGHY,etal.Defect levels and types of pointdefects in high-purity and vanadium-doped sem i-insulating 4H-SiC[J].Journal of Applied Physics,2004,96(10):5484-5489.